CMOS 集成逻辑门电路

description

Transcript of CMOS 集成逻辑门电路

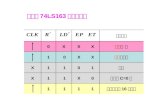

★ CMOS反相器的电压传输特性

★ CMOS反相器的输入输出特性

★ TTL与 CMOS集成电路性能比较

7.1 MOS集成逻辑门

能与大多数的 TTL 逻辑电路兼容。

MOS 集成逻辑门是由 MOS场效应晶体管组成的数字集成电路

MOS 集成逻辑门

在 LSI (大规模集成电路)及 VLSI( 超大规模集成电路 ) 的制作上 已经超过 TTL ,并占据优势。

:制作工艺简单,成本低,

输入阻抗极高, 功耗低, 集成度高

工作电源允许变化范围大,抗干扰性能较好

场效应晶体管是电压控制型器件

与双极性晶体管相比较具有许多优点。

MOS集成逻辑门分

P 沟道增强(称 PMOS ) N 沟道增强(称 NMOS )

和互补 MOS (称 CMOS )三种。PMOS 由于开关速度低,电源电压高而且是负电源,

不便与 TTL 集成逻辑门衔接,现以很少用;

NMOS 克服了 PMOS 的许多问题,但速度低的问题始终

限制了其发展;CMOS 充分表现了 MOS 技术的突出优点,成为LSI 及 VLSI 集成电路的主流产品。

7.2 CMOS反相器的工作原理

1.电路结构

这种由 T1, T2共同组成的互补对称型的场效应管集成电路称为 CMOS反相器。

P 沟道结构的增强型场效应管

N 沟道结构的增强型场效应管

负载管

驱动管

....

vI

T1iD

vo

vssT2

vDD

输入和输出之间为反相关系,实现非门逻辑功能

2.电路工作原理uI=0V时, uGSN=0V,

uGSP= 0V ,

uGSP= -10V

输出 vO 为高电平;uI= 10V 时, uGSN=10V,

输出 vO 为低电平。

0

0

截止

导通

-10

1

10

10

导通

截止

0

0

T2 截止

T1 导通

此时 T2 导通T1 截止 ,

vI

vo

vDD

vSS

T

T2

vI

vo

vDD

vSS

T1

T2

7.3 CMOS传输门和双向模拟开关

CMOS传输门 双向模拟开关

VI/Vo

T1

T2

VDD

C

Vo/VI

C

Vo/VITG

VI/Vo

C

C

1.电路结构

设 T1 管和 T2 管的开启电压 UGS(th)N=UGS(th)P=UGS(th) ,

VDD≥2 UGS(th), 控制信号 C 的高电平为 VDD ,低电平为 0V。

2.工作原理:PMOS管

PMOS管

T1

T2

VDD

C

Vo/VI

C

和 T2 管均处于截止状态相当于电路是断开的。

( 1 )当 0C 0C

0C0C( 2 )当 T1 管和 T2 管均导通,即传输门

导通, uo=uI uI 可以是 0V到 VDD 的任意电压。

结论:当输入信号电压在 0 - VDD 范围内变化时, T1 管和 T2 管至少有一个处于导通状态,输入和输出之间

呈低阻态,相当于开关闭合信号得以传输,且 uo=uI 。

传输门不传输信号。因为 T1 管

7.4 其它类型的 CMOS门电路

由两个串联的 N 沟道和两个并联 P 沟道增强型 MOS管构成

T1 和 T2 两个栅极相连构成又一互补电路,两个互补电路的输入端为与非门的 2 个输入端。

T3 和 T4 两个栅极相连构成互补电路

2 输入端CMOS与非门电路

2 输入端CMOS与非门电路

1.电路结构

Y

T1

T4

T2

T3

B

A

VDD

T1 均截止,输出端 Y 为低电平 0 ,即“全 1出 0”

导通输出端 Y 为高电平 1 ,即“有 0 出 1”

2.逻辑功能

当 A , B 同时为高电平 1 时,T4 , T2 均导通, T3 ,

当 A , B 端有一个或两个为低电平时, 串联 T4 , T2

有一个或两个截止,并联的 T3 , T1 有一个或两个

由两个串联的 P 沟道增强型和两个并联 N 沟道增强型 MOS管构成。

1. 电路组成:

7.5 CMOS或非门

2 输入端CMOS或非门电路

2 输入端CMOS或非门电路

负载管

驱动管

VDD

B

A

T2

T1

T4T3

Y

输入输出之间的逻辑关系为 BAY

2.逻辑功能:

接高电平的驱动管 T3 或 T4

导通,输出端 Y 为低电平 0 ,即“有 1 出 0” 。

输出 Y 为高电平 1 ,即“全 0 出1”

当 A , B 同时为高电平 1 时,

当 A 、 B 端都为低电平 0 时,驱动管 T3 和 T4 两个都截止,

负载管 T1 、 T2 同时导通。

7.6 CMOS模拟开关

1.电路组成:

VDD

ui

V1 V2

V3

V4

uIuO

uo

1

TG

c

当 C=VDD 时,

由此可见,只要适当控制反相器的输入电压,即可决定模拟开关的通断,传输门所能传输的电压值为 0 - VDD

之间任意电压值。又因 MOS管源极和漏极的对称性,所以模拟开关是一种双向开关。

2.工作原理

0C

控制 CMOS传输门导通,使 uo=uI 。

DDVC 当 C=0时,反相器输出控制 CMOS传输门截止,使输入和输入断开。

反相器输出

7.7 TTL与 CMOS集成电路性能比较

不同点:

频率不高情况下,电路的带负载能力比 TTL 集成

电路强

所以 CMOS 集成电路的工作速度比 TTL 集成电路慢。

具有相同逻辑功能的 TTL 集成电路和 CMOS 集成电路相同点:

( 1 ) CMOS 集成电路的输入阻抗很高,可达 108Ω 以上

( 2 ) CMOS 集成电路的导通电阻比 TTL 集成电路的导通 电阻大得多

( 5 )由于 CMOS 集成电路内部电路功耗小,发热量小,

( 3 ) CMOS 集成电路的电源电压范围为 3-18V ,这使它的输

出电压摆幅大,因此其干扰能力比 TTL 集成电路强,

这与严格限制电源电压的 TTL 集成电路要优越的多。( 4 )由于 CMOS 集成电路静态时栅机电流几乎为0 , 因此该电路功耗比 TTL 电路功耗小。

所以 CMOS 集成电路集成度比 TTL 集成电路集成度高。

( 7 )由于 CMOS 集成电路的输入阻抗很高,使其容易 受静电感应而击穿,虽然制作集成电路时在其内 部设置了保护电路,但在存放和使用时应注意静 电屏蔽,焊接时电烙铁应注意良好的接地 , 尤其 是 CMOS 集成电路不用的多于输入端不能悬空,应 根据需要接地或接电源。

( 6 ) CMOS 集成电路的稳定性能好,抗辐射能力强, 可在特殊情况下工作。

TTL 集成电路一般不需要考虑静电感应和屏蔽的问题,不用的多于输入端可以悬空。