第 3 章 逻辑门电路

-

Upload

daria-cruz -

Category

Documents

-

view

154 -

download

5

description

Transcript of 第 3 章 逻辑门电路

第 3章 逻辑门电路

第 3 章 逻辑门电路一、学习目的

逻辑门电路是构成数字电路的基本单元。要从内部结构上认识了解逻辑门电路的基本构造和性能特点,了解逻辑门电路的逻辑关系用分立元件是如何实现的,了解集成门电路的分类和各类集成逻辑门电路的工作特点及主要参数。

二、内容概要

本章首先介绍逻辑门电路的开关特性。在此基础上,简要介绍分立元件与门、或门、非门及与非门、或非门的工作原理和逻辑功能,然后着重讨论 TTL 和 CMOS 集成逻辑门电路的工作原理、逻辑功能和外特性,及它们的改进电路和其它功能的集成逻辑门电路。还介绍 TTL 和 CMOS 电路的使用方法及其功能的测试与应用。而对于各种集成逻辑门的内部电路只作简单介绍。

三、本章重点三极管的开关特性,组合逻辑门电路的逻辑关系, TTL 集成逻辑门电路的类型系列和各自的特点, CMOS 集成逻辑门电路的特点,集成逻辑门电路的应用,掌握 OC 门、三态门的工作特点。

第 3章 逻辑门电路

概述

用以实现各种基本逻辑关系的电子电路称为门电路。它是组成其它功能数字电路的基础。常用的逻辑门电路有与门、或门、非门、与非门、或非门、三态门和异或门等。集成逻辑门主要有双极型的 TTL 门电路和单极型的 CMOS 门电路。其输入和输出信号只有高电平和低电平两种状态。用 1 表示高电平、用 0表示低电平的情况称为正逻辑;反之用 0 表示高电平、用 1 表示低电平的情况称为负逻辑。在本书中,如未加说明,则一律采用正逻辑。

第 3章 逻辑门电路

在数字电路中,只要能明确区分高电平和低电平两个状态就可以了,所以,高电平和低电平都允许有一定的变化范围,如下图所示。

第 3章 逻辑门电路

3.1 3.1 逻辑门电路逻辑门电路

◆ ◆ 逻辑门电路是指能够实现一些基本逻辑关系的电路,简称逻辑门电路是指能够实现一些基本逻辑关系的电路,简称“门电路”或“逻辑元件”。各种门电路均可用半导体分立元“门电路”或“逻辑元件”。各种门电路均可用半导体分立元件或集成电路构成。目前几乎都做成单片集成电路件或集成电路构成。目前几乎都做成单片集成电路

◆ ◆ 基本门电路是指能够实现三种基本逻辑功能关系的电路,基本门电路是指能够实现三种基本逻辑功能关系的电路,即即与门、或门、非门与门、或门、非门((又称又称反相器反相器)。)。

◆ ◆ 逻辑门电路的描述有以下逻辑门电路的描述有以下 4 4 种方方式:种方方式:真值表真值表、、逻辑表达逻辑表达式式、、逻辑图逻辑图和和波形图波形图。。这这 44 种描述方法都能反映逻辑门电路输种描述方法都能反映逻辑门电路输入和输出变量间的逻辑关系。其实这入和输出变量间的逻辑关系。其实这 44 种描述方法是等价的,种描述方法是等价的,各有其特点且可以相互转换。在逻辑电路的分析和设计过程中各有其特点且可以相互转换。在逻辑电路的分析和设计过程中可根据实际情况灵活选择不同的描述方式。可根据实际情况灵活选择不同的描述方式。

第 3章 逻辑门电路3.1.1 3.1.1 非门非门定义:定义:输入与输出信号状态满足“非”逻辑关系。输入与输出信号状态满足“非”逻辑关系。 非门电路非门电路:: 逻辑符号逻辑符号:: 非门波形图非门波形图::

非门工作特点非门工作特点::

●● 当输入端为低电平当输入端为低电平 00 (( 0V0V )时,晶体管截止,晶体管集电极)时,晶体管截止,晶体管集电极—发射极间呈高阻状态,输出端—发射极间呈高阻状态,输出端 LL 的电压近似等于电源电压;的电压近似等于电源电压;

●● 任何能够实现 “非”逻辑关系的电路均称为“非门”,任何能够实现 “非”逻辑关系的电路均称为“非门”, 也称为反相器。式中的符号“ 也称为反相器。式中的符号“ -”-” 表示取反,在其逻辑符号的输出表示取反,在其逻辑符号的输出端用一个小圆圈来表示。端用一个小圆圈来表示。

AL

●● 当输入端当输入端 A A 为高电平为高电平 11 (( +5V+5V )时,晶)时,晶体管导通,体管导通, L L 端输出端输出 0.20.2 ~~ 0.3V0.3V 的电压,属于的电压,属于低电平范围;低电平范围;

第 3章 逻辑门电路3.1.2 3.1.2 与门与门定义:定义:输入与输出信号状态满足“与”逻辑关系。输入与输出信号状态满足“与”逻辑关系。 与门电路:与门电路: 逻辑符号:逻辑符号: 与门波形图:与门波形图:

与门工作特点:与门工作特点:

● 当 AA 、 BB 中的任何一端为低电平“ 0” ( 0V )或 AA 、 BB 端同时为低电平“ 0” 时,二极管 D1 、 D2 的导通使输出端 LL 为低电平“ 0” ( 0.7V )。

●● 如图所示为双输入单输出如图所示为双输入单输出 DTLDTL 与门电路及与门逻辑符号。与门电路及与门逻辑符号。当输入端当输入端 AA 与与 BB 同时为高电平“同时为高电平“ 1”1” (( +5V+5V )时,二极管)时,二极管 DD11 、、 DD

22 均截止,均截止, R R 中没有电流,其上的电压降为中没有电流,其上的电压降为 0V0V ,输出端,输出端 LL 为高为高电平“电平“ 1”1” (( +5V+5V ););

● 任何能够实现 L=A·B “ 与”逻辑关系的电路均称为“与门”。

第 3章 逻辑门电路

3.1.3 3.1.3 或门或门定义:定义:输入与输出信号状态满足“或”逻辑关系。输入与输出信号状态满足“或”逻辑关系。 或门电路或门电路:: 逻辑符号逻辑符号:: 或门波形图或门波形图::

或门工作特点或门工作特点::

● 当 AA 、 B B 端同时为低电平“ 0” ( 0V )时,输出端 LL 一定一定为低电平 0 。

●● 如图所示为双输入单输出如图所示为双输入单输出 DTLDTL 或门电路及或门逻辑符号。或门电路及或门逻辑符号。当输入端当输入端 AA 或或 BB 中的任一端为高电平“中的任一端为高电平“ 1”1” (( +5V+5V )时,输出端)时,输出端LL 一定为高电平“一定为高电平“ 1”1” (( +4.3V+4.3V );输入端);输入端 AA 和和 BB 均为高电平时,均为高电平时,输出端也为高电平。输出端也为高电平。

● 任何能够实现 L=A+B “ 或”逻辑关系的电路均称为“或门”。

第 3章 逻辑门电路3.1.4 3.1.4 其他常见门电路其他常见门电路1. 1. 与非门与非门

与非门电路与非门电路:: 逻辑符号逻辑符号::

与非门波形图与非门波形图::

与非门工作特点与非门工作特点::● ● 当输入端当输入端 AA 和和 BB 同时为高电平(同时为高电平( +5V+5V )时,所接二极管)时,所接二极管 DD11

和和 DD22 截止,晶体管截止,晶体管 TT11 、、 TT22 均导通,输出端均导通,输出端 LL 为低电平为低电平 00 (( +0.3+0.3

VV )。可见,只要输入端中的任意一端为低电平时,输出端就一)。可见,只要输入端中的任意一端为低电平时,输出端就一定为高电平,定为高电平,只有当输入端均为高电平时,输出端才为低电平,只有当输入端均为高电平时,输出端才为低电平,既输入与输出信号状态满足“与非”逻辑关系。既输入与输出信号状态满足“与非”逻辑关系。

●● 如图所示为双输入单输出如图所示为双输入单输出 TTLTTL 与非门电路及其逻辑符号。与非门电路及其逻辑符号。当输入端当输入端 AA 或或 BB 中的任何一端为低电平中的任何一端为低电平 00 (( 0V0V )时,所接二极)时,所接二极管管 DD11 或或 DD22 导通,晶体管导通,晶体管 TT11 的基极电压为的基极电压为 0.7V0.7V (小于(小于 2.1V2.1V ),),晶体管晶体管 TT11 截止,晶体管截止,晶体管 TT22 也截止,输出端也截止,输出端 LL 为高电平(为高电平( +5V+5V ););当输入端同时为低电平当输入端同时为低电平 00 (( 0V0V )时,输出端同样也为高电平()时,输出端同样也为高电平( ++5V5V )。)。 ● 任何能够满足“与非”逻辑关系的电路均称为“与非门”。

BAL 逻辑关系式逻辑关系式::

提

示提

示

◆ ◆ 常用门电路也可以由基本门电路“非门”、“与门”、常用门电路也可以由基本门电路“非门”、“与门”、“或门”间接构成。例如:“或门”间接构成。例如:

◆ ◆ 通常我们将由逻辑符号表示的逻辑电路称为“逻辑通常我们将由逻辑符号表示的逻辑电路称为“逻辑图”图”。。

第 3章 逻辑门电路

2. 2. 或非或非门 门

或非门电路或非门电路::逻辑符号逻辑符号::

或非门波形图或非门波形图::

◆◆ 能够实现 “或非”逻辑关系的电路均称为能够实现 “或非”逻辑关系的电路均称为“或非门”。在一个或门的输出端连接一个非门就构成“或非门”。在一个或门的输出端连接一个非门就构成了“或非门”,如下图所示。了“或非门”,如下图所示。

BAL

第 3章 逻辑门电路

3. 3. 异或异或门 门

异或门电路异或门电路:: 逻辑符号逻辑符号::

双输入端异或门波形图双输入端异或门波形图::

◆◆ 能够实现 “异或”逻辑关系的能够实现 “异或”逻辑关系的电路均称为“异或门”。电路均称为“异或门”。异或门可由非门、与门和或门异或门可由非门、与门和或门组合而成组合而成,如下图所示。,如下图所示。

BABABAL

提 示提 示 当输入端当输入端 AA 、、 B B 的电的电平状态互为相反时,输出端平状态互为相反时,输出端LL 一定为高电平;当输入端一定为高电平;当输入端AA 、、 BB 的电平状态相同时输的电平状态相同时输出出 LL 一定为低电平。一定为低电平。

第 3章 逻辑门电路4. 4. 同或同或门 门

同或门电路同或门电路:: 逻辑符号逻辑符号::

双输入端同或门波形图双输入端同或门波形图::

提 示提 示

当输入端当输入端 AA 、、 B B 的电的电平状态互为相反时,输出端平状态互为相反时,输出端LL 一定为低电平;而当输入一定为低电平;而当输入端端 AA 、、 B B 的电平状态相同的电平状态相同时,输出端 时,输出端 L L 一定为高电一定为高电平。平。

◆◆ 能够实现 能够实现 AA⊙⊙BB “ “ 同或”逻辑关系的电同或”逻辑关系的电路均称为“同或门”。由非门、与门和或门组合而成的同或门及逻路均称为“同或门”。由非门、与门和或门组合而成的同或门及逻辑符号如下图所示。辑符号如下图所示。

BABAL

第 3章 逻辑门电路

3.2 3.2 不同系列门电路不同系列门电路

目前使用的门电路大多为集成门电路,目前使用的门电路大多为集成门电路,最常用的是最常用的是 TTLTTL 系列和系列和 CMOSCMOS 系列。在系列。在两种不同系列的门电路中,他们虽具有相两种不同系列的门电路中,他们虽具有相同的逻辑功能而两者的结构、制造工艺却同的逻辑功能而两者的结构、制造工艺却不同,其外形尺寸、性能指标也有所差别。不同,其外形尺寸、性能指标也有所差别。

因此有必要了解两种不同系列门电路因此有必要了解两种不同系列门电路的结构特点、工作原理及主要特性,以便的结构特点、工作原理及主要特性,以便在实际设计中合理选择芯片。在实际设计中合理选择芯片。

第 3章 逻辑门电路

3.2.1 TTL3.2.1 TTL 系列门电路系列门电路◆◆ TTLTTL (晶体管—晶体管逻辑)门电路只制成单片集成电路。(晶体管—晶体管逻辑)门电路只制成单片集成电路。输入级由多发射极晶体管构成,输出级由推挽电路(功率输出输入级由多发射极晶体管构成,输出级由推挽电路(功率输出电路)构成。标准电路)构成。标准 TTLTTL 与非门如下图所示。与非门如下图所示。

◆ ◆ 标准标准 TTLTTL 与非门与非门 ◆ ◆ 电路工作原理电路工作原理1.1. 电路组成电路组成2. 2. 逻辑关系逻辑关系

当一个发射极或当一个发射极或 33 个发个发射极都接低电平(射极都接低电平( AA 、、 BB 、、CC 接地),多发射极晶体管接地),多发射极晶体管TT11 一定工作在饱和导通状态,一定工作在饱和导通状态,其集电极电压其集电极电压 UUB2B2≈0.2V≈0.2V ,晶,晶体管体管 TT22 必定截止,使必定截止,使 TT33 饱饱和导通,而和导通,而 TT44 截止,输出端截止,输出端L L 为高电平。为高电平。

当当 33 个发射极都接高电个发射极都接高电平(平( AA 、、 BB 、、 CC 都接都接 +5+5VV )时,)时, TT11 的集电结处于正的集电结处于正向偏置而导通(向偏置而导通(倒置工作状倒置工作状态态 )至使)至使 TT22 、、 TT44 饱和导通,饱和导通,则有则有

UUB4B4≈0.7V≈0.7V ,, UUCES2CES2≈0.2V≈0.2V

UUB3B3≈0.9V≈0.9V ,, TT33 截止,截止, UULL≈0≈0

第 3章 逻辑门电路

3 . TTL与非门的主要参数(1) 工作速度 :

为了提高开关速度,电路采用了抗饱和三极管和有源泄放电路。 抗饱和三极管 :三极管饱和越深,其工作速度越慢。因此,要提高电路的工作速度,就必须设法使三极管工作在浅饱和状态。

(2) 电压传输特性和噪声容限 :

当 0<ui<0.8V时, V2和 V5截止, V2集电极电压 uC2为高电平, V3和 V4导通,输出 u0为高电平,如图 AB段所示。这时与非门工作在截止区。

当 0.8V<ui<1.1V 时, V2和 V5同时工作在放大区,输入电压 uI 的微小增大,会引起输出电压 uO的急剧下降,如图 BC 段所示。这时与非门工作在转折区,又称过渡区。

当 uI>1.1时, V2和 V5 饱和导通,输出电压 uO为低电平 ,它不再随输入 uI的增加而变化,如图 CD 段所示。这时与非门工作在饱和区。

第 3章 逻辑门电路

关门电平 : 在保证输出为标准高电平时,允许输入低电平的最大值称为关门电平,用 UOFF表示。 UOFF≈1.0V。

开门电平 : 在保证输出为标准低电平时,允许输入高电平的最小值称为开门电平,用 UON表示。 UON≈1.2V。

阈值电压 : 工作在电压传输特性转折区中点对应的输入电压称为阈值电压,又称门槛电平,用 UTH表示。

第 3章 逻辑门电路

输入噪声容限 : 当输入低电平信号上叠加了正向噪声(干扰)电压而上升时,只要不大于关门电平,输出的高电平不会小于标准高电平。同样,当输入的高电平信号上叠加了负向噪声(干扰)电压而下降时,只要不小于开门电平,则输出的低电平也不会立刻上升。在输入信号上叠加的噪声电压只要不超过允许值,就不会影响电路的正常逻辑功能,这个允许值称为噪声容限。电路的噪声容限越大,其抗干扰能力就越 强。

4 .输入负载特性:

在实际工作中,经常会遇到在门电路输入端与地之间接入一个电阻 R1的情况,等效电路如图所示。当 uI上升到 1.1时, V1的基极电压被钳位在 1.8V上, V2和 V5导通,输出 uO为低电平 UOL,此后, uI不再随R1的增大而升高。 uI 随 R1变化的曲线如图所示。

第 3章 逻辑门电路5 .输出负载特性:

带灌电流负载特性 :与非门输出 uO为低电平时,带灌电流负载。当输入都为高电平时,与非门的 V2、 V5 饱和导通,输出 uO为低电平 UOL,这时,各个外接负载门的输入低电平电流都流入(即灌入) V5的集电极,形成了输出低电平电流。当外接负载门的个数增加时,流入 V5集电极的电流随之增大,输出低电平稍有上升,只要不超过输出低电平允许的上限值,与非门的正常逻辑功能就不会被破坏。设与非门输出低电平时,允许 V5 最大集电极电流为I OL(max),每个负载门输入低电平电流为I IL时,则输出端外接灌电流负载门的个数 NOL为。NOL= IOL(max) /IIL

第 3章 逻辑门电路

带拉电流负载特性:当输入有低电平时, V5截止、 V4导通,输出uO为高电平 UOH。这时,与非门输出高电平电流从输出端流向各个外接负载门。当外接负载门的个数增多时,被拉出的电流增大,与非门输出的高电平随之下降,只要不超过允许的高电平下限值 UOH(min),与非门的正常逻辑功能就不会被破坏。设与非门输出高电平允许的最大电流为 IOH(max),每个负载门输入高电平电流为 IIH,则输出端外接拉电流负载门的个数 NOH为。 NOH= IOH( max ) /IIH

第 3章 逻辑门电路6 .传输延迟时间:

在 TTL与非门中,由于 器件内部的原因,当输入电压 UI 为一个矩形脉冲时,输出电压 UO的脉冲波形比输入波形延迟了一定的时间。输出电压 UO的波形滞后于输入电压 UI 波形的时间称作传输延迟时间。从输入电压 UI波形上升沿 0.5UIm 到输出电压下降沿 0.5UOm之间的时间,称作导通延迟时间,用 tPHL表示。从输入电压 UI 下降沿 0.5UIm处到输出电压 UO上升沿 0.5UOm之间的时间称作截止延迟时间,用 tPLH表示。平均延迟时间 tpd 为 tPHL 和 tPLH 的平均值。 tpd=(tPHL+tPLH)/2

第 3章 逻辑门电路◆ ◆ 小 结小 结

(( 44 )多发射极晶体管始终有基极电流流)多发射极晶体管始终有基极电流流过。在正向状态下,基极电流流向一个或过。在正向状态下,基极电流流向一个或几个处于低电平的输入端;在反向状态下,几个处于低电平的输入端;在反向状态下,基极电流流向晶体管基极电流流向晶体管 TT22 的基极。即基区的基极。即基区载流子(电荷)在工作状态转换时无需排载流子(电荷)在工作状态转换时无需排空,省去了排空所需时间,使晶体管从一空,省去了排空所需时间,使晶体管从一种状态转换到另一种状态非常迅速。因此,种状态转换到另一种状态非常迅速。因此,TTLTTL 系列门电路的工作速度比其他系列门系列门电路的工作速度比其他系列门电路要快。电路要快。

(( 11 )输入信号与输出信号符合)输入信号与输出信号符合与非与非逻辑关系。逻辑关系。(( 22 ))拉电流与灌电流拉电流与灌电流:输出为高电平时,向负载输出的电流为拉电流;:输出为高电平时,向负载输出的电流为拉电流;

输出端输出端 LL 为低电平时,负载电流流入输出端为低电平时,负载电流流入输出端 LL并经并经 TT44 流向地端,称此为灌电流。流向地端,称此为灌电流。

(( 33 )若某一输入端悬空,无论其他输入端接高电平或是低电平,)若某一输入端悬空,无论其他输入端接高电平或是低电平,悬空端的悬空端的作用相当于接高电平。作用相当于接高电平。

◆ ◆ 提 示提 示

1.1.若输出端若输出端 LL 所接的负载较重(即负载从输出端汲取的控所接的负载较重(即负载从输出端汲取的控制电流较大),输出的高电平经电阻制电流较大),输出的高电平经电阻 RR44 后会略有下降。后会略有下降。

2.2. 在实际应用中,为避免引入干扰不用的输入端一般不允在实际应用中,为避免引入干扰不用的输入端一般不允许悬空。许悬空。

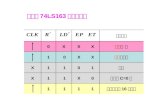

3.3. 下图是下图是 TTLTTL 与非门与非门 74LS0074LS00 集成电路示意图。它包括集成电路示意图。它包括 44个双输入与非门,此类电路多数采用双列直插式封装。个双输入与非门,此类电路多数采用双列直插式封装。在封装表面上都有一个小豁口,用来标识管脚的排列顺在封装表面上都有一个小豁口,用来标识管脚的排列顺序。如果豁口方向朝左,管脚顺序是按逆时针顺序排列序。如果豁口方向朝左,管脚顺序是按逆时针顺序排列的。的。

第 3章 逻辑门电路3.2.2 MOS3.2.2 MOS 系列门电路系列门电路◆ ◆ 特点特点▲ ▲ MOSMOS 系列门电路是采用系列门电路是采用 MOSMOS (( Metal Oxide SemiconductoMetal Oxide Semiconductorr金属氧化物半导体)场效应晶体管制作。金属氧化物半导体)场效应晶体管制作。

▲ ▲ MOSMOS场效应晶体管几乎不需要驱动功率。这种系列的门电路场效应晶体管几乎不需要驱动功率。这种系列的门电路(或开关电路)体积小且制造简单,可以制成高封装密度的集成(或开关电路)体积小且制造简单,可以制成高封装密度的集成电路。电路。

▲ ▲ 由于场效应晶体管的电容作用,开关时间较长,使电路的工由于场效应晶体管的电容作用,开关时间较长,使电路的工作速度较慢。作速度较慢。◆ ◆ 类型类型▲ ▲ PMOSPMOS 电路:用电路:用 P P 沟道耗尽型沟道耗尽型 MOS MOS 场效应晶体管作为电路元件,则称为场效应晶体管作为电路元件,则称为PMOS PMOS ;;

▲ ▲ NMOSNMOS 电路:采用电路:采用 N N 沟道耗尽型沟道耗尽型 MOSMOS 场效应晶体管作为电路元件,称为场效应晶体管作为电路元件,称为NMOS NMOS ;;

▲ ▲ CMOSCMOS 电路:既采用电路:既采用 P P 沟道耗尽型沟道耗尽型 MOSMOS 场效应晶体管又采用场效应晶体管又采用 N N 沟道耗尽沟道耗尽型型 MOSMOS 场效应晶体管,构成互补对称电路,则称为场效应晶体管,构成互补对称电路,则称为 CMOS CMOS 。。

第 3章 逻辑门电路

◆ ◆ CMOSCMOS 门电路举例门电路举例▲ ▲ CMOSCMOS 非门电路非门电路 ▲ ▲ CMOSCMOS 与非门与非门 ▲ ▲ CMOSCMOS 或非门或非门

工作原理工作原理

AA 为高电平,为高电平, TT11

截止截止 TT22 导通,导通, LL 为为低电平,符合非逻低电平,符合非逻辑关系。辑关系。

工作原理工作原理

AA 、 、 BB 同为高电平同为高电平时时 TT1 1 、、 TT22 截止, 截止, TT3 3

、、 TT44 导通,导通, LL 为低电为低电平,符合与非逻辑关平,符合与非逻辑关系。反之亦然。系。反之亦然。

工作原理工作原理

请自行分析请自行分析

2-2