第二章 基本逻辑运算及集成逻辑门

-

Upload

philantha-carlyn -

Category

Documents

-

view

172 -

download

2

description

Transcript of 第二章 基本逻辑运算及集成逻辑门

时序电路的分析 计算机科学系 刘敏钰教授 1 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 1

第二章 基本逻辑运算及集成逻辑门 【教学目标】 1. 掌握基本逻辑和复合逻辑的逻辑关系以及它们的逻辑符号; 2. 理解 TTL 与非门和 CMOS 非门的电路结构和它们的工作原理,理解 TTL 与非门的主要参数的意义; 3. 熟悉 TTL 与非门和 CMOS 非门主要的衍生门电路,特别是或非门、 三态门的逻辑功能; 4. 熟悉 TTL 和 CMOS 门电路的区别和使用注意事项。【教学重点】 TTL 与非门和 CMOS 非门的工作原理; TTL 与非门的主要参数与 TTL

与非门电路之间的关系。【教学难点】 TTL 与非门电路的工作原理。【内容提要】 2.1 基本逻辑运算 2.2 常用复合逻辑 2.3 逻辑赋值和逻辑运算优先权 2.4 集成逻辑门 TTL 与非门和 CMOS 门、集成逻辑门的使用

时序电路的分析 计算机科学系 刘敏钰教授 2 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 2

2.1 基本逻辑运算 逻辑运算是逻辑思维和逻辑推理的数学描述。 具有“真”与“假”两种可能,并且可以判定其“真”、“假”的陈述语句叫逻辑变量。一般用英文大写字母 A 、 B 、 C 、 …表示。例如:“开关 A 闭合着”、“电灯 F 亮着”、 “开关 D 开路着”等均为逻辑变量,可分别将其记作 A , F , D ; “开关 B 不太灵活”、 “电灯 L 价格很贵”等均不是逻辑变量。 逻辑变量只有“真”、“假”两种可能,在逻辑数学中,把“真”、 “假”称为逻辑变量的取值,简称逻辑值,也叫逻辑常量。通常用“ 1” 表示“真”,用“ 0” 表示“假”,或者相反。本教材中,若不作特别说明,“ 1” 就代表“真”,“ 0” 就代表“假”。 虽然“ 1” 和“ 0” 叫逻辑值或逻辑常量,但是它们没有“大小”的含义,也无数量的概念。它们只是代表逻辑“真”、“假”的两个形式符号。

时序电路的分析 计算机科学系 刘敏钰教授 3 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 3

一个结论成立与否,取决于与其相关的前提条件是否成立。结论与前提条件之间的因果关系叫逻辑函数。通常记作:

F=f(A, B, C, …)

逻辑函数 F 也是一个逻辑变量,叫做因变量或输出变量。 因此它们也只有“ 1” 和“ 0” 两种取值,相对地把 A 、 B 、 C 、…叫做自变量或输入变量。

时序电路的分析 计算机科学系 刘敏钰教授 4 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 4

一、与逻辑 ( 与运算、 逻辑乘 ) 决定某一结论的所有条件同时成立,结论才成立,这种因果关系叫与逻辑,也叫与运算或叫逻辑乘。 【例】描述图 2-1 所示电路的功能。

A

F

B

E

【 解 】 根 据 左 图 , 描 述 其 功 能 为 :“开关 A 闭合,并且开关 B 闭合,则电灯 F 亮”。状态表见 2-1(a) 这三个陈述语句均具有“真”、 “假”两种可能 , 其对应关系如表 2-1(b) 所示。图 2-1 与门逻辑电路实例图

时序电路的分析 计算机科学系 刘敏钰教授 5 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 5

表 2-1 与逻辑的真值表

若用“ 1” 代表逻辑“真”,用“ 0” 代表逻辑“假”,则表2-1(b) 可改为表 2-1(c) 的形式。这种表格叫真值表。 所谓真值表,就是将输入变量的所有可能的取值组合对应的输出变量的值一一列出来的表格 , 是描述逻辑功能的一种重要形式。

a 状态表 b 逻辑关系表 c 真值表

A B F A B F A B F

断开 断开 灭 假 假 假 0 0 0

断开 闭合 灭 假 真 假 0 1 0

闭合 断开 灭 真 假 假 1 0 0

闭合 闭合 亮 真 真 真 1 1 1

时序电路的分析 计算机科学系 刘敏钰教授 6 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 6

由表 2-1 可知,上述三个语句之间的因果关系属于与逻辑。 其逻辑表达式 ( 也叫逻辑函数式 ) 为:

F=A·B

读 作 “ F 等 于 A 乘 B” 。 在 不 致 于 混 淆 的 情 况 下 , 可 以 把 符 号“ ·” 省掉。在有些文献中,也采用∩、∧、 & 等符号来表示逻辑乘。

由表 2-1 的真值表可知,逻辑乘的基本运算规则为:

0·0=0 0·1=0 1·0=0 1·1=1

0·A=0 1·A=A A·A=A

时序电路的分析 计算机科学系 刘敏钰教授 7 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 7

实现“与运算”的电路叫与门,其逻辑符号如图 2-2 所示, 其中图 (a) 是我国常用的传统符号,图 (b) 为国外流行符号,图(c) 为国家标准符号。

(a )

FA

B

(b )

FAB

(c )

& FA

B

图 2-2 与门的逻辑符号

时序电路的分析 计算机科学系 刘敏钰教授 8 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 8

二、 或逻辑 ( 或运算、逻辑加 ) 决定某一结论的所有条件中, 只要有一个成立, 则结论就成立,这种因果关系叫或逻辑。 【例】描述图 2-3 所示电路的功能。

图 2-3 或逻辑电路实例图

【解】根据左图,描述如下:“开关 A 断开,开关 B 也断开,则电灯 F 熄灭”。显然这三个语句都是逻辑变量,分别记作 A , B , F 。其真值表如表 2-2 所示。 由表 2-2 可知,上述三个语句之间的因果关系属于或逻辑。 其逻辑表达式为: F=A+B

读作“ F 等于 A 加 B” 。有些文献也采用∪、∨等符号来表示逻辑加。

时序电路的分析 计算机科学系 刘敏钰教授 9 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 9

由表 2-2 的真值表可知,逻辑加的运算规则为:

0+0=0 0+1=1 1+0=1 1+1=1

0+A=A 1+A=1 A+A=A

实现“或运算”的电路叫或门,其逻辑符号如图 2-4 所示。 表 2-2 或逻辑的真值表

a 状态表 b 真值表A B F A B F

断开 断开 灭 0 0 0

断开 闭合 亮 0 1 1

闭合 断开 亮 1 0 1

闭合 闭合 亮 1 1 1

时序电路的分析 计算机科学系 刘敏钰教授 10 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 10

£« FA

B

FA

B

¡Ý1

FAB(b )

(c )

(a )

图 2-4 或门的逻辑符号

时序电路的分析 计算机科学系 刘敏钰教授 11 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 11

三、非逻辑 ( 非运算, 逻辑反 )

若前提条件为“真”,则结论为“假”;若前提条件为“假”,则结论为“真”。即结论是对前提条件的否定, 这种因果关系叫非逻辑。

【例】描述图 2-5 所示电路的功能。

【解】根据左图,描述如下:“若开关 A闭合,则电灯 F 就亮”。 把以上两个陈述句分别记作 A 、 F ,则其真值表如表 2-3 所示。

FA

R

E

图 2-5 非门逻辑电路实例图

时序电路的分析 计算机科学系 刘敏钰教授 12 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 12

表 2-3 非逻辑的真值表

a 状态表 b 真值表

A F A F

断开 亮 0 1

闭合 灭 1 0

由表 2-3 的真值表可知,上述两个语句之间的因果关系属于非逻辑,也叫非运算或者叫逻辑反。其逻辑表达式为: 读作“ F 等于 A非”。 通常称 A 为原变量, 为反变量, 二者共同称为互补变量。 完成“非运算”的电路叫非门或者叫反相器,其逻辑符号如图 2-6所示。

AF

A

时序电路的分析 计算机科学系 刘敏钰教授 13 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 13

(b ) (c )(a )

FA FA1

FA

图 2-6 非门的逻辑符号

(a) 常用符号; (b) 国外流行符号; (c) 国标符号

非运算的运算规则是:

10

01

时序电路的分析 计算机科学系 刘敏钰教授 14 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 14

2.2 常用复合逻辑

一、“与非”逻辑

“ 与非”逻辑是“与”逻辑和“非”逻辑的组合。 先“与”再“非”。 其表达式为:

______

BAF

实现“与非”逻辑运算的电路叫“与非门” , 其逻辑符号如图 2-7 所示。

时序电路的分析 计算机科学系 刘敏钰教授 15 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 15

(b ) (c )(a )

FB

A FAB F

A &B

图 2-7 与非门的逻辑符号

(a) 常用符号; (b) 国外流行符号; (c) 国标符号

时序电路的分析 计算机科学系 刘敏钰教授 16 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 16

二、“或非”逻辑

“ 或非”逻辑是“或”逻辑和“非”逻辑的组合。 先“或”后“非”。 其表达式为: ______

BAF

实现“或非”逻辑运算的电路叫“或非门”。其逻辑符号如图 2-8所示。

(b ) (c )(a )

FB

A £« FAB

A ¡Ý1F

B

图 2-8 或非门的逻辑符号

(a) 常用符号; (b) 国外流行符号; (c) 国标符号

时序电路的分析 计算机科学系 刘敏钰教授 17 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 17

三、“与或非”逻辑

“ 与或非”逻辑是“与”、“或”、“非”三种基本逻辑的组合。 先“与”再“或”最后“非”。 其表达式为:

______

BAF 实现“与或非”逻辑运算的电路叫“与或非门”。其逻辑符号如图 2-9所示。

(b ) (c )(a )

£« FB

A

D

CF

AB

CD

FB

A

D

C

¡Ý1&

图 2-9 与或非门的逻辑符号

(a) 常用符号; (b) 国外流行符号; (c) 国标符号

时序电路的分析 计算机科学系 刘敏钰教授 18 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 18

四、“异或”逻辑及“同或”逻辑

1. 两变量的“异或”及“同或”逻辑

若两个输入变量 A 、 B 的取值相异,则输出变量 F 为 1 ;若 A 、B 的取值相同, 则 F 为 0 。这种逻辑关系叫“异或”逻辑,其逻辑表达式为:

读作“ F 等于 A异或 B” 。 “异或”运算也叫“模 2 加”运算。

__

BABABAF

时序电路的分析 计算机科学系 刘敏钰教授 19 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 19

实现“异或”运算的电路叫“异或门”。 其逻辑符号如图 2-10 所示。

(c )(a )

FABF

B

A £« FA

B

£½1

(b )图 2- 10 异或门的逻辑符号

(a) 常用符号; (b) 国外流行符号; (c) 国标符号

若两个输入变量 A 、 B 的取值相同,则输出变量 F 为 1 ; 若 A 、 B 取值相异,则 F 为 0 。这种逻辑关系叫“同或”逻辑,也叫“符合”逻辑。其逻辑表达式为:

BABABAF __

时序电路的分析 计算机科学系 刘敏钰教授 20 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 20

实现“同或”运算的电路叫“同或门”。 其逻辑

符号如图 2 - 10 所示。

(b ) (c )(a )

FABF

B

AF

A

B

£½

图 2 – 10 同或门的逻辑符号

(a) 常用符号; (b) 国外流行符号; (c) 国标符号

时序电路的分析 计算机科学系 刘敏钰教授 21 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 21

两变量的“异或”及“同或”逻辑的真值表如表 2 - 4所示。

表 2-4 “异或”及“同或”逻辑真值表

A B

0 0

0 1

1 0

1 1

0

1

1

0

1

0

0

1

BAF BAF

时序电路的分析 计算机科学系 刘敏钰教授 22 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 22

反函数的定义:对于输入变量的所有取值组合,函数

F1 和 F2 的取值总是相反,则称 F1 和 F2 互为反函数。记

作:

1221

FFFF 或 由表 2 - 4 可知,两变量的“异或逻辑”和“同或逻辑”互为反函数。即

_______________

_______________

_________________

BABAABBAABBABABA

BABABABA

由对偶规则 ( 见第三章 ) 可知, A B 和 A B⊙ 互为对偶式。

时序电路的分析 计算机科学系 刘敏钰教授 23 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 23

2. 多变量的“异或”及“同或”逻辑

多变量的“异或”或“同或”运算, 要利用两变量的“异或门”或“同或门”来实现。实现电路分别如图 2-11 和图 2-12 所示。

A

BC

£½1

(a )

B

A

D

F

£½1

£½1

£½1

£½1

C

(b )

F

F 1

F 1

F 2

图 2 – 11 多变量的“异或”电路

时序电路的分析 计算机科学系 刘敏钰教授 24 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 24

A

BC

£½

(a )

B

A

D

y

£½

£½

£½

£½

C

(b )

y

y 1

y 1

y 2

图 2 – 12 多变量的“同或”电路

时序电路的分析 计算机科学系 刘敏钰教授 25 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 25

DCBA

DCBAYYY

DCYBAY

CBACBACYY

BAY

DCBA

DCBAFFF

DCFBAF

CBACBACFF

BAF

)()(

)(

)()(

)(

21

21

1

1

21

21

1

1由图 2 - 11(a)得:

由图 2 - 11(b)得:

由图 2 - 12(a)得:

由图 2 - 12(b)得:

时序电路的分析 计算机科学系 刘敏钰教授 26 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 26

(1) n 个变量的“异或”逻辑的输出值和输入变量取值的对应关系是:输入变量的取值组合中,有奇数个 1

时,“异或”逻辑的输出值为 1 ;反之,输出值为 0 。利用此特性,可作为奇偶校验码校验位的产生电路。

“异或”逻辑电路,可以用作奇校验码的接收端的错码检测电路。当它输出“ 0” 时,表示输入代码有错码;当它输出“ 1” 时,表示输入代码基本无错码。 ( 有可能有偶数位错码,但发生的概率很小。 ) 也可用于偶校验码的错码检测,只是其输出值“ 1” 和“ 0” 的含义与检测奇校验码时相反。

时序电路的分析 计算机科学系 刘敏钰教授 27 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 27

(2) 偶数个变量的“同或”,等于这偶数个变量的

“异或”之非。如:

A B= A B C D=⊙ ⊙ ⊙ ⊙

奇数个变量的“同或”, 等于这奇数个变量的

“异或”。如:

________

BA_____________________

DCBA

A B C= ⊙ ⊙ CBA

时序电路的分析 计算机科学系 刘敏钰教授 28 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 28

2.3 正 负 逻 辑 2.3.1 正负逻辑 在数字系统中,逻辑值是用逻辑电平表示的。若用逻辑高电平 UOH 表示逻辑“真”,用逻辑低电平 UOL 表示逻辑“假”,则称为正逻辑;反之,则称为负逻辑。本教材采用正逻辑。 当规定“真”记作“ 1” ,“假”记作“ 0” 时,正逻辑可描述为: 若 UOH 代表“ 1” , UOL 代表“ 0” ,则为正逻辑;反之,则为负逻辑。 UOH 和 UOL 统称为逻辑电平,其值因逻辑器件内部结构不同而异 (后述 ) 。 UOH 和 UOL 的差值 ( 叫逻辑摆幅 )愈大,则“1”和“ 0”

的区别越明显,电路可靠性越高。

时序电路的分析 计算机科学系 刘敏钰教授 29 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 29

2.3.2 逻辑运算的优先级别

逻辑运算的优先级别决定了逻辑运算的先后顺序。 在求解逻辑函数时,应首先进行级别高的逻辑运算。各种逻辑运算的优先级别,由高到低的排序如下:

长非号是指非号下有多个变量的非号。

][][ 加同或

异或乘

括号

长非号

时序电路的分析 计算机科学系 刘敏钰教授 30 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 30

2.3.3 逻辑运算的完备性

“ 与”、“或”、“非”是逻辑代数中三种最基本的逻辑运算。 任何逻辑函数都可以用这三种运算的组合来构成。即任何数字系统都可以用这三种逻辑门来实现。因此,称“与”、“或”、 “非”是一个完备集合,简称完备集。但是,它不是最好的完备集,因为用它实现逻辑函数,必须同时使用三种不同的逻辑门,这对数字系统的制造、维修都不方便。由反演律 ( 见逻辑代数一章 ) 可以看出,利用“与”和“非”可以得出“或”;利用“或”和“非”可以得出“与”。因此,“与非”、“或非”、 “与或非”这三种复合运算中的任何一种都能实现“与”、 “或”、“非”的功能,即这三种复合运算各自都是完备集。因此,利用“与非门”、“或非门”、“与或非门”中的任何一种, 都可以实现任何逻辑函数,这给数字系统的制造、维修带来了极大的方便。

时序电路的分析 计算机科学系 刘敏钰教授 31 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 31

2.4 集 成 逻 辑 门

把若干个有源器件和无源器件及其连线,按照一定的功能要求,制做在同一块半导体基片上,这样的产品叫集成电路。若它完成的功能是逻辑功能或数字功能, 则称为逻辑集成电路或数字集成电路。最简单的数字集成电路是集成逻辑门。

集成逻辑门,按照其组成的有源器件的不同可分为两大类: 一类是双极性晶体管逻辑门;另一类是单极性绝缘栅场效应管逻辑门,简称 MOS 门。

时序电路的分析 计算机科学系 刘敏钰教授 32 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 32

双极性晶体管逻辑门主要有 TTL 门 (晶体管 -晶体管逻辑门 ) 、 ECL 门 (射极耦合逻辑门 ) 和 I2L 门 (集成注入逻辑门 ) 等。

单极性MOS 门主要有 PMOS 门 (P沟道增强型M

OS管构成的逻辑门 ) 、 NMOS 门 (N沟道增强型MOS

管构成的逻辑门 ) 和 CMOS 门 (利用 PMOS管和 NMO

S管构成的互补电路构成的门电路,故又叫做互补 MO

S 门

时序电路的分析 计算机科学系 刘敏钰教授 33 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 33

2.4.1 TTL 与非门

典型的 TTL 与非门的电路图如图 2 - 13(a) 所示。

R 1

b

U C C

e 1 e 2 e 3 c

A B C

R 1

VD 1

VD2

VD 3

e 1

e 2

e 3

cA

B

C

VD4

P 1

b

U C C

(b )

U C C £½£«5 V

b 1

V 2

3 k

c 1

e 1

e 2

e 3

A

BC

V 1

750R 2

R 43 k

360

100R 5

V 3

V4

V 5

F

U O

(a )

c 2

R 1

R 3

图 2 – 13 典型的 TTL 与非门电路

(a) 电路原理图; (b) 多射极晶体管的等效电路

时序电路的分析 计算机科学系 刘敏钰教授 34 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 34

1. 电路结构

多发射极晶体管 V1 和电阻 R 1构成输入级。其功能是对输入变量 A 、 B 、 C 实现“与运算”,如图 2 - 13(b)

所示。

晶体管 V2 和电阻 R2 、 R3构成中间级。其集电极和发射极各输出一个极性相反的电平,分别用来控制晶体管 V

4 和 V5 的工作状态。

晶体管 V3 、 V4 、 V5 和电阻 R4 、 R5构成输出级,它们的功能是非运算。

在正常工作时, V4 和 V5总是一个截止,另一个饱和。

时序电路的分析 计算机科学系 刘敏钰教授 35 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 35

2. 功能分析

(1) 输入端至少有一个为低电平 (UIL=0.3V) 。当输入端至少有一个接低电平 UIL(0.3V) 时,接低电平的发射结正向导通,则 V1 的基极电位 UB1=UBE1+UIL=0.7+0.3=1V 。为使 V1 的集电结及 V2 和 V5 的发射结同时导通, UB1至少应当等于 2.1V(UB1=UBC1+UBE2+UBE5) 。现在 UB1=1V ,所以, V2 和 V5必然截止。由于 V2截止,故 IC2≈0 , R2 中的电流也很小, 因而 R2 上的电压很小。因此有

VUUU RCCC 522

时序电路的分析 计算机科学系 刘敏钰教授 36 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 36

该电压使 V3 和 V4 的发射结处于良好的正向导通状态,

V5处于截止状态,此时输出电压等于高电平 (3.6 V) 。

UO=UOH=UC2-UBE3-UBE4=5-0.7-0.7=3.6V

此值未计入 R2 上的压降,所以实际的 UOH 小于 3.6V 。

当 UO=UOH 时,称与非门处于关闭状态。

时序电路的分析 计算机科学系 刘敏钰教授 37 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 37

(2) 输入端全部接高电平 (UIH=3.6V) 。 V1 的基极电

位 UB1最高不会超过 2.1V 。因为当 UB1≥2.1V 时, V1 的

集电结及 V2 和 V5 的发射结会同时导通,把 UB1钳在 UB1

=UBC1+UBE2+UBE5=0.7+0.7+0.7=2.1V 。所以,当各个输入

端都接高电平 UIH(3.6V) 时, V1 的所有发射结均截止。

这时 +UCC 通过 R1使 V1 的集电结及 V2 和 V5 的发射结

同时导通,从而使 V2 和 V5处于饱和状态。此时 V2 的集

电极电位为:

UC2=UCES2+UBE5≈0.3+0.7=1V

时序电路的分析 计算机科学系 刘敏钰教授 38 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 38

UC2 加到 V3 的基极,由于 R4 的存在,可以使 V3导通。所以, V4 的基极电位和射极电位分别为:

UB4=UE3≈UC2-UBE3=1-0.7=0.3V

UE4=UCES5≈0.3V

可见, V4 的发射结偏压 UBE4=UB4-UE4=0.3-0.3=0V ,所以, V4处于截止状态。

在 V4截止、 V5饱和的情况下,输出电压 UO 为:

UO=UOL=UCES5≈0.3V

UO=UOL 时,称与非门处于开门状态。

时序电路的分析 计算机科学系 刘敏钰教授 39 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 39

综上所述,当输入端至少有一端接低电平 (0.3V) 时, 输出为高电平 (3.6V) ;当输入端全部接高电平 (3.6V)

时, 输出为低电平 (0.3 V) 。由此可见,该电路的输出和输入之间满足“与非”逻辑关系

___________

CBAF

时序电路的分析 计算机科学系 刘敏钰教授 40 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 40

(3) 输入端全部悬空。输入端全部悬空时, V1管的

发射结全部截止。 +UCC 通过 R1使 V1 的集电结及 V2 和

V5 的发射结同时导通,使 V2 和 V5处于饱和状态,则

UB3=UC2=UCES+UBE5=0.3+0.7=1V 。由于 R4 的作用, V3

导通, 故 UBE3=0.7 V 。此时 V2 的发射结电压为:

UBE4=UB4-UE4=UE3-UCES5=UB3-UBE3-UCES5

≈1-0.7-0.3=0 V

所以 V4处于截止状态。

时序电路的分析 计算机科学系 刘敏钰教授 41 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 41

可见该电路在输入端全部悬空时, V4截止, V5饱

和。故其输出电压 UO 为:

UO=UCES5≈0.3V

可见输入端全部悬空和输入端全部接高电平时,该电路的工作状态完全相同。所以, TTL 电路的某输入端悬空,可以等效地看作该端接入了逻辑高电平。实际电路中,悬空易引入干扰,故对不用的输入端一般不悬空, 应作相应的处理。

时序电路的分析 计算机科学系 刘敏钰教授 42 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 42

(4) 一个输入端通过电阻 RE接地,其它输入端接高电平。 设 V1 的发射极 A 通过 RE接地,其它输入端均接高电平,如图 2 - 14 所示。在 +UCC 的作用下,接 RE 的发射结必然导通,在 RE 上形成电压 UEA 。 RE越大,其压降 UEA越大。实验测知,只要 RE≤0.7 kΩ ,其端电压就相当于逻辑低电平。使与非门输出高电平,即与非门处于关门状态。只要 RE≥2k

Ω ,则其端电压 UEA 达到 1.4V ,此时 V1管的基极电位 UB1

=UBE1 + UEA=0.7+1.4=2.1V ,从而使 V5导通, V4截止,与非门输出低电平,即与非门处于开门状态。由于 V1管的基极电位 UB1 不可能高于 2.1V ,因此,不管 RE 的阻值有多大,其端电压最高为 1.4 V 。该电压值虽然与高电平 (3.6) 相差甚远,但其效果相当于在该端接入了高电平。

时序电路的分析 计算机科学系 刘敏钰教授 43 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 43

R 1

£«U C C

£

UB 1

V 2 V5

R3

V 1

UEA

£«

C BU IH

RE

A

图 2 – 14 一个输入端接电阻

时序电路的分析 计算机科学系 刘敏钰教授 44 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 44

当与非门的某一输入端通过电阻 RE接参考地 ( 其它输入端接高电平 ) 时,为使与非门可靠地工作在关门状态, RE

所允许的最大阻值叫该与非门的关门电阻,记作 ROFF 。为使与非门可靠地工作在开门状态, RE 所允许的最小阻值叫该与非门的开门电阻,记作 RON 。由上述分析可知,典型TTL 与非门的 ROFF=0.7 kΩ , RON=2kΩ 。考虑到不同类型的TTL 与非门,其内部结构及元件参数会有所不同,故它们的ROFF及 RON 也会有所差异。所以,在工程技术中, TTL 与非门的 ROFF 和 RON 分别取值为 0.5 kΩ 和 2 kΩ 。 综合上述,当 TTL 与非门的某一输入端通过电阻 R接地时,若 R≤0.5kΩ ,则该端相当于输入逻辑低电平;若 R≥2

kΩ ,则该端相当于输入逻辑高电平。

时序电路的分析 计算机科学系 刘敏钰教授 45 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 45

3. 主要参数

对器件的使用者来说, 正确地理解器件的各项参数是十分重要的。 (1) 输出高电平 UOH 和输出低电平 UOL 。与非门至少一个输入端接低电平时的输出电压叫输出高电平,记作 UOH 。不同型号的 TTL 与非门,其内部结构有所不同,故其 UOH 也不一样。 即使同一个与非门,其 UOH 也随负载的变化表现出不同的数值。 但是只要在 2.4~3.6V 之间即认为合格。 UOH 的标准值是 3V 。

与非门的所有输入端都接高电平时的输出电压叫输出低电平,记作 UOL 。其值只要在 0~0.5V 之间即认为合格。 UOL 的标准值是 0.3V 。

时序电路的分析 计算机科学系 刘敏钰教授 46 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 46

(2) 开门电平 UON 和关门电平 UOFF 。开门电平 UON

是保证与非门输出标准低电平时,允许输入的高电平的最小值。 只有输入电平大于 UON ,与非门才进入开门状态,输出低电平。即 UON 是为使与非门进入开门状态所需要输入的最低电平。一般产品规定 UON 在 1.4~1.8

V 之间。 关门电平 UOFF 是保证与非门输出标准高电平的 90%(2.7 V) 时,允许输入的低电平的最大值。只有输入电平低于 UOFF ,与非门才进入关门状态,输出高电平。即 UOFF 是为使与非门进入关门状态所需要输入的最高电平。一般产品规定 UOFF 在 0.8~1 V 之间。

时序电路的分析 计算机科学系 刘敏钰教授 47 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 47

(3) 噪声容限 UNH 和 UNL 。当与非门的输入端全接高电平时,其输出应为低电平,但是若输入端窜入负向干扰电压,就会使实际输入电平低于 UON ,致使输出电压不能保证为低电平。在保证与非门输出低电平的前提条件下, 允许叠加在输入高电平上的最大负向干扰电压叫高电平噪声容限 ( 或叫高电平干扰容限 ) ,记作 UNH 。其值一般为:

UNH=UIH-UON=3-1.8=1.2V

式中, UIH=3 V 是输入高电平的标准值。

时序电路的分析 计算机科学系 刘敏钰教授 48 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 48

当与非门的输入端接有低电平时,其输出应为高电平。 若输入端窜入正向干扰,以致使输入低电平叠加上该干扰电压后大于 UOFF ,则输出就不能保证是高

电平。 在保证与非门输出高电平的前提下,允许叠加在输入低电平上的最大正向干扰电压叫低电平噪声容限 ( 或叫低电平干扰容限 ) ,记作 UNL 。 其值一般为:

UNL=UOFF-UIL=0.8-0.3=0.5V

式中, UIL=0.3V 是输入低电平的标准值。

时序电路的分析 计算机科学系 刘敏钰教授 49 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 49

(4) 平均传输延迟时间 tpd 。平均传输延迟时间是

衡量门电路运算速度的重要指标。当输入端接入输入信号后,需要经过一定的时间 td ,才能在输出端产生

对应的输出信号。 td 就叫传输延迟时间。

从输入端接入高电平开始,到输出端输出低电平为止,所经历的时间叫导通延迟时间,记作 tpHL 。测

试时,把输入波形的上升边沿的中点,到对应输出波形下降边沿的中点之间的时间间隔作为 tpHL 的值。如

图 2 - 15 所示。

时序电路的分析 计算机科学系 刘敏钰教授 50 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 50

U I

UO

A

A ¡ä

tpHL

B

B ¡ä

tpLH

图 2 – 15 TTL 与非门的延迟时间

时序电路的分析 计算机科学系 刘敏钰教授 51 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 51

从输入端接入低电平开始,到输出端输出高电平为止,所经历的时间叫截止延迟时间,记作 tpLH 。测试时, 把输入波形的下降边沿的中点到对应输出波形的上升边沿的中点之间的时间间隔作为 tpLH 的值。如图 2 -15 所示。

平均传输延迟时间 tpd 是 tpHL 和 tpLH 的平均值,即

TTL 门的 tpd 在 3~40 ns 之间。

)(2

1pLHpHLpd ttt

时序电路的分析 计算机科学系 刘敏钰教授 52 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 52

(5) 空载功耗。输出端不接负载时,门电路消耗的功率叫空载功耗。

动态功耗是门电路的输出状态由 UOH 变为 UOL( 或相反 ) 时, 门电路消耗的功率。

静态功耗是门电路的输出状态不变时,门电路消耗的功率。静态功耗又分为截止功耗和导通功耗。

截止功耗 POFF 是门输出高电平时消耗的功率;导通功耗 PON 是门输出低电平时消耗的功率。导通功耗大于截止功耗。 作为门电路的功耗指标通常是指空载导通功耗。 T

TL 门的功耗范围为 1~22 mW 。

时序电路的分析 计算机科学系 刘敏钰教授 53 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 53

(6) 功耗延迟积 M 。门的平均延迟时间 tpd 和空载导通功耗 PON 的乘积叫功耗延迟积或功耗速度积,也叫品质因数, 简称 pd积。记作 M

M=PON·tpd

若 PON 的单位是 mW , tpd 的单位是 ns ,则 M 的单位是 pJ(微微焦耳 ) 。 M 是全面衡量一个门电路品质的重要指标。 M越小, 其品质越高。

74 系列 TTL 门的延迟时间及功耗如表 2 - 5 所示。

时序电路的分析 计算机科学系 刘敏钰教授 54 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 54

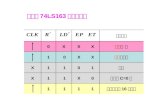

表 2 – 5 74 系列 TTL 与非门的传输延迟时间 tpd 和功耗 PON

产品型号 传输延迟时间 tpd/ns 功耗 PON/mW 产品名称的意义

7400 10 10 标准 TTL

74H00 6 22 高速 TTL

74L00 33 1 低功耗 TTL

74S00 3 19 肖特基 TTL

74LS00 9.5 2 低功耗肖特基 TTL

74ALS00 3.5 1.3 先进低功耗肖特基 TTL

74AS00 3 8 先进肖特基 TTL

时序电路的分析 计算机科学系 刘敏钰教授 55 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 55

(7) 输入短路电流 IIS 和输入漏电流 IIH 。输入短

路电流 IIS 是把与非门的一个输入端直接接地 ( 其它

输入端悬空 ) 时,由该输入端流向参考地的电流,也

叫低电平输入电流。 IIS 的典型值约为 1.5mA 。

输入漏电流 IIH 是把与非门的一个输入端接高电

平 ( 其它输入端悬空 ) 时,流入该输入端的电流,也

叫高电平输入电流。因为此时 V1管处于倒置状态,

故 IIH 数值很小, 一般为几十微安。

时序电路的分析 计算机科学系 刘敏钰教授 56 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 56

(8) 最大灌电流 IOLmax 和最大拉电流 IOHmax 。 IOLmax

是在保证与非门输出标准低电平的前提下,允许流进

输出端的最大电流, 一般为十几毫安。 IOHmax 是在保

证与非门输出标准高电平并且不出现过功耗的前提下,允许流出输出端的最大电流,一般为几毫安。

实际应用中,若输出电流超出 IOLmax 或 IOHmax ,则

与非门就可能输出不正确的逻辑电平。

时序电路的分析 计算机科学系 刘敏钰教授 57 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 57

(9) 扇入系数 NI 。扇入系数是门电路的输入端数。

一般 NI≤5 ,最多不超过 8 。当需要的输入端数超过 NI

时,可以用与扩展器来实现。

(10) 扇出系数 NO 。扇出系数 NO 是在保证门电路输

出正确的逻辑电平和不出现过功耗的前提下,其输出端允许连接的同类门的输入端数。

NO 由 IOLmax/IIS 和 IOHmax/IIH 中的较小者决定。一般 NO

≥8 , NO越大,表明门的负载能力越强。

时序电路的分析 计算机科学系 刘敏钰教授 58 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 58

(11) 最小负载电阻 RLmin 。 RLmin 是为保证门电路输出正确的逻辑电平,在其输出端允许接入的最小电阻 ( 或最小等效电阻 ) 。

在门的输出端接上负载电阻 RL后,只要 RL 的阻值不趋近于零,对于输出低电平几乎无影响。但 RL阻值太小, 会使门电路无法输出正确的高电平。因为与非门处于关门状态时,应当输出高电平,此时流经 RL 的电流 IRL 的实际方向是由门的输出端经 RL 流向参考地,如图 2-16 所示。 属于门电路的拉电流的最大允许值为 IOHmax 。与非门的输出电平 UO=I

RL·RL 。若 RL阻值太小,就会使得 IRL 达到允许的最大值 IOHm

ax 时,输出电平仍低于 UOHmin ,从而造成逻辑错误。为了输出正确的逻辑高电平, RL 的阻值必须使如下的不等式成立:

时序电路的分析 计算机科学系 刘敏钰教授 59 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 59

max

minmin

max

min

minmax

OH

OHL

OH

OHL

OHLOH

I

UR

I

UR

URI

即

亦即

对于 TTL 标准系列,按上式求得的 RLmin 的阻值范围为 150~200Ω ,为留有余地,一般取 RLmin=200Ω 。对于 TT

L 改进系列 ( 如高速系列及低功耗系列等 ) ,按上式求得的 RLmin 相差很大,很难确定一个参考值。在实际工作中,应根据给定的参数按上式进行计算。

时序电路的分析 计算机科学系 刘敏钰教授 60 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 60

(12) 输入高电平 UIH 和输入低电平 UIL 。一般取 UIH

≥2 V , UIL≤0.8V 。

V 4

R 4

U CC

R 2

V 3

R 5

R L

£«

£

UO

I O

图 2-16 接入 RL 输出 UOH 的情况

时序电路的分析 计算机科学系 刘敏钰教授 61 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 61

2.4.2 OC 门和三态门

一般的 TTL 门电路,不论输出高电平,还是输出低电平,其输出电阻都很低,只有几欧姆至几十欧姆。因此不能把两个或两个以上的 TTL 门电路的输出端直接并接在一起。否则,当其中一个输出高电平,另一个输出低电平时,它们中的导通管,就会在 +UCC 和地之间形成一个低阻串联通路。因此产生的大电流会导致门电路因功耗过大而损坏。即使门电路不被损坏,也不能输出正确的逻辑电平,从而造成逻辑混乱。图 2 - 17 是门1 输出高电平,门 2 输出低电平时,两者的并联情况。

时序电路的分析 计算机科学系 刘敏钰教授 62 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 62

FI

L

V2

V5

门 2

门 1

V3

V 4

U CC

R 5

£«

£ U R 5

F 1

F2

£«

£

UO

图 2— 17

两个T

TL

门输出端并联情

况

时序电路的分析 计算机科学系 刘敏钰教授 63 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 63

因为门 1 输出高电平,所以其 V4管饱和导通 ( 其 V5管截止,图中未画 ) 。

而门 2 输出低电平,所以其 V5管饱和导通 ( 其 V4管截止,未画 ) 。门 1 和门 2 的输出端直接并接后,则 UCC经 R5

和处于饱和导通状态的 V4( 门 1)管和 V5( 门 2)管到参考地, 会产生很大的电流。使得两个门电路因功耗过大而损坏。 即使侥幸门未损坏,则其输出电平 UO 为:

VRIUUUU LCCRCCO 5.1)(2

1)(

2

155

此值既不属于逻辑高电平,也不属于逻辑低电平。

OC 门和三态门是允许输出端直接并接在一起的两种 TTL门。

时序电路的分析 计算机科学系 刘敏钰教授 64 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 64

1. OC 门 ( 集电极开路门 )

OC 门的典型电路及逻辑符号如图 2 - 18 所示。

FA

BV 1

V5

V 2

R 3

£«U CC

R2

R1

(a )

A

BF

A

BF

&

(b ) (c )

图 2–18 OC 门电路

(a) 电路; (b) 常用符号; (c) 国标符号

时序电路的分析 计算机科学系 刘敏钰教授 65 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 65

(1) 电路结构及功能分析。 OC 门的电路特点是其输出管的集电极开路。使用时,必须外接“上拉电阻 RC” 和+UCC 相连。多个 OC 门输出端相连时,可以共用一个上拉电阻 RC , 如图 2 - 19 所示。

(a ) (b )

B

A

D

C

F

F1

F2

&

&

&

&

&

AB

CD

门 2

门 1F1

F2

线与

F

RC ICC

图 2 – 19 多个 OC 门并联

(a) 线与逻辑电路; (b) 等效逻辑图

时序电路的分析 计算机科学系 刘敏钰教授 66 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 66

OC 门接入上拉电阻 RC后,与图 2 - 13 所示的与非

门的差别仅在于用外接电阻 RC 取代了由 V3 和 V4构成的

有源负载。 当其输入中有低电平时, V2 和 V5 均截止,

F端输出高电平; 当其输入全是高电平时, V2 和 V5导

通,只要 RC 的取值足够大, V5 就可以达到饱和,使 F

端输出低电平。可见 OC 门外接上拉电阻 RC后,就是一

个与非门。

两个 OC 门输出端并联的电路如图 2 - 19 所示。

时序电路的分析 计算机科学系 刘敏钰教授 67 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 67

若 F1=0, F2=1 ,即 OC1 的输出管 V5导通, OC2 的 V5

管截止, 则流过 RC 的电流 ICC全部灌入 OC1 的 V5管。只要 RC 的阻值足够大,就会使 OC1 的 V5管饱和。此时, ICC

等于 OC1 的 V5管的集电极电流 IC5 。所以:

UO=UCC-URC=UCC-ICCRC=UCC-IC5RC=UCES5=UOL

式中, UCES5 是 V5管的饱和压降。可见,只要 F1 和 F2 中之一为逻辑“0”,则输出 F 就为“ 0” 。

若 F1=F2=0 ,即两个门的输出管都导通,则流过 RC 的电流 ICC 是两个输出管的集电极电流之和。其值要比一个输出管导通时大,因此,输出电平 UO更低,即 F=0 。

时序电路的分析 计算机科学系 刘敏钰教授 68 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 68

若 F1=F2=1, 即两个 OC 门的输出管均截止,则流过RC 的电流 ICC 是两个输出管的穿透电流之和,即 ICC=2ICEO5 。所以

UO=UCC-ICCRC=UCC-2ICEO5RC=UOH

故 F=1 。 表 2-6 逻辑功能表 F1 F2 F

0 0

0 1

1 0

1 1

0

0

0

1

时序电路的分析 计算机科学系 刘敏钰教授 69 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 69

通过上述分析可知,由于 RC 的阻值较大,因此,不论两个 OC 门处于何种状态,在 +UCC 和地之间都不会出现低阻通路,电路可以安全工作。两个 OC 门并联后实现的逻辑功能可用表 2 - 6 描述。显然, F 与 F1 、 F2 之间是“与”逻辑关系, 即 F=F1·F2

由于这种“与”逻辑是两个 OC 门的输出线直接相连实现的, 故称作“线与”。图 2 - 19 实现的逻辑表达式为:

F=F1·F2=AB·CD

除了 TTL 与非门可以做成 OC 门外,其它 TTL 门也可做成 OC 门,并且也能实现“线与”或“线或”。

时序电路的分析 计算机科学系 刘敏钰教授 70 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 70

(2) RC 的计算。 RC 的选取原则是保证 OC 门输出的高电平不低于 UOHmin ;输出的低电平不大于 UOLmax 。 在 OC 门的实际应用中,经常需要多个 OC 门并联后为多个负载门提供输入信号。图 2 - 20(a) 、 (b) 是 n 个 O

C 门并联后为负载门的 m 个输入端提供输入信号的两种情况。

图 2-20(a) 是 n 个 OC 门全部输出 UOH 的情况。此时所有 OC 门的输出管都截止,因此,流入每个 OC 门输出端的电流都是其输出管的穿透电流 ICEO(OC 门正常工作时,不论输出 UOH还是 UOL ,都不产生拉电流 ) ;流入负载门各输入端的电流都是高电平输入漏电流 IIH 。各电流的实际方向如图 2 - 20(a) 中所示。

时序电路的分析 计算机科学系 刘敏钰教授 71 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 71

(a )

£«U CC

¡

&

&

1

1

¡

I IH

ICCRC

(b )

ICEO

ICEO

ICEO

I IH

I IH

I IH

A

共有n个门

m个输入端

&

£«U CC

¡ &

&

&1

1

¡

I IS

ICCRC

IOL

IOL

IOL

I IS

I IS

I IS

A

m个输入端

&

n个门

£«3.6 V

&

图 2 – 20 外接上拉电阻的计算

时序电路的分析 计算机科学系 刘敏钰教授 72 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 72

CHCEOCCCCCCCOH RmInIURIUU )( 1

为使 UOH≥UOHmin ,则必须使

HCEO

OHCCC

HCEO

OHCCC

OHCHCEOCC

mInI

UUR

mInI

UUR

URmInIU

1

minmax

1

min

min1 )(

即

故

时序电路的分析 计算机科学系 刘敏钰教授 73 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 73

ICC 和所有的负载电流全部流入唯一导通门的输出管 V5 对导通门来说这是负载最重的情况。因为

CSOLCCCCCCCOL

SOLCC

RmIIURIUU

mIII

)( 1

1

所以

时序电路的分析 计算机科学系 刘敏钰教授 74 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 74

综合上述两种情况,上拉电阻 RC 的取值范围是:

RCmin≤RC≤RCmax

为保证 IOL=IOLmax 时, UOL≤UOLmax ,应当使

SOL

OLCCC

SOL

OLCCC

OLCSOLCC

mII

UUR

mII

UUR

URmIIU

1max

maxmin

1max

max

max1max )(

即

故

式中, IOLmax 是一OC 门允许的最大灌电流。

时序电路的分析 计算机科学系 刘敏钰教授 75 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 75

(3) OC 门的应用。

① 实现多路信号在总线 ( 母线 ) 上的分时传输,如图 2 - 21 所示。 E

1

A

&

&

R C

&

&

¡

F1

F 2

F 3

F n

&

&

B

y a

y b

£«U C CD

1

D2

E 2

D 3

E 3

Dn

E n

图 2 – 21 OC 门实现总线传输

时序电路的分析 计算机科学系 刘敏钰教授 76 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 76

② 实现电平转换——抬高输出高电平。由 OC 门的功能分析可知, OC 门输出的低电平 UOL=UCES5≈0.3

V ,高电平 UOH=UCC-ICEO5RC≈UCC 。所以,改变电源电压可以方便地改变其输出高电平。只要 OC 门输出管的 U(BR)CEO 大于 UCC , 即可把输出高电平抬高到 UCC

的值。 OC 门的这一特性, 被广泛用于数字系统的接口电路,实现前级和后级的电平匹配。

时序电路的分析 计算机科学系 刘敏钰教授 77 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 77

③ 驱动非逻辑性负载。图 2-22(a) 是用来驱动发光二极管 (LED) 的。当 OC 门输出 UOL 时, LED导通发光;当 OC

门输出 UOH 时, LED截止熄灭。 图 2-22(b) 是用来驱动干簧继电器的。二极管 VD保护OC 门的输出管不被击穿。工作过程如下: OC 门输出 UOL

时,有较大的电流经继电器线圈流入 OC 门,干簧管被吸合,VD 相当于开路,不影响电路工作。当 OC 门输出 UOH 时,OC 门的输出管截止,流过线圈的电流突然减小为 ICEO ,干簧管断开。此时若无 VD ,则线圈中的感应电动势与 UCC 同向串联后,加到 OC 门的集电极和发射极之间,会使其集电结击穿。接入 VD后,与 UCC极性相同的感应电动势使 VD

导通,感应电动势大大减小, OC 门的输出管就不会被击穿。

时序电路的分析 计算机科学系 刘敏钰教授 78 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 78

图 2 - 22(c) 是用来驱动脉冲变压器的。脉冲变压器与普通变压器的工作原理相同,只是脉冲变压器可工作在更高的频率上。

图 2-22(d) 是用来驱动电容负载的,构成锯齿波发生器。 当 UI=UOL

时, OC 门截止, UCC 通过 RC 对电容 C充电, UO近似线性上升;当 UI

=UOH 时, OC 门导通,电容通过 OC 门放电, UO迅速下降,在电容两端形成锯齿波电压。

C

U O

U I

£«U CC

R C

(d )

&

U I

UO&

+ UCC

(b )

VD

&

+ U CC

(a )

&

+ UCC

(c )

RL

图 2 - 22 OC 门驱动非逻辑性负载

时序电路的分析 计算机科学系 刘敏钰教授 79 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 79

④ 用来实现“与或非”运算。利用反演律可把图 2-19 的输出函数变换为:

F=AB·CD=AB+CD

用 OC 门实现“与或非”运算,要比用其它门的成本低。

OC 门的外接电阻的大小会影响系统的开关速度, 其值越大, 工作速度越低。由于它只能在 RCmin

和 RCmax 之间取值,开关速度受到限制,故 OC 门只适用于开关速度不高的场合。

时序电路的分析 计算机科学系 刘敏钰教授 80 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 80

2. 三态门 (TS 门或 TSL 门 )

一种三态与非门的电路及逻辑符号如图 2 - 23 所示。

A

F

U CC £½£« 5 V

V 4

V5

V 3

V 2V 1B

3 kR 2

R 5

R 4

U O

R 1

b 1e

1e 2

R6

G

3 k

R 3360

750 100

V 6

V D

(a )

(c )

(d )

(b )

FB

A

G

FABG

FAB

ENG

图 2 – 23 三态 TTL 与非门电路及符号

(a) 电路; (b) 常用符号; (c) 国外流行符号; (d) 国标符号

时序电路的分析 计算机科学系 刘敏钰教授 81 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 81

(1) 功能分析。在图 2 - 23(a) 中, G端为控制端,也叫

选通端或使能端。 A端与 B端为信号输入端, F端为输出

端。

当 G=0( 即 G端输入低电平 ) 时,晶体管 V6截止,其

集电极电位 UC6 为高电平,使晶体管 V1 中与 V6集电极相

连的那个发射结也截止。由于和二极管 VD 的 N区相连的

PN 结全截止, 故 VD截止,相当于开路,不起任何作用。

这时三态门和普通与非门一样,完成“与非”功能,即 F=

A·B 。这是三态门的工作状态,也叫选通状态。

时序电路的分析 计算机科学系 刘敏钰教授 82 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 82

当 G=1( 即 G端输入高电平 ) 时, V6饱和导通, UC6

为低电平, 则 VD导通,使 UC2被钳制在 1V 左右,致使V4截止。同时 UC6使 V1管射极之一为低电平,所以 V2 、V5 也截止。由于同输出端相接的两个晶体管 V4 和 V5 同时截止,因而输出端相当于悬空或开路。这时三态门相对负载而言呈现高阻抗, 故称这种状态为高阻态或悬浮状态,也叫禁止状态。在禁止状态下,三态门与负载之间无信号联系,对负载不产生任何逻辑功能,所以禁止状态不是逻辑状态,三态门也不是三值逻辑门,叫它“三态门”只是为区别于其它门的一种“方便称呼”。

时序电路的分析 计算机科学系 刘敏钰教授 83 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 83

该三态门的真值表如表 2 - 7 所示。

G A B F

1 X X

0 0 0

0 0 1

0 1 0

0 1 1

高阻1

1

1

0

表 2-7 三态门的真值表

时序电路的分析 计算机科学系 刘敏钰教授 84 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 84

(2) 分类。三态门可以按如下的方式分类:

① 按逻辑功能分为四类,即三态与非门、三态缓冲门、三态非门 ( 三态倒相门 ) 、三态与门。其逻辑符号如图 2 - 24 所示。

② 按控制模式分为两类,即低电平有效的三态门和高电平有效的三态门。低电平有效的三态门是指当 G=0

时,三态门工作;当 G=1 时,三态门禁止。其逻辑符号如图 2 - 24(a) 所示。这类三态门也叫做低电平选通的三态门。高电平有效的三态门是指当 G=1 时,三态门工作;当 G=0 时,三态门禁止。其逻辑符号如图 2 - 24(b)

所示。这类三态门也叫做高电平选通的三态门。

时序电路的分析 计算机科学系 刘敏钰教授 85 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 85

(a )

(b )

A

G

F

1

EN

三态缓冲门

A

G

F

1

EN

三态倒相门

A

B

G

F

&

EN

三态与门

A

B

G

F

&

EN

三态与非门

A

G

F

三态缓冲门

1

ENA

G

F

三态倒相门

1

EN EN

A

B

G

F

&

三态与门

A

B

G

F

&

EN

三态与非门

图 2 – 24 各种三态门的逻辑符号

时序电路的分析 计算机科学系 刘敏钰教授 86 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 86

③ 按其内部的有源器件分为两类,即三态 TTL 门和三态 MOS 门。

(3) 用途。三态门主要用来实现多路数在总线上的分时传送,如图 2 - 25(a) 所示。 为实现这一功能,必须保证在任何时刻只有一个三态门被选通,即只有一个门向总线传送数据;否则,会造成总线上的数据混乱,并且损坏导通状态的输出管。传送到总线上的数据可以同时被多个负载门接收,也可在控制信号作用下,让指定的负载门接收。

时序电路的分析 计算机科学系 刘敏钰教授 87 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 87

( b )

D 1 G 1 D 2 G 2

数据总线

( a )

D n G n

…

…

G

A B

1 EN 1 EN 1 EN

门 1

门 2

1

EN

1

EN

图 2 – 25 三态门的应用(a) 三态门用于总线传输; (b) 三态门实现双向传送

利用三态门可以实现信号的可控双向传送,如图 2-25

(b) 所示。当 G=0 时,门 1选通,门 2禁止,信号由 A 传送到 B ;当 G=1 时,门 1禁止,门 2选通,信号由 B 传送到 A 。

时序电路的分析 计算机科学系 刘敏钰教授 88 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 88

3. 三态门和 OC 门的性能比较

(1) 三态门的开关速度比 OC 门快。因为输出高电平时,三态门的 V4管是按射极输出器的方式工作,其输出电阻小,输出端的分布电容充电速度快, uO 很快由 UOL

变到 UOH ;而 OC 门在输出高电平时,其输出电阻约等于外接的上拉电阻 RC , 其值比射极输出器的输出电阻大得多,故对输出分布电容的充电速度慢, uO 的上升时间长。在输出低电平时,两者的输出电阻基本相等,故两者 uO

的下降时间基本相同。

时序电路的分析 计算机科学系 刘敏钰教授 89 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 89

(2) 允许接到总线上的三态门的个数,原则上不受限制,但允许接到总线上的 OC 门的个数受到上拉电阻RC 的取值条件的限制。

(3)OC 门可以实现“线与”逻辑,而三态门则不能。若把多个三态门输出端并联在一起,并使其同时选通, 当它们的输出状态不同时,不但不能输出正确的逻辑电平,而且还会烧坏导通状态的输出管。

TTL产品中除与非门外,还有或非门、与或非门、与门、 或门、 异或门等。

时序电路的分析 计算机科学系 刘敏钰教授 90 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 90

2.4.3 MOS 集成逻辑门 MOS 逻辑门是用绝缘栅场效应管制作的逻辑门。在半导体芯片上制作一个 MOS管要比制作一个电阻容易,而且所占的芯片面积也小。所以,在 MOS集成电路中,几乎所有的电阻都用 MOS管代替,这种 MOS管叫负载管。在 MOS 逻辑电路中,除负载管有可能是耗尽型外,其它 MOS管均为增强型。 MOS 逻辑电路有 PMOS 、 N

MOS 和 CMOS 三种类型。 PMOS 逻辑电路是用 P沟道MOS管制作的。由于工作速度低,而且采用负电源,不便和 TTL 电路连接, 故其应用受到限制。

时序电路的分析 计算机科学系 刘敏钰教授 91 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 91

NMOS 逻辑电路是用 N沟道MOS管制作的。其工作速度比 PMOS 电路高,集成度高,而且采用正电源,便于和 TTL 电路连接。其制造工艺适宜制作大规模数字集成电路,如存储器和微处理器等。但不适宜制作通用型逻辑集成电路。 ( 这种电路要求在一个芯片上制作若干不同类型的逻辑门和触发器。 )主要是因为 NMOS

电路对电容性负载的驱动能力较弱。

时序电路的分析 计算机科学系 刘敏钰教授 92 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 92

CMOS 逻辑电路是用 P沟道和 N沟道两种 MOS管构成的互补电路制作的。和 PMOS 、 NMOS 电路相比,CMOS 电路的工作速度高,功耗小,并且可用正电源,便于和 TTL 电路连接。所以它既适宜制作大规模数字集成电路,如寄存器、存储器、微处理器及计算机中的常用接口等,又适宜制作大规模通用型逻辑电路,如可编程逻辑器件等。

MOS 门的各项指标的定义和 TTL 门的相同, 只是数值有所差异。

时序电路的分析 计算机科学系 刘敏钰教授 93 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 93

对于 NMOS 和 CMOS 门,若电源电压为 UDD 时,

UOH≈UDD , UOL≈0; UIH≈UDD , UIL≈0 。

由于 UDD 的取值在 3~20V 之间,故输入电平摆幅

和输出电平摆幅都很大,所以抗干扰能力强。若把 C

MOS 改用双电源 (±UDD 或 +UDD 和 -USS)供电,则高低

电平的摆幅更大,噪声容限更大。

由于各种 MOS 门的工作原理类似,所以下面只

讨论应用日益广泛的 CMOS 逻辑门 。

时序电路的分析 计算机科学系 刘敏钰教授 94 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 94

1. CMOS 反相门 (CMOS 非门 )

CMOS 反相器的电路图如图 2 - 26 所示。 U DD

U OU I

V 2 (P沟道 )

V 1 (N )沟道G 1

G 2 S 2

S 1

图 2 – 26 CMOS 门反相器电路

时序电路的分析 计算机科学系 刘敏钰教授 95 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 95

V1 是 N沟道 MOS管 ( 简称 NMOS管 ) ,用作驱动管。其开启电压 UTN 为正值,约为 1~5V 。只有当 UGS>UTN 时,V1 才导通;当 UGS<UTN 时, V1截止。

V2 是 P沟道MOS管 ( 简称 PMOS管 ) ,用作负载管。其开启电压 UTP 是负值,约为 -2~-5V 。当 UGS<UTP 时, V2

导通;当 UGS>UTP 时, V2截止。

电源电压 UDD 可在 3~20V 之间选择。但是为保证电路正常工作,必须使 UDD>UTN+|UTP| 。

当 UI=UIL=0V 时, UGS1=0<UTN ,因此 V1截止。而此时UGS2=-UDD<UTP ,故 V2 导通,所以, UO=UOH≈UDD ,即输出高电平。

时序电路的分析 计算机科学系 刘敏钰教授 96 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 96

当 UI=UIH=UDD 时, UGS1=UDD>UTN ,故 V1导通。而此时 UGS2=0>UTP ,因此 V2截止。所以, UO=UOL≈0 ,即输出低电平。

可见该电路实现了“非逻辑”功能。

该电路在静态 (UO=UOH 或 UO=UOL) 条件下,不论输出高电平还是输出低电平, V1 和 V2 中总有一个截止,并且截止时阻抗极高,因此流过 V1 和 V2 的静态电流很小,故该电路的静态功耗非常低。这是 CMOS

电路共有的优点。

时序电路的分析 计算机科学系 刘敏钰教授 97 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 97

2. CMOS 与非门

图 2-27 所示为 CMOS 与非门电路。图中, V1 和 V2 是两个串联的 N

MOS管,用作驱动管; V3 和 V4 是两个并联的 PMOS管,用作负载管。V1 和 V3 为一对互补管,它们的栅极作为输入端 A ; V2 和 V4 作为另一对互补管,它们的栅极相连作为输入端 B 。 V2 和 V4 的漏极相连作为输出端F 。 V2 的衬底没有和自己的源极相接,而是与 V1 的源极、衬底相接后,共同接地。这是为了更容易产生导电沟道。因为沟道的产生及其宽度,实质上是受栅极 G 和衬底 B 之间的电压 UGB 的控制 (多数情况下,源极 S 和衬底 B短接, UGS=UGB ,此时可以认为沟道的产生受 UGS 的控制 ) 。本电路中,只要 B端输入电压 UIB>UTN ,则 V2 就产生沟道。若把 V2 的衬底和自己的源极相连,只有当 B端输入电压 UIB>UTN+UDS1 时, V2 才产生沟道。

时序电路的分析 计算机科学系 刘敏钰教授 98 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 98

U DD

F

V 3 (P )

A

B

V 4 (P )

V 2 (N )

V 1 (N )

图 2-27 CMOS 与非门电路

时序电路的分析 计算机科学系 刘敏钰教授 99 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 99

当两个输入端 A 、 B 均输入高电平 (UIH=UDD) 时, V1

和 V2 的“栅 -衬”间的电压均为 UDD ,其值大于 UTN ,故V1 和 V2 均产生沟道而导通。而 V3 和 V4 的“栅 - 衬”间的电压均为 0 V ,其值大于 UTP ,故 V3 和 V4 均不产生沟道而截止。由于截止管的“漏极和源极之间的等效电阻 rDS”

近似为∞,因而 F端的输出电压 UO=UOL≈0 V 。

当两个输入端 A 和 B 中至少有一个输入低电平 (UIL=0)

时, V1 和 V2 中至少有一个不能产生导电沟道,处于截止状态。 V3 和 V4 中至少有一个产生沟道,处于导通状态。 所以,此种情况下, F端的输出电压 UO=UOH≈UDD 。

综合上述, F 和 A 、 B 之间是“与非逻辑”关系。即

F=A·B

时序电路的分析 计算机科学系 刘敏钰教授 100 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 100

3. CMOS 或非门

CMOS 或非门的电路如图 2 - 28 所示。图中, V1 和V2 是两个并联的 N沟道MOS管,用作驱动管; V3 和V4 是两个串联的 P沟道MOS管,用作负载管。 V2 和V3 为一对互补管, 它们的栅极相连作为输入端 A ; V1

和 V4 为另一对互补管,它们的栅极相连作为输入端 B 。F 是 CMOS 或非门电路的输出端。

当两个输入端 A 、 B 均输入低电平 (UIL=0V) 时,V1 和 V2 均不开启,处于截止状态; V3 和 V4 均被开启导通。故 F端必定输出高电平 UOH≈UDD

时序电路的分析 计算机科学系 刘敏钰教授 101 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 101

F

V1

(N )

B

A

V 2 (N )

V3

(P )

V 4 (P )

U DD

图 2 - 28 CMOS 或非门电路

时序电路的分析 计算机科学系 刘敏钰教授 102 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 102

当两个输入端 A 、 B 中至少有一个为高电平 (UIH≈UD

D) 时, V1 和 V2 中至少有一个开启导通; V3 和 V4 中至少

有一个不产生沟道而截止。故 F端必输出低电平 UOL≈0 。

可见,该电路的 F 和 A 、 B 之间是“或非”逻辑关系, 即 F=A+B

时序电路的分析 计算机科学系 刘敏钰教授 103 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 103

比较与非门电路和或非门电路可知。与非门的驱动管是由多个 NM

OS管串联构成,即有几个输入端,就有几个管子串联。其输出低电平是各驱动管 D 、 S极间导通电压的和。

故其 UOL 的值较高,为保证 UOL 不超过 UOLmin ,其输入端一般不超过三个。或非门的驱动管是由多个 NMOS管并联构成的, 有几个输入端,就有几个管子并联。其输出低电平是一个驱动管的 D 、 S极间导通电压,增加输入端数,不会提高 UOL 的值。故其输入端数不受 UOL 取值的限制。因此,在 CMOS( 或 NMOS) 数字集成电路中是以或非逻辑为基础的。 利用与非门、或非门、非门,可以构成与门、或门、与或非

门、异或门、异或非门 ( 同或门 ) 等。

时序电路的分析 计算机科学系 刘敏钰教授 104 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 104

4. CMOS 传输门

CMOS 传输门的电路和符号如图 2 - 29 所示。它

由一个 NMOS管 V1 和一个 PMOS管 V2 并联而成。

V1 和 V2 的源极和漏极分别相接作为传输门的输入端

和输出端。两管的栅极是一对互补控制端, C端叫

高电平控制端, C端叫低电平控制端。两管的衬底

均不和源极相接, NMOS管的衬底接地, PMOS管

的衬底接正电源 UDD ,以便于控制沟道的产生。

时序电路的分析 计算机科学系 刘敏钰教授 105 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 105

C

C

V 2

V 1

U I / U O U O / U I

U DD

(a )

TGU I / U O U O / U I

C

C

(b )

图 2 – 29 CMOS 传输门(a) 电路; (b) 符号

时序电路的分析 计算机科学系 刘敏钰教授 106 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 106

把 NMOS管 V1 的栅极和衬底之间的电压记为 UGB1 ,

开启电压记为 UTN ,则当 UGB1>UTN 时, V1产生沟道;当

UGB1<UTN 时, V1 的沟道消失。

把 PMOS管 V2 的“栅 - 衬”间的电压记为 UGB2 ,

开启电压记为 UTP ,则当 UGB2<UTP 时, V2 产生沟道;当

UGB2>UTP 时, V2 的沟道消失。

当 C= UDD, C=0V 时, V1 的 UGB1=UDD>UTN,故 V1 导

通; V2 的 UGB2=-UDD< UTP, 故 V2 也导通。所以此时在 V1

和 V2 的“漏 - 源”之间同时产生导电沟道,使输入端与输出端之间形成导电通路,相当于开关接通。

时序电路的分析 计算机科学系 刘敏钰教授 107 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 107

当 C=0 , C=UDD 时, V1 的 UGB1=0<UTN ,故 V1

不能产生沟道; V2 的 UGB2=0> UTP ,故 V2 也不能产生导电沟道。所以, 在这种情况下,输入端与输出端之间呈现高阻抗状态, 相当于开关断开。

由于 MOS管的结构对称,其漏极和源极可以互换, 因而 TG 的输入端和输出端可以互换使用,即 TG

是双向器件。

时序电路的分析 计算机科学系 刘敏钰教授 108 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 108

把一个传输门 TG 和一个非门按图 2-30(a)连接起来,即可构成模拟开关,其符号如图 2 - 30(b) 所示。当 C=1 时,开关接通;当 C=0 时,开关断开。该模拟开关也是双向器件。

UI

/ UO

UO

/ UI

SWUI

/ UO

UO

/ UI

C

(b )

TG

1C

(a )

图 2 – 30 CMOS模拟开关 (a) 电路; (b) 符号

时序电路的分析 计算机科学系 刘敏钰教授 109 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 109

5. CMOS 三态非门

图 2 - 31 所示为 CMOS 三态非门电路。两个 NMOS

管 V1 和 V2 串联,另外两个 PMOS管 V3 和 V4 也串联。

两组串联 MOS管构成等效互补电路, V2 和 V3 一对互补管构成 CMOS 反相器 ( 非门 ) ,其栅极相接作为三态非门的信号输入端, V1 和 V4 一对互补管构成控制电路,两者的栅极反相连接后作为控制端 ( 也叫选通端 ) 。

时序电路的分析 计算机科学系 刘敏钰教授 110 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 110

F

V 2 (N )

V 4 (P )

U DD

1G

A

V3

(P )

V1

(N )

图 2 – 31 CMOS 三态非门电路

时序电路的分析 计算机科学系 刘敏钰教授 111 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 111

当 G=1 时, V1 和 V4 均不产生导电沟道,不论 A

为何值, F端均处于高阻态,相当于 F端悬空,称为禁止状态。

当 G=0 时, V1 和 V4 均产生导电沟道,处于导通状态。此时若把 V1 和 V4近似用短路线代替,则该电路就与图 2-26 所示的反相器一样,完成非运算 F=A 。

可见该电路是一个低电平选通的三态非门。 CMO

S 三态门的逻辑符号与 TTL 三态门相同。

时序电路的分析 计算机科学系 刘敏钰教授 112 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 112

6. CMOS 逻辑电路的特点 ( 与 TTL 门比较 )

(1) 工作速度比 TTL稍低。

(2) 输入阻抗高,可达 108 Ω 。

(3) 扇出系数 NO 大。

(4) 静态功耗小。

(5) 集成度高。

(6) 电源电压允许范围大, 约为 3~20 V 。

(7) 输出高低电平摆幅大。

时序电路的分析 计算机科学系 刘敏钰教授 113 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 113

(8) 抗干扰能力强。

(9) 温度稳定性好。

(10) 抗辐射能力强。

(11) 电路结构简单 (CMOS 与非门只有四个管子构成,而 TTL 与非门共有五个管子和五个电阻 ) ,工艺容易 ( 做一个 MOS管要比做一个电阻更容易,而且占芯片面积小 ) ,故成本低。

(12) 输入高、低电平 UIH 和 UIL 均受电源电压 UDD 的限制。

(13) 拉电流 IOL<5 mA ,要比 TTL 门的 IOL( 可达 20m

A) 小得多。

时序电路的分析 计算机科学系 刘敏钰教授 114 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 114

2.4.4 集成逻辑门使用中的实际问题

1. 多余输入端的处理

(1) TTL 门。 TTL 门的输入端悬空,相当于输入高

电平。 但是,为防止引入干扰,通常不允许其输入端悬

空。 对于与门和与非门的多余输入端,可以使其输

入高电平。具体措施是将其通过电阻 R(约几千欧 )接 +

UCC ,或者通过大于 2 kΩ 的电阻接地。在前级门的扇出

系数有富余的情况下,也可以和有用输入端并联连接。

时序电路的分析 计算机科学系 刘敏钰教授 115 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 115

表 2-8 CMOS 各系列的传输延迟时间、功耗及电源电压

时序电路的分析 计算机科学系 刘敏钰教授 116 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 116

对于或门及或非门的多余输入端,可以使其输入低电平。具体措施是通过小于 500 Ω 的电阻接地或直接接地。在前级门的扇出系数有富余时, 也可以和有用输入端并联连接。

对于与或非门,若某个与门多余,则其输入端应全部输入低电平 (接地或通过小于 500Ω 的电阻接地 ) ,或者与另外同一个门的有用端并联连接 ( 但不可超出前级门的扇出能力 ) 。

若与门的部分输入端多余, 处理方法和单个与门方法一样。

时序电路的分析 计算机科学系 刘敏钰教授 117 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 117

(2) MOS 门。 MOS 门的输入端是 MOS管的绝缘

栅极, 它与其它电极间的绝缘层很容易被击穿。虽然

内部设置有保护电路,但它只能防止稳态过压,对瞬

变过压保护效果差,因此 MOS 门的多余端不允许悬空。

由于 MOS 门的输入端是绝缘栅极,所以通过一个

电阻 R 将其接地时,不论 R多大,该端都相当于输入

低电平。除此以外, MOS 门的多余输入端处理方法与

TTL 门相同。

时序电路的分析 计算机科学系 刘敏钰教授 118 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 118

2. 接口电路

接口电路的作用是通过逻辑电平的转换,把不同逻辑值的电路 ( 如 TTL 和 MOS 门电路 )连接起来;或者用来驱动集成电路本身驱动不了的大电流及大功率负载;也可用来切断干扰源通道,增强抗干扰能力。

接口电路有系统接口 ( 如 PIO 、 SIO 、 CT

C 等 ) 和器件之间的接口。下面只介绍几种用于器件之间的简单接口。

时序电路的分析 计算机科学系 刘敏钰教授 119 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 119

(1) TTL→CMOS 门的接口。凡是和 TTL 门兼容的 CM

OS 门 ( 如 74HCT×× 和 74ACT×× 系列 CMOS 门 ) 可以和TTL 的输出端连接,不必外加元器件。 当 CMOS 门的逻辑电平与 TTL 不同,但两者的电源电压相近时,可以在 TTL 门的输出端和 UDD 之间接入上拉电阻R1 , 以提高 TTL 门的输出高电平。如图 2 - 32(a) 所示,这样当 TTL 与非门有一个输入端接低电平时,则如图 2-13

(a) 中 TTL 的两个输出管 V4 和 V5 均截止, 流过 R1 的电流很小,使其输出高电平接近 UDD ,满足CMOS 门的要求。 R1 的取值方法和 OC 门的上拉电阻的取值方法相同 (约在几百欧到几千欧之间 ) 。

时序电路的分析 计算机科学系 刘敏钰教授 120 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 120

当 UDD>>UCC 时,上述方法不再适用。否则,会使 V

5 截止 (TTL 输出 UOH) 时,所承受反压 (约为 UDD)超过其耐压极限而损坏。解决的方法之一是在 TTL 门和 CM

OS 门之间插入一级 OC 门,图 2 - 32(b) 所示 (OC 门的输出管均采用高反压管, 其耐压可高达 30 V 以上 ) 。另一种方法是采用专用于 TTL 门和 CMOS 门之间的电平移动器,如 CC40109 。它实际上是一个带电平偏移电路的 C

MOS 门电路。它有两个供电端钮 UCC 和 UDD 。若把 UCC

端接 TTL 的电源,把 UDD端接 CMOS 的电源, 则它能接收 TTL 的输出电平,而向后级 CMOS 门输出合适的 U

IH 和 UIL 。应用电路如图 2 - 32(c) 所示。

时序电路的分析 计算机科学系 刘敏钰教授 121 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 121

(a )

(b )

TTL

1 ¡Ý1

CMOS

R1

10 k

£«U CC (5V )£«U

D D(8 ¡« 18 V )

&U I1U

I2U

O

(c )

U CCU DD

&1

CMOSTTL

电平移动器

R 13.3 k

£«U CC (5 V ) £«U D D (8 ¡« 18 V )

CC40109

TTL

¡Ý1

CMOS

R 110 k

£«UCC

(5 V )

U O

&U I

£«UD D

¡Ö UCC

图 2 – 32 TTL→CMOS 的接口

时序电路的分析 计算机科学系 刘敏钰教授 122 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 122

(2) CMOS 门的 UOH≈UDD , UOL≈0 V ,满足 TTL 门

对 UIH 和 UIL 的逻辑要求。但是当 UDD 太高时,有可能使

TTL损坏。 另外,虽然 CMOS 门的拉电流 IOH近似等于

灌电流 IOL ,但是因为 TTL 门的 IIS>>IIH ,所以,当用 C

MOS 门驱动 TTL 门时, 将无法保证 CMOS 门输出符合

规定的低电平。 ( 因为 CMOS 门输出 UOL 时, TTL 门的

IIS 将灌入 CMOS 门输出端,使 UOL升高。 ) 因此接口电

路既要把输出高电平降低到 TTL 门所允许的范围内,又要对 TTL 门有足够大的驱动电流。具体实现方法如下:

时序电路的分析 计算机科学系 刘敏钰教授 123 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 123

方法一:采用专用的 CMOS→TTL 电平转换器,

如 CC4049(六反相器 ) 或 CC4050(六缓冲器 ) 。由于

它们的输入保护电路特殊,因而允许输入电压高于电

源电压 UDD 。例如,当 UDD=5V 时,其输入端所允许

输入的最高电压为 15 V , 而其输出电平在 TTL 的 UI

H 和 UIL 的允许范围内。应用电路如图 2 - 33(a) 所示。

时序电路的分析 计算机科学系 刘敏钰教授 124 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 124

(c )

(a ) (b )

UDD

&

TTL

1/6CC4050

&

CMOS

£«U D D (5 ¡« 18 V ) £«UCC

(5 V )

TTL

& ¡Ý1

CMOS

Rx

£«U CC (£«5 V )

&

CMOS

£«UD D

(5 ¡« 18 V )

CMOSR 2

£«U CC (5 V )

& &

£«UD D

(5 ¡« 18 V )

10 k

10 k

R 33.3 k R 1

图 2 – 33 CMOS→TTL 的接口

时序电路的分析 计算机科学系 刘敏钰教授 125 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 125

方法二:采用 CMOS漏极开路门 (OD 门 ) ,如 C

C40107 。 当 UDD=5 V 时,其 IOL≥16mA , 应用电路

如图 2 - 33(b) 所示。

方法三: 用分立三极管开关。应用电路如图 2-33

(c) 所示。

方法四: 将同一封装内的门电路并联应用,以加大驱动能力。

时序电路的分析 计算机科学系 刘敏钰教授 126 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 126

TTL(CMOS)→ 大电流负载的接口。大电流负载通常对输入电平的要求很宽松,但要求有足够大的驱动电流。最常见的大电流负载有继电器、脉冲变压器、显示器、指示灯、可关断可控硅等。普通门电路很难驱动这类负载,常用的方法有如下几种:

方法一:在普通门电路和大电流负载间,接入和普通门电路类型相同的功率门 ( 也叫驱动门 ) 。有些功率门的驱动电流可达几百毫安。

方法二:利用 OC 门或 OD 门 (CMOS漏极开路门 ) 做接口。 把OC 门或 OD 门的输入端与普通门的输出端相连,把大电流负载接在上拉电阻的位置上。

时序电路的分析 计算机科学系 刘敏钰教授 127 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 127

方法三:用分立的三极管或 MOS管做接口电路

来实现电流扩展,为充分发挥前级门的潜力,应将拉

电流负载变成灌电流负载,因为大多数逻辑门的灌电

流能力比拉电流能力强,例如 TTL 门 74×× 系列的 IOH

=0.4 mA , IOL=16 mA 。

图 2-34 是一个用普通 TTL 门接入三极管来驱动

大电流负载的电路。

时序电路的分析 计算机科学系 刘敏钰教授 128 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 128

&U I1

200 mA

U I2

R 1

VD 1 VD 2 R 2

i B

负载

£«5 V £«24 V

I C

TTL

图 2 – 34 用三极管实现电流扩展

时序电路的分析 计算机科学系 刘敏钰教授 129 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 129

设负载的工作电流 IC=200mA ,三极管的 β=20 ,则三极管的基极电流 iB=10mA 。若不接 R1 、 VD1 、 VD2 ,而把三极管的基极直接接 T

TL 门的输出端,则 iB 对 TTL 门构成拉电流, 其值已远远超过 TTL 门拉电流的允许值,使其 UOH 大大降低,以致无法工作在开关状态,甚至会因超过允许功耗而损坏。接入 R1 、 VD 1、 VD 2后,当 TTL 门输出 UOH 时, VD1截止, iB 由 +5V→R1→VD2 的支路提供,对 TTL 门不产生影响。当 TTL 门输出 UOL 时,由 +5V→R1→VD1 的支路向 TTL 门灌入电流,只要 R1 取值合适,就可以使灌电流保持在 TTL 门所允许的范围内。该电路的工作过程如下:当两个输入端之一为低电平时, TT

L 门输出 UOH , VD1截止,直流电源 +5 V ,经 R1 和 VD2使三极管导通,负载进入工作状态。当两个输入端全是高电平时, TTL 门输出 UO

L ,使 VD2 和三极管均截止,负载停止工作。

时序电路的分析 计算机科学系 刘敏钰教授 130 基本逻辑运算及集成逻辑门 陕西教育学院计算机科学系 130

若门电路是 CMOS 门,则应把双极性三极管换成

MOS管。由于 CMOS 门的拉电流和灌电流基本相等,

故 R1 、 VD1 、 VD2 应当去掉,但必须在门的输出端和

MOS管的栅极间串接一个电阻,并且保留 R 2。