第五章 时序逻辑电路

-

Upload

brynne-zamora -

Category

Documents

-

view

80 -

download

0

description

Transcript of 第五章 时序逻辑电路

第五章 时序逻辑电路

5.2 常用时序逻辑5.3 时序逻辑电路的设计方法 本章小结

5.1 时序逻辑电路的分析方法

第五章 时序逻辑电路

例如:拉线开关有记忆、而计算机的复位开关就没有记忆若时序电路中所有触发器在同一时钟作用下使能,

叫做同步时序电路, 否则就是异步时序电路

组合逻辑电路(第三章内容)—— 无记忆

时序逻辑电路 —— 有记忆

任何一个时刻的输出,仅取决于当时的输入,而与电路以前的状态无关

任何一个时刻的输出,不仅与当时的输入有关,还与电路以前的状态有关

分析时序逻辑电路的一般步骤5.1 时序逻辑电路的分析方法

1 .由逻辑图写出下列方程

时钟方程 输出方程驱动方程

2 .将驱动方程代入相应触发器的特性方程,求状态方程

3 .根据状态方程和输出方程,设定初态 , 计算状态转换表,画出状态转换图、时序图 (在异步电路中应注意使能条件)

4 .根据状态转换表或状态转换图,说明给定时序逻辑电路的逻辑功能

一、同步时序逻辑电路的分析

n01 QMJ

{ {n10 QMJ

1K0 1K1

例 5-1 :试分析下图所示时序逻辑电路

( 2 )写输出方程:本例除 Q1 、 Q0 外没有其他输出,无输出方程

解:该电路为同步时序逻辑电路,时钟方程可以不写

( 1 )写出驱动方程:

1

=1

F1

J

C1

K

Q

Q

=1

F0

J

C1

K

Q

Q 1

Q1Q0

M

CP

( 3 )求状态方程(即各触发器的次态)

( 4 )状态转换表及状态图

n1

n0

n11

n11

1n1 Q)Q(MQKQJQ n

10 QMJ

n0

n1

n00

n00

1n0 Q)Q(MQKQJQ

n0

n1

1n0 QQQ 1K0

n0

n1

1n0 QQQ

1K1 n01 QMJ

或: M=0时

M=1 时n0

n1

1n1 QQQ

n0

n1

1n1 QQQ

n1Q n

0Q 1n0Q 1n

1Q

0 0 0 0 1

M

0 0 1 1 0 0 1 0 0 0 0 1 1 0 0

1 1 0 0 1

1 0 1 0 0

1 0 0 1 0

1 1 1 0 0

Q1Q0

11

M=0 时

M=1 时

00 01 10

10 01 00 11

nn1n QKQJQ

该电路是一个能自启动的可逆 3 进制计数器

11 00 01 10

10 01 00 11

M=0 时

M=1 时

( 5 )给定时序逻辑电路的逻辑功能

无效状态无效状态

自启动

自启动

有效循环

有效循环

M=0 3 进制加法计数器,能自启动

M=1 3 进制减法计数器,能自启动

例 5-2 :试分析如图所示的时序逻辑电路

解:( 1 )写出驱动方程: n

011 QKJ 1KJ 00 n0

n122 QQKJ

n0

n00

n00

1n0 QQKQJQ

n0

n1

n0

n1

n11

n11

1n1 QQQQQKQJQ

n0

n1

n2

n0

n1

n2

n22

n22

1n2 QQQQQQQKQJQ

( 2 )写输出方程:

n0

n1

n2 QQQC

( 3 )求状态方程:

{

F2

J

C1

K

Q

Q

F0

J

C1

K

Q

Q

Q2 Q0

J

C1

K

Q

Q

F1

Q1

&

1

C

CP

CP Cn0

n1

n2 QQQ 1n

01n

11n

2 QQQ

( 4 )状态转换表、状态转换图

1 0 0 0 0 0 1 0

000/C 001/0

010/0

011

101 100110111

1n0

1n1

1n2 QQQ

2 0 0 1 0 1 0 03 0 1 0 0 1 1 04 0 1 1 1 0 0 05 1 0 0 1 0 1 06 1 0 1 1 1 0 07 1 1 0 1 1 1 08 1 1 1 0 0 0 1

( 5 )时序图

CP

Q0

1 2 3 4 5 6 7 8

Q1

Q2

C

000/0 001/0 010/0 011/0 100/0 101/0 110/0 111/1 000/0

Q Q Q /C012

n0

n1

n2 QQQ

n0

1n0 QQ

n0

n1

n0

n1

1n1 QQQQQ

/0

/0

/0/0/0

/1

n0

n1

n2

n0

n1

n2

1n2 QQQQQQQ

n0

n1

n2 QQQC

( 6 )电路的功能

CP

Q0

1 2 3 4 5 6 7 8

Q1

Q2

C

000/0 001/0 010/0 011/0 100/0 101/0 110/0 111/1 000/0

Q Q Q /C012

同步八进制( 3 位二进制)加法计数器

000 001/0

010/0

011

101 100110111

/0

/0/0/0

/1

进位信号

Q0 对 CP 二分频

C 对 CP 八分频

Q2 对 CP 八分频

Q1 对 CP 四分频

/0

思考时钟的时针、分针、秒针之间的关系和计数器的关系

CP1=Q0

例 5-3 :试分析如图所示的时序逻辑电路

解:该电路为异步时序逻辑电路

( 1 )时钟方程

CP0=CP2=C

P

二、异步时序逻辑电路的分析

n20 QJ

1KJ 11

1K0

1K2 n0

n12 QQJ

( 2 )驱动方程

F2

J

C1

K

Q

Q

F0

J

C1

K

Q

Q

Q2 Q0

CP

J

C1

K

Q

Q

F1

Q1

111

( 3 )状态方程n20 QJ

1KJ 11 1K0

1K2 n0

n12 QQJ

n0

n2

1n0 QQQ

n0

n1

n2

n2 QQQQ

n1

1n1 QQ

(4) 状态转换表、状态转换图CP CP2CP1CP0

n0

n1

n2 QQQ 1n

01n

11n

2 QQQ

1 0 0 0 0 0 1 ↓ ↓

( CP0↓ )

( CP2↓ )

( CP1↓ )

000 001

1 0 0 1 0 1 0 ↓ ↓ ↓

010

1 0 1 0 0 1 1 ↓ ↓

011

1 0 1 1 1 0 0 ↓ ↓ ↓

100

1 1 0 0 0 0 0 ↓ ↓

1 0 1 0 1 0 ↓ ↓ ↓ 1 1 0 0 1 0 ↓ ↓ 1 1 1 0 0 0 ↓ ↓ ↓

111 110 101

无效状态

有效循环无效状态

nn1n QKQJQ

( 6)结论:能自启动得异步五进制加法计数器

( 5)时序图(设初态为 000 )

Q

Q

Q

CP

000 001 010 011 100 000

0

1

2

1 2 3 4 5

(一)计数器的基本概念

计数器——对时钟脉冲 CP 计数的电路。

按计数器的内容随 CP 脉冲的增减可分为加法计数器、减法计数器和可逆计数器。

计数器有几个有效状态构成循环(即有效循环),就叫做几进制计数器

按计数器中触发器翻转是否与 CP 脉冲同步分为同步计数器和异步计数器。

一、计数器

5.2 常用时序逻辑电路

(二)中规模集成计数器1 . 74LS90 异步计数器 ( 1 )功能:异步 2-5-10 进制加法计数器

二进制计数器:时钟端 CP1 ,输出端为Q0 ;

五进制计数器:时钟为 CP2 ,输出端为Q3 、 Q2 、 Q1 ,有效状态为位: 000, 001 , 010 , 011 , 100

R0(1) 、 R0(2) ——— 异步清 0 端S9(1) 、 S9(2) ——— 异步置 9 端

如果将 Q0 与 CP2 相连, CP1 作时钟输入端, Q3 ~ Q0 作输出端,则为

8421BCD 码十进制计数器。如果将 Q3与 CP0相连, CP2作时钟输入端

,从高位到低位的输出为 Q0 Q3 Q2 Q1 时,则构成 5421BCD码十进制计

数器

Q3

Q2

Q1

Q0

CP0

CP1

R0(

1)

R0(

2)S9

(1)

S9(2

)

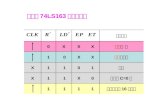

74LS90 的功能表:

注意:清 0 和置 9 信号不得同时有效,更不能同时由有效变为无效

输入 输出CP R0(1) R0(2) S9(1) S9(2) QD QC QB QA

0 0 0 0× 1 1 0 ×

× 1 1 X 0

× 0 X 1 1

× X 0 1 1↓ X 0 X 0

↓ X 0 0 X

↓ 0 X X 0

↓ 0 X 0 X

0 0 0 0

1 0 0 1

1 0 0 1

计数

异步清0

异步置9

Q

Q

Q

CP

A

B

C

R

000 001 010 011 100 101 110 000

1 2 3 4 5 6 7

( 2 ) 74LS90 的应用(以 7 进制为例)

1 CP

R

ABD CQ Q Q Q

(a)µç·

Q0

12

Q1

9

Q2

8

Q3

11

S9(1

)6

S9(2

)7

R0(

1)2

R0(

2)3

CP014

CP11

74LS90

&

输出端的清 0 速度一般是不一致,假设 QC 先回 0 ,清零信号 R 立即消失, QB 、 QA 来不及清零,造成误动作

先接成 10 进制计数器R

0(1)

2

R0(

2)3

S9(1

)6

S9(2

)7

CP114

QA

12

CP21

QB

9

QC

8

QD

11

74LS90

CP

Q Q Q QABCD

再用反馈归零法,接成 7进制计数器

因为是异步清 0的,所以 111 状态并不能保持,称其为过渡状态,实际有效状态为 000 ~ 110

000 001 010 011

100101110111

000 001 010 011

100101110111

过渡状态

清 0 电路的改进

1 2 3 4

A

B

C

D

4321

D

C

B

A

1 G

CP

R

ABD CQ Q Q Q

(a)µç·

Q0

12

Q1

9

Q2

8

Q3

11

S9(1

)6

S9(2

)7

R0(

1)2

R0(

2)3

CP014

CP11

74LS90

2

3 4

1

&G&

G

& G

利用基本 RS 触发器(由 G3 、G4 组成),可将清零信号加宽(第 7 个 CP 的下降沿开始,第 8

个 CP 的上升沿结束),使计数器能可靠清零

改进后的时序图

1 2 3 4

A

B

C

D

4321

D

C

B

A

1CP

R

&

&

&

QA

QB

QC

1 2 3 4

A

B

C

D

4321

D

C

B

A

Q

Q

Q

CP

A

B

C

R

1 2 3 4 5 6 7 8

清 0脉冲被加

宽

清 0 信号 R ,在第 7 个 CP 的下降沿时被置 1 ,第 8 个 CP的上升沿才置 0 ,使计数器能可靠清零

74LS160 、 74LS161 为异步清零 A3

B4

C5

D6

Q0

14

Q1

13

Q2

12

Q3

11

TC

15

P7

T10

CP2

LD

9

R1

2. 同步计数器 74LS160 、 74LS161 、 74LS162 、 74LS163

74LS160 、 74LS162 为十进制计数

-- 同步预置端

TC -- 为进位输出端,

74LS162 、 74LS163 为同步清零

74LS161 、 74LS163 为十六进制( 4 位 2 进制)计数

( 1 )功能同步计数、同步置数管脚完全相同

其中

CP— 计数时钟LD

R -- 同步或异步清 0端

D 、 C 、 B 、 A -- 并行预置数

Q3 、 Q2 、 Q1 、 Q0 – 数据输出端

P 、 T – 使能端

74LS160 、 74LS161 的功能表

P T CPLD 0123 QQQQ0 X X X X X X X X

D B C A

1 0 X X ↑ d c b a

1 1 X 0 X X X X X1 1 0 1 X X X X X1 1 1 1 ↑ X X X X

注 1

0 0 0 0d c b a

计数 注 2

注 1:

注 2:

74LS162 、 74LS163 的功能表

将“ X” 换为“↑”

A3

B4

C5

D6

Q0

14

Q1

13

Q2

12

Q3

11

TC

15

P7

T10

CP2

LD

9

R1

数据输出保持,进位 C置 0

数据输出保持,进位 C也保持

R

1 2 3 4

A

B

C

D

4321

D

C

B

A

013 2Q Q Q Q

CP

&

+5V

A3

B4

C5

D6

Q0

14

Q1

13

Q2

12

Q3

11

TC

15

P7

T10

CP2

LD

9

R1

74LS163

1 2 3 4

A

B

C

D

4321

D

C

B

A

013 2Q Q Q Q

CP&

+5V

A3

B4

C5

D6

Q0

14

Q1

13

Q2

12

Q3

11

TC

15

P7

T10

CP2

LD

9

R1

74LS161

① 反馈归 0 法( 2 )应用

异步清 0 ( 74LS161 ) 同步清 0 ( 74LS163 )

0001 0010 0011 0100

0110 010101111000

0000

10011010

异步清0 ,有过渡状

态

同步清 0

以 74LS161 、 7SLS163 构成十进制计数器为例

注意区别

② 预置数法

1 2 3 4

A

B

C

D

4321

D

C

B

A

013 2Q Q Q Q

CP

+5V

A3

B4

C5

D6

Q0

14

Q1

13

Q2

12

Q3

11

TC

15

P7

T10

CP2

LD

9

R1

U?

74LS160

&

0001 0010

00110100

0000

1 2 3 4

A

B

C

D

4321

D

C

B

A

013 2Q Q Q Q

CP

+5V

A3

B4

C5

D6

Q0

14

Q1

13

Q2

12

Q3

11

TC

15

P7

T10

CP2

LD

9

R1

U?

74LS160

1

0010 0011

01000101

0001

都是五进制,使用的有效状态不同

解:先用两片 74LS161 接成 100 进制(也叫模为 100 )的计数器。例 5-4 用 74LS161 组成 48 进制计数器

1 2 3 4

A

B

C

D

4321

D

C

B

A

CP

2Q

+5V

+5V

A3

B4

C5

D6

Q0

14

Q1

13

Q2

12

Q3

11

TC

15

P7

T10

CP 2

LD

9

R1

74LS161

A3

B4

C5

D6

Q0

14

Q1

13

Q2

12

Q3

11

TC

15

P7

T10

CP 2

LD

9

R1

74LS161

3Q 1Q 0Q 2Q 3Q 1Q 0Q

¸öλʮλ

&

再利用反馈清 0 或预置数法构成 84 进制( 00-83 )计数器。

虽然 CP 同时送到了个位和十位(同步),但只有个位计到 1001 时, TC=1,十位的 T=1 ,在下一个 CP 的上升沿到来时,十位才加 1 计数,个位回到0000

(一) 数据寄存器常用来临时存放数据、指令

一、寄存器

1. 由 D触发器构成的寄存器

只有最简单的存(写入)、取(读出)功能的寄存器称为数据寄存器

由高电平有效的 D 触发器构成的两位数据寄存器。 G1 、 G0 为低电平有效的三态反相器。

1 2 3 4

A

B

C

D

4321

D

C

B

A

D D

Q Q

OE

CP

01

01

1

C1

D

F

1 EN G 0

C1

D

F

1 EN G

1 0

OE

当 CP=1 时,存入数据,

当OE =0 时,输出数据。

=1时,输出为高阻状态,

CP=0 时,保持数据。

2. 8D 数据锁存器 74HC373 、 74HC573

OE LE D Q

功能表符号

1 2 3 4

A

B

C

D

4321

D

C

B

A

D03

Q02

D14

Q15

D27

Q26

D38

Q39

D413 Q4 12

D514

Q515

D617

Q616

D718 Q7 19

OE1

LE11

74HC373

OE1

LE11

1D2

2D3

3D4

4D5

5D6

6D7

7D8

8D9

1Q19

2Q18

3Q17

4Q16

5Q 15

6Q14

7Q13

8Q 12

74HC573

LE – 锁存 – 输出使能

0 1 0 00 0 X 保持1 X X 高阻

0 1 1 1

74HC373 和 74HC573 的功能完全一样,只是管脚不一样。

74HC373 比较常用,如:单片机的地址锁存,但 74HC573 的管脚分布更便于排印刷电路板。

OE

二、移位寄存器在时钟(移位)脉冲作用下寄存器的数据向左移位或向

右移位,具有移位功能的寄存器称作移位寄存器1 .由 D 触发器构成的移位寄存器

1 2 3 4

A

B

C

D

4321

D

C

B

A

210 QQQ

DR

CP

210

Q

Q

D

C1

F

D2

Q

Q

D

C1

F

D2

Q

Q

D

C1

F

D2

DR 是数据输入端,它在 CP 脉冲(移位脉冲)的作用下,输入数据逐个地输入寄存器

状态方程为: R1n

0 DQ n0

1n1 QQ n

11n

2 QQ

1 2 3 4

A

B

C

D

4321

D

C

B

A

DR

CP

1

2

0

Q

Q

Q

1 2 3 4 5 6

R1n

0 DQ

n0

1n1 QQ

n1

1n2 QQ

1 0 1 0 0 0

1 0 1 0 0 01 0 1 0 0

1 0 1 0

上升沿有效

DR 端称为串行输入端, Q2 端称为串行输出端

移位过程:

移位脉冲

串行输入

并行输出

串行输出

移位过程, Q0 、 Q1 、 Q2 的波形相同,依次滞后一个 CP 的周期

在 CP 上升沿时, DR 端数据依次移入寄存器、数据依次右移

2. 双向移位寄存器 74LS194

74LS194 是具有双向移位和并行输入数据的四位移位寄存器

S0 、 S1—— 功能选择端

dR—— 为异步清零端

QDQCQBQA—— 输出端

CP—— 时钟

SR—— 右移串行输入端SL—— 左移串行输入端

DCBA—— 并行输入端dR

1 2 3 4

A

B

C

D

4321

D

C

B

A

Rd

1

S09

S110

CP

11

SR2

A3

QA

15

B4

QB

14

C5

QC

13

D6

SL

7

QD

12

74LS194

CP

S1S0 功能

X 0 X X 清零X 1 0 0 保持↑ 1 0 1 右移 QD 为串行输出↑ 1 1 0 左移 QA 为串行输出

↑ 1 1 1 并行输入

功能表

逻辑符号

QD—— 右移串行输出端

QA—— 左移串行输出端

0 0 0 0

D C B A

QD QC QB QA

D C B A

QD QC QB QA

DR

D C B A

QD QC QB QA

DL

dRCP

S1S0 功能

X 0 X X 清零X 1 0 0 保持↑ 1 0 1 右移↑ 1 1 0 左移↑ 1 1 1 并行输入

功能表

3.8 位移位寄存器 74LS164

1 2 3 4

A

B

C

D

4321

D

C

B

A

Rd

9

CP8

A1

B2

QA

3Q

B4

QC

5Q

D6

QE

10Q

F11

QG

12Q

H13

74LS164

逻辑符号

功能表

CP

nG

1nH

nB

1nC

nA

1nB

1nA QQQQ,QQAB,Q

功能

X 0 异步清零↑ 1

74LS164 是一个 8 位移位寄存器A 、 B—— 串行输入数据端 —— 异步清零

端CP—— 移位脉冲输入端QH ~ QA 为输出端

dR

dR

设初态( QH ~ QA )

为 00000000

QH 通过反相器 G 反馈到串行输入端 A 、 B

1 2 3 4

A

B

C

D

4321

D

C

B

A

1 G

CP

Rd

9

CP8

A1

B2

QA

3Q

B4

QC

5Q

D6

QE

10Q

F11

QG

12Q

H13

74LS164

+5V

1

0 0 0 0 0 0 00

在 CP 上升沿的作用下其状态转换过程为:

由 74LS164 构成扭环计数器

00000000→0000001→00000011→00000111→00001111→……→11111111→11111110→11111100→……→10000000→00000000 。由 16 个状态构成一个循环,称它为 16 进制扭环形计数器。

逻辑符号CD4017 是十进制计数器 / 脉冲分配器

RESET—— 异步清零输入

CLK—— 时钟输入

—— 时钟 / 使能输入

Cout—— 进位输出

Q0 ~ Q9—— 脉冲输出

EN/CLK

EN/CLK

EN/CLK

三、顺序脉冲发生器

=0 时, CLK 上升沿有效

EN/CLK

当 CLK=1 时,在 CLK (或

1 2 3 4

A

B

C

D

4321

D

C

B

A

CL

K14

CL

K/E

N13

RE

SET

15

Q0

3Q

12

Q2

4Q

37

Q4

10Q

51

Q6

5Q

76

Q8

9Q

911

Cou

t12

CD4017

当下降沿有效) 有效沿的作用下

Q0 ~ Q9 依次输出一个正脉冲

输出端依次输出脉冲的电路称为顺序脉冲发生器,或称脉冲分配器,他它也是周期性的工作,实际上也是一个计数器

1 2 3 4

A

B

C

D

4321

D

C

B

A

CLK

CLK/EN

RESET

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q8

Q9

Cout

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

异步清0

这个↑不起作用

时序图

74LS163 接成了 8 进制计数器,其输出 QC、 QB 、 QA 分别接到译码器 74LS138 的A2 、 A1 、 A0

1 2 3 4

A

B

C

D

4321

D

C

B

A

&

CP

R

200

A0

1

A1

2

A2

3

S16

S24

S35

Y0

15

Y1

14

Y2

13

Y3

12

Y4

11

Y5

10

Y6

9

Y7

7

74LS138

R1

LD

9

T10

P7

CP2

C15

A3

QA

14

B4

QB

13

C5

QC

12

D6

QD

11

74LS163

+5V

+5V

+5VVB0 VB1 VB2 VB3 VB4 VB5 VB6 VB7

右图是由计数器 74LS163和译码器 74LS138 组成的顺序脉冲发生器

74LS138 的输出依次输出低电平(即顺序输出负脉冲),发光二极管 VB0 ~ VB7依次点亮一个 CP周期。

设计的任务就是根据设计的要求,选用基本逻辑单元电路或数字部件,通过逻辑设计,画出满足要求的时序逻辑电路。

时序逻辑电路的设计,是分析的逆过程。

值得一提的是,由于大、中规模集成电路的广泛采用,利用触发器来组成 N 进制计数器的方法已经不大采用了。

计数器是一种简单而又典型的时序逻辑电路,它的设计具有普遍性。

5.3 时序逻辑电路的设计方法

例 5-3 :试用 JK 触发器设计一个同步六进制加法计数器。

解:设计步骤如下

(1)确定触发器个数 n

按照 2n≥N ,来确定

(2)选择状态编码、并画出状态转换图本例有六个状态: S0 ~ S5 ,可设 S0=000 ; S1=001 ;S2=010 ; S3=011 ; S4=100 ; S5=101 。

N 也称为计数长度, N 也称为计数器的模本例 N=6 ,现取 n=3,用3个触发

器

N 为计数器状态数,

110 、 111 为无效状态

因为是六进制加法计数,状态 S5→S0 时,产生进位: C=1

状态转换图

S0

000S1

001S2

010

S3

011S4

100S5

101

/0 /0

/0/0/0

/1

/C

(3) 求状态方程、输出方程状态方程即计数器的次态方程

卡诺图n2Q

1n1Q

001/0 010/0 100/0 011/0

XXX/0XXX/0000/0101/0

C/QQQ 1n0

1n1

1n2

1n2Q

1n0Q n

0n1 QQ

00 01 11 10

0

1

卡诺图n2Q

0 0 1 0

XX01

n0

n1 QQ

00 01 11 10

0

1

卡诺图

n2Q

0 1 0 1

XX00

n0

n1 QQ

00 01 11 10

0

1

卡诺图n2Q

1 0 0 1

XX01

n0

n1 QQ

00 01 11 10

0

1

1n1Q

1n2Q

1n0Q

n2Q

n0

n1 QQ

00 01 11 10

0

1

0 0 1 0

1 0 X X

C

n2

n0

n2

n0

n1

1n2 QQQQQQ

n1

n0

n1

n0

n2

1n1 QQQQQQ

n0

n2QQC

n2Q

n0

n1 QQ

00 01 11 10

0

1

0 1 0 1

0 0 X X

n2Q

n0

n1 QQ

00 01 11 10

0

1

1 0 0 1

1 0 X X

n2Q

n0

n1 QQ

00 01 11 10

0

1

0 0 0 0

0 1 X X

并不是最简形式,是为了和 JK 触发器的特性方程进行比较,得到驱动方程

为了和 JK 触发器的特性方程进行比较,得到的驱动方程

n0

n0

n0

1n0 Q1Q1QQ

输出方程

n2

n0

n2

n0

n1

1n2 QQQQQQ

nn1n QKQJQ

输出方程:

n0

n2QQC

(4) 求驱动方程

n0

n0

n0

1n0 Q1Q1QQ

n0

n12 QQJ

n02 QK

n0

n21 QQJ n01 QK

1J0 1K0

n1

n0

n1

n0

n2

1n1 QQQQQQ

JK 触发器的特性方程

将状态方程和 JK 触发器的特性方程进行比较,即可求得驱动方程

(5) 根据驱动方程和输出方程画逻辑图

n0

n12 QQJ

n02 QK

n0

n21 QQJ n01 QK

1J0 1K0

1 2 3 4

A

B

C

D

4321

D

C

B

A

1

Q Q Q

CP

C

012

012

J

C1

K

Q

Q

F

J

C1

K

Q

Q

F

J

C1

K

Q

Q

F

&

n0

n2QQC

计数器可以从无效状态进入有效状态,所以该计数器可以自启动。

(6)检查能否自启动

n2

n0

n2

n0

n1

1n2 QQQQQQ

n1

n0

n1

n0

n2

1n1 QQQQQQ S0

000S1

001S2

010

S3

011S4

100S5

101

/0 /0

/0/0/1

n0

1n0 QQ

将两个无效状态: 110 、111 分别代入状态方程和输出方程,计算

111 110

n0

n2QQC

时序电路结构特点:电路中一定有触发器。时序电路逻辑功能特点:有记忆功能。时序电路逻辑功能的描述方法:

时序图:适用于时序电路的调试、故障分析。

次态方程(注意使能条件特别是对于异步计数器)和输出方程:它是分析、设计时序电路所必需的描述方法。状态转换表和状态转换图:非常直观地反映了时序电路工作的全过程和逻辑功能

常见的时序逻辑电路有:计数器、寄存器、顺序脉冲发生器等,他们都是在时钟脉冲作用下工作的本章系统地介绍了时序电路的分析方法和设计方法,重点介绍了典型中规模计数器、寄存器、顺序脉冲发生器的功能和应用。

本章小结