时序逻辑电路 - 分析

description

Transcript of 时序逻辑电路 - 分析

1

时序逻辑电路 - 分析

2

§1 概 述组合逻辑电路:如译码器,全加器,数据选择器时序逻辑电路:(简称时序电路)任意时刻的输出信号不仅取决于该时刻的输入信号,而且还取决于电路原来的状态,即与以前的输入信号有关。 如触发器,寄存器,计数器和移位寄存器等

3

反馈

输出方程驱动方程状态方程

4

同步时序电路:所有存储电路中存储单元状态的变化都是在同一时钟信号操作下同时发生的。异步时序电路:存储单元状态的变化不是同时发生的。可能有公共的时钟信号,也可能没有公共的时钟信号。米利( Mealy )型电路:某时刻的输出是该时刻的输入和电路状态的函数穆尔( Moore )型电路:某时刻的输出仅是该时刻电路状态的函数,与该时刻的输入无关,如同步计数器。( *CP 不是输入)

5

§2 时序逻辑电路的分析根据其逻辑图分析出该电路实现的功能

分析步骤1 、从给定的逻辑图中写出每个触发器的驱动方程(即写出存储电路中每个触发器输入信号的逻辑表达式);2 、将驱动方程代入触发器的特性方程,得出每个触发器的状态方程;3 、根据逻辑电路写出电路的输出方程;4 、画状态转换表 / 状态转换图 / 时序图。

6

同步 nnn QKQJQ 1

7

8

异步Q0 下降沿

9

§3 寄存器

时 序逻辑电路寄存器和移位寄存器

计数器

10

Q3 Q2 Q1 Q0

& & & &

Q QD

Q QD

Q QD

Q QD

A0A1A2A3

CLR

取数脉冲接收脉冲( CP )

寄存器:存放多位二值代码。每个触发器存放一位二进制数或一个逻辑变量,由 n 个触发器构成的寄存器可存放 n 位二进制数或 n 个逻辑变量的值。

四位寄存器

寄存器

11

四位寄存器

12

1 2 3 4 5 6 7 1098

14 13 12 11151617181920

1Q 1D 2D 2Q 3Q 3D 4D 4Q GND输出控制

时钟VCC 5D6D7D8D 5Q6Q7Q8Q

7 4 L S 3 7 4

低电平有效

正边沿触发

八 D 寄存器 :三态输出共输出控制共时钟

13

移位寄存器 所谓“移位”,就是将寄存器所存各位数据,在每个移位脉冲的作用下,向左或向右移动一位。根据移位方向,常把它分成三种:

寄存器左移

(a)

寄存器右移

(b)

寄存器双向移位

(c)

14

1011

15

SD

Q

Q D

Q

Q D

Q

Q D

Q

Q D

& & & &

A0A1A2A3

RD

CLR

LOAD

移位脉冲CP

0串行输出

数 据 预 置

3 2 1 0

存数脉冲

清零脉冲

四位并入 - 串出的左移寄存器

16

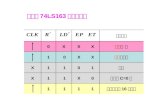

R— 右移串行输入L— 左移串行输入A 、 B 、 C 、 D

— 并行输入

VCC QA QB QC QD S1 S0CP

QA QB QC QD CP S1

S0CLRLDCBAR

A B C DR LCLR GND

74LS194

1516 14 13 12 11 10 9

1 2 3 4 5 6 7 8

01111

0 00 11 01 1

直接清零保 持右移 ( 从 QA 向 QD 移动 )左移 ( 从 QD 向 QA 移动 ) 并行输入

CLR CP S1 S0 功 能

17

&

G1

S0

S1

CP1

QA1QB1QC1QD1 S0

S1

CP2

QA2QB2QC2QD2

R1 R2A1 B1 C1 D1 A2 B2 C2 D2

D0 D1 D2 D3 D4 D5 D6

+5V

+5V

CP

启动脉冲

移位脉冲

&

G2

串行输出

并行输入

74LS194 (1) 74LS194 (2)

例:数据传送方式变换电路

18

寄存器各输出端状态QA1QB1QC1QD1QA2QB2QC2 QD2

寄存器工作方式0 D0 D1 D2 D3 D4 D5 D6 1 0 D0 D1 D2 D3 D4 D5 1 1 0 D0 D1 D2 D3 D4 1 1 1 0 D0 D1 D2 D3 1 1 1 1 0 D0 D1 D2 1 1 1 1 1 0 D0 D1 1 1 1 1 1 1 0 D0

CP

并行输入 ( S1S0=11)

并行输入 ( S1S0=11)

右移 ( S1S0=01)

右移 ( S1S0=01)

右移 ( S1S0=01)

右移 ( S1S0=01)右移 ( S1S0=01)

在电路中,“右移输入”端接 + 5V 。

19

集成移位寄存器简介并行输入-并行输出 ( 双向 )74LS194 、 74LS198 、 74LS299 等并行输入-串行输出 74LS165 、 74LS166 等串行输入-并行输出 74LS164 等串行输入-串行输出 74LS91 等

20

§4 计数器4.1 计数器的功能和分类

1. 计数器的作用记忆输入脉冲的个数;用于定时、分频、产生节拍脉冲及进行数字运算等等。

2. 计数器的分类按工作方式分:同步计数器和异步计数器。按功能分:加法计数器、减法计数器和可逆计数器。按计数器的计数容量 ( 或称模数 ) 来分:各种不同的计数器,如二进制计数器、十进制计数器、二-十进制计数器等等。

21

4.2 异步计数器异步计数器的特点:在异步计数器内部,有的触发器直接受输入计数脉冲控制,有的触发器则是把其它触发器的输出信号作为自己的时钟脉冲,因此各个触发器状态变换的时间先后不一,故被称为“ 异步计数器 ”。

有异步二进制计数器和异步十进制计数器,常用的异步二进制计数器有 4 位、 7 位、 12 和 14 位。

22

nnnn QQKQJQ 1

加法

分频

23

减法

简单,速度慢。

pdcNtf 1max

24

4.3 同步计数器同步计数器的特点:在同步计数器内部,各个触发器都受同一时钟脉冲——输入计数脉冲的控制,因此,它们状态的更新几乎是同时的,故被称为 “ 同步计数器 ”。

二进制加法运算规则:对一个多位二进制而言,最低位每次加 1 都改变状态,而第 i 位(除最低位外)仅有当以下各位皆为 1 时才改变状态

25

nnn QKQJQ 1

pdgpdc ttf

1max

26

多功能计数器

27

10010000

用模 16 构成模 10

28

半导体存储器半导体存储器是一种能存储大量二值信息(或称为二值的数据)的半导体器件。随机存取存储器( Random Access Memory, RAM )只读存储器( Read Only Memory, ROM )

29

可编程逻辑器件简介Programmable Logic Device ( PLD ), (V)LSI ,通过编程来实现逻辑功能。FPLA, PAL, GAL, FPGA, ISP…功能密度高、系统可靠性高、设计灵活方便、开发周期短EDA ,开发系统, VHDL ,下载…

30

作业10-910-15