数字电路 与 逻辑设计

-

Upload

olga-sawyer -

Category

Documents

-

view

115 -

download

8

description

Transcript of 数字电路 与 逻辑设计

数字电路数字电路

与与 逻辑设计逻辑设计

2004 - 2011

第四章 组合逻辑电路

1. 组合逻辑电路概述组合逻辑电路概述 1. 组合逻辑电路概述组合逻辑电路概述

2. 组合逻辑电路分析组合逻辑电路分析 2. 组合逻辑电路分析组合逻辑电路分析

3. 组合逻辑电路设计组合逻辑电路设计 3. 组合逻辑电路设计组合逻辑电路设计

4. 组合逻辑电路的竞争冒险组合逻辑电路的竞争冒险 4. 组合逻辑电路的竞争冒险组合逻辑电路的竞争冒险

5. 常用的组合逻辑电路常用的组合逻辑电路 5. 常用的组合逻辑电路常用的组合逻辑电路

常用组合逻辑电路常用组合逻辑电路

某些组合逻辑电路具有相对独立的功能,这些电路比较普遍地应用于多种逻辑电路中。

为了方便电路设计,降低产品成本,这些电路被封装为标准化的独立集成电路芯片。

典型的电路 编码器 ■ 译码器 ■ 加法器 数据分配器 ■ 数据选择器

编码器 编码器 (实现编码操作的电路)

数字逻辑电路是二值电路,信号都是以高、低电平的形式给出。

编码器的逻辑功能就是把输入的每一个高、低电平信号编成一个对应的二进制代码。

常用的编码器分为普通编码器和优先编码器两类。 普通编码器

任何时刻只允许输入一个编码信号,否则输出将发生混乱。 优先编码器

允许同时输入两个以上编码信号。在设计优先编码器时已经将所有的输入信号按优先顺序排队,当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。

普通编码器普通编码器 3 位 8 线二进制编码器 任何时刻只允许输入一个编码信号,否则输出将发生混乱。

真值表输入 输出

I0

I1

I2

I3

I4

I5

I6

I7

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 0 0

0 0 1

Y2 Y1 Y0

I 0-7 为信号输入端,当某一输入端信号为 1 时,其它输入端为 0 。

753175310

763276321

765476542

IIIIIIIIY

IIIIIIIIY

IIIIIIIIY

逻辑表达式

逻辑图

普通编码器 普通编码器 (( 33 位位 88 线二进制编码器线二进制编码器))

允许同时输入两个以上编码信号。优先级别高的信号排斥级别低的信号,具有单方面排斥的特性。

优先编码器优先编码器(( 33 位位 88 线二进制优先编码器线二进制优先编码器))

74LS148 芯片引脚图

芯片功能: 将 8 条数据线( IN0 — IN7 )进行 3 线

二进制优先编码,即对最高位数据线进行译码。IN0 — IN7 :编码输入端(低电平有效)

S :选通输入端(低电平有效)Y0 — Y2 :编码输出端(低电平有效)

YEX :扩展端(低电平有效)

YS :选通输出端(低电平有效)

优先编码器优先编码器(( 33 位位 88 线二进制优先编码器线二进制优先编码器))

根据电路逻辑结构,可写出

如下逻辑关系式:

优先编码器优先编码器(( 33 位位 88 线二进制优先编码器线二进制优先编码器))

上表中的 “ ×” 表示输入信号 “ 1” 、“ 0” 均可。

二 二 ~ ~ 十进制优先编码器十进制优先编码器

根据电路逻辑结构,可写

出如下逻辑关系式:

二 二 ~ ~ 十进制优先编码器十进制优先编码器

代表十进制数数字的输入端低电平有效,优先级依次为 9 - 0

输出结果为反码形式。

译码器译码器(把一种代码转换为另一种代码的电路。)(把一种代码转换为另一种代码的电路。)

把代码状态的特定含义翻译出来的过程称为把代码状态的特定含义翻译出来的过程称为译码译码。。

实现译码操作的电路称为实现译码操作的电路称为译码器译码器。。 译码是编码的反操作。译码是编码的反操作。 常用的译码器电路:常用的译码器电路: 二进制译码器 二进制译码器 二二 -- 十进制译码器十进制译码器 显示译码器显示译码器

二进制译码器二进制译码器 设二进制译码器的输入端为 n 个,则输出端为 2n 个,且对应于输入代

码的每一种状态, 2n 个输出中只有一个为 1 (或为 0 ),其余全为 0(或为 1 )。

二进制译码器可以译出输入变量的全部状态,故又称为变量译码器。

输入: 3 位二进制代码 输出: 8 个互斥的信号

3 线 - 8 线 译码器

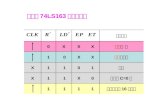

3-83-8 译码器译码器 74LS138 74LS138 (( 与非门电路组成与非门电路组成 ))

0127

0126

0125

0124

0123

0122

0121

0120

AAAY

AAAY

AAAY

AAAY

AAAY

AAAY

AAAY

AAAY

3-83-8 译码器译码器 74LS138 74LS138

3-83-8 译码器译码器 74LS138 74LS138 组合应用组合应用

4-16 4-16 译码器译码器

例题 例题 用 3-8 译码器及与非门实现函数 F=AB+AC+BC

7653 mmmmABCCABCBABCABCACABF

765376537653 yyyymmmmmmmmFF

C B A

数值比较器数值比较器

用来完成两个二进制数的大小比较的逻辑电路称为数值比较器,简称比较器。

1 位数值比较器 设 A > B 时, L1 = 1 ; A < B 时, L2 = 1 ;A = B 时, L3 = 1 。 得 1 位数值比较器的真值表。

BABAABBAL

BAL

BAL

3

2

1逻辑表达式

逻辑图

1 位数值比较器

数据分配器数据分配器

在数据传送时,根据需要把数据传送到指定的数据通道中,实现此功能的电路,称为数据分配器。

A1 A0 Y0-Y3

0 0 Y0=D 0 1 Y1=D 1 0 Y2=D 1 1 Y3=D

数据分配器数据分配器

数据选择器数据选择器

在数据传送时,把多路数据传送到同一数据通道中,实现此功能的电路,称为数据选择器。

A1 A0 Y

-----------------

0 0 D0

0 1 D1

1 0 D2

1 1 D3

数据选择器数据选择器

74LS151 是常用的数据选择器集成电路芯片,可实现 8 – 1 数据选择功能。

数据选择器数据选择器

D0 - D7 :数据输入端A 、 B 、 C :数据输入地址选择控制G :输入使能端Y :同相输出端W :反相输出端

数据选择器数据选择器

)7,6,5,3,1,0(F

)7,6,5,3(F

半加器

能对两个 1 位二进制数进行相加而求得和及进位的逻辑电路称为半加器。

半加器真值表

Ai Bi Si Ci

0 0

0 1

1 0

1 1

0 0

1 0

1 0

0 1

iii

iiiiiii

BAC

BABABAS

=1

&

Ai

BiSi

Ci

Ai

Bi

Si

Ci

∑CO

半加器符号

半加器电路图

加数本位之和

进位值

加法器加法器

全加器 能对两个 1 位二进制数进行相加并考虑低位来的进位,

即相当于 3 个 1 位二进制数相加,求得和及进位的逻辑电路称为全加器。

Ai Bi Ci-1 Si Ci

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 0

1 0

1 0

0 1

1 0

0 1

0 1

1 1

Ai 、 Bi :加数,

Ci-1 :低位来的进位,

Si :本位的和,

Ci :向高位的进位。

11 iiiiiii CBCABAC

1111 iiiiiiiiiiiii CBACBACBACBAS

Si Ci

1 1 1

Ai Bi Ci-1

& &

& & & & & & &

用与门实现全加器

iiiii

iiiiiiiiiiiiiiiii

BACBA

BACBABABACBACBABAmmC

1

11153

)(

)(

1

111111

11117421

)()()()(

iii

iiiiiiiiiiiiiiii

iiiiiiiiiiiii

CBA

CBACBACBCBACBCBA

CBACBACBACBAmmmmS

全加器

全加器