集成组合逻辑电路 功能介绍

Click here to load reader

description

Transcript of 集成组合逻辑电路 功能介绍

集成组合逻辑电路

功能介绍

译码器译码器类 别 品 种 代 号

双 2 线 – 4 线译码器 / 多路分配器

139 155 156 239

双 2 线 – 4 线译码器3 线 – 8 线译码器 / 多路分配器 ( 地址锁存 )3 线 – 8 线译码器 / 多路分配器4 线 – 16 线译码器 / 多路分配器4 线 – 10 线译码器

显示译码器( OC )BCD – 十进制译码器 / 驱动器BCD – 七段译码器 / 驱动器注:对有下划线的型号,提供了真值表,其它型号可参照。

539 4555 4556 14555 14556

131 137 237

538138 238

154 159 4514 14514 14515

42 43 44 4028

45 141 145

4511 4543 14511 14513

46 47 48 49 246 247 248 249

547

548

537

347 447

4055 14543 14544 14547

VCC

2S

2A0

2A1

2Y0

2Y1

2Y2

2Y3

1S

1A0

1A1

1Y0

1Y1

1Y2

1Y3

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

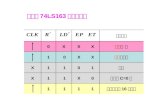

139

01 AAS 0123 YYYY1 1 1 0 1 1 0 11 0 1 10 1 1 11 1 1 1

0 0 00 0 10 1 0 0 1 1 1

½ 139 译码器真值表

双 2 线 – 4 线译码器

1S

1A0

1A1

1Y0

1Y1

1Y2

1Y3

GND

VCC

2S

2A0

2A1

2Y0

2Y1

2Y2

2Y3

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

239

VCC

2C

2S

A0

2Y3

2Y2

2Y1

2Y0

1S

1C

A1

1Y3

1Y2

1Y1

1Y0

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

155 156

双 2 线 – 4 线译码器

156 集电极开路输出

双 2 线 – 4 线译码器

VCC

1Y3

1A1

1A0

1S

2S

2OE

2AL

2Y0

2Y1

1Y2

1Y1

1Y0

1AL

1OE

2A0

2A1

2Y3

2Y2

GND

539

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

双 2 线 – 4 线译码器

1S

1A0

1A1

1Y0

1Y1

1Y2

1Y3

VSS

VDD

2S

2A0

2A1

2Y0

2Y1

2Y2

2Y3

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

455514555

1S

1A0

1A1

1Y0

1Y1

1Y2

1Y3

VSS

VDD

2S

2A0

2A1

2Y0

2Y1

2Y2

2Y3

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

455614556

VCC

Y0

Y1

Y2

Y3

Y4

Y5

Y6

A0

A1

A2

CP

S2

S1

Y7

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

131

VCC

Y0

Y1

Y2

Y3

Y4

Y5

Y6

A0

A1

A2

S3

S2

S1

Y7

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

137

A0

A1

A2

S3

S2

S1

Y7

GND

VCC

Y0

Y1

Y2

Y3

Y4

Y5

Y6

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

237

3 线 – 8 线译码器

VCC

Q3

Q4

A2

LE

E1

E2

E3

Q0

Q7

Q2

Q1

ACK

WR

RD

A0

A1

Q5

Q6

GND

547

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

ACKWRREEE D321

1 1 0 1 0 1 0 1 1 1 1 10 1 1 0 00 1 1 0 0

应答真值表

LEEEE 321

0 1 1 1 直通 寻址单元输出 0

0 1 1 0 存储 所有输出为 1

1 存储 所有输出为 1

0 存储 所有输出为 1

0 存储 所有输出为 1

锁存和输出状态表输 入 锁存

状态译码器输 出

3 线 – 8 线译码器(输入锁存,有应答功能)

VCC

Y0

Y1

Y2

Y3

Y4

Y5

Y6

A0

A1

A2

S3

S2

S1

Y7

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

138

012321 AAASSS 01234567 YYYYYYYY1 1 1 1 1 1 1 0 1 1 1 1 1 1 0 11 1 1 1 1 0 1 11 1 1 1 0 1 1 11 1 1 0 1 1 1 11 1 0 1 1 1 1 11 0 1 1 1 1 1 10 1 1 1 1 1 1 11 1 1 1 1 1 1 11 1 1 1 1 1 1 1

1 0 0 0 01 0 0 0 11 0 0 1 01 0 0 1 11 0 1 0 01 0 1 0 11 0 1 1 01 0 1 1 10 1

138 真值表

VCC

Y0

Y1

Y2

Y3

Y4

Y5

Y6

A0

A1

A2

S3

S2

S1

Y7

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

238

3 线 – 8 线译码器 / 多路分配器

VCC

Y3

Y4

C

G4

G3

G2

G1

AL

Y7

Y2

Y1

Y0

OE1

OE2

A

B

Y5

Y6

GND

538( 3S)

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

3 线 – 8 线译码器 / 多路分配器

1

0

0

1

21

21

AL

AL

OEOEAL

OEOEAL 所有输出为高阻态所有输出电平同 AL

有效输出为高电平有效输出为低电平

3 线 – 8 线译码器 / 多路分配器(有应答功能)

ACKWRREEEE D4321

1 1 1 1 0 1 0 10 0 1 1 1 1 10 0 1 1 0 00 0 1 1 0 0

应答真值表VCC

Y3

Y4

A2

E1

E2

E3

E4

Y0

Y7

Y2

Y1

ACK

WR

RD

A0

A1

Y5

Y6

GND

548

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

154

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

Y9

Y10

GND

VCC

A

B

C

D

G2

G1

Y15

Y14

Y13

Y12

Y11

4 线 – 16 线译码器 / 多路分配器

4 线 – 16 线译码器 / 多路分配器( OC 输出)

159

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

Y9

Y10

GND

VCC

A

B

C

D

G2

G1

Y15

Y14

Y13

Y12

Y11

4 线 – 16 线译码器 / 多路分配器

451414514

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

ST

A1

A2

Y7

Y6

Y5

Y4

Y3

Y1

Y2

Y0

VSS

VCC

INH

A4

A3

Y10

Y11

Y8

Y9

Y14

Y15

Y12

Y13

451514515

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

ST

A1

A2

Y7

Y6

Y5

Y4

Y3

Y1

Y2

Y0

VSS

VCC

INH

A4

A3

Y10

Y11

Y8

Y9

Y14

Y15

Y12

Y13

INH=1 时,所有输出为 0 INH=1 时,所有输出为 1

VCC

A0

A1

A2

A3

Y9

Y8

Y7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

424344

42 BCD— 十进制43 余三码—十进制44 格雷码—十进制

Y4

Y2

Y0

Y7

Y9

Y5

Y6

VSS

VDD

Y3

Y1

A1

A2

A3

A0

Y8

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

4028

4 线 – 10 线译码器

4 线 – 10 线译码器 / 多路分配器

VCC

Y3

Y4

A2

G4

G3

G2

G1

AL

Y7

Y2

Y1

Y0

AL

OE

A

B

Y5

Y6

GND

537( 3S

)

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

1 ,0

0 ,0

0

1

ALOE

ALOE

OE

OE 所有输出为高阻态所有输出电平同 AL

有效输出为高电平有效输出为低电平

VCC

A0

A1

A2

A3

Y9

Y8

Y7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

45 (OC)145

BCD – 十进制译码器 / 驱动器

Y0

Y1

Y5

Y4

GND

Y6

Y7

Y3

Y8

Y9

A0

A3

VCC

A1

A2

Y2

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

141(OC)

BCD – 七段码译码器 / 驱动器

VCC

f

g

a

b

c

d

e

B

C

LT

BI/RBO

RBI

D

A

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

347447

4 线 – 七段码译码器 / 驱动器

VDD

Yf

Yg

Ye

Yd

Yc

Yb

Ya

fDO

A1

A2

A3

A4

fDF

VEE

VSS

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

4055

VDD

Yf

Yg

Ye

Yd

Yc

Yb

Ya

ST

A2

A1

A3

A0

M

BI

VSS

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

14543

BCD – 七段码译码器 / 驱动器

VDD

Yf

Yg

Ye

Yd

Yc

Yb

Ya

RBI

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

14544

1

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

10

4055

ST

A2

A1

A3

A0

M

BI

RBO

VSS

14544

VDD

Yf

Yg

Ya

Yb

Yc

Yd

Ye

A1

A2

NC

BI

NC

A3

A0

VSS

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

14547

VCC

Yf

Yg

Ya

Yb

Yc

Yd

Ye

A1

A2

LT

BI/RBO

RBI

A3

A0

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

48248249(OC)

VCC

Yf

Yg

Ya

Yb

Yc

Yd

A1

A2

BI

A3

A0

Ye

GND

1

2

3

4

5

6

7

14

13

12

11

10

9

8

49

BCD – 七段译码器 / 驱动器

VCC

Yf

Yg

Ya

Yb

Yc

Yd

Ye

A1

A2

LT

BI/RBO

RBI

A3

A0

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

46 47246(OC)247(OC)

VDD

Yf

Yg

Ya

Yb

Yc

Yd

Ye

A1

A2

LT

BI

LE

A3

A0

VSS

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

451114511

BCD – 七段译码器 / 驱动器

VDD

Yf

Yg

Ya

Yb

Yc

Yd

Ye

RBO

A1

A2

LT

BI

LE

A3

A0

RBI

VSS

1

2

3

4

5

6

7

8

9

18

17

16

15

14

13

12

11

10

451314513

VDD

Yf

Yg

Ya

Yb

Yc

Yd

Ye

A1

A2

LT

BI

LE

A3

A0

VSS

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

454314543

代码转换器及编码器代码转换器及编码器类 别 品 种 代 号

BCD – 二进制代码转换器

二 – BCD 代码转换器10 线 – 4 线优先编码器8 线 – 3 线优先编码器4 位可级联优先寄存器8 线— 8 线优先编码器

注:对有下划线的型号,提供了真值表,其它型号可参照。

184

185 484

485147

148 348 4532 14532278

40147

149

VCC

G

E

D

C

B

A

Y8

Y1

Y2

Y3

Y4

Y5

Y6

Y7

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

184185

BCD 二进制代码转换器

184 BCD 二进制185 二进制 BCD

484485

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

E

D

C

B

A

Y1

Y2

Y3

Y4

GND

VCC

F

G

H

G2

G1

Y8

Y7

Y6

Y5

BCD 二进制代码转换器

484 BCD 二进制485 二进制 BCD

VCC

NC

Y3

I3

I2

I1

I9

Y0

I4

I5

I6

I7

I8

Y2

Y1

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

147

147 10 线 – 4 线优先编码器真值表

1 1 1 1 1 1 1 1 1 1 0 0

1 0 1

1 0 1 1 1 0 1 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 10 1 1 1 1 1 1 1 1 1

1 1 1 10 1 1 00 1 1 1 1 0 0 0 1 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 1

9876543210 IIIIIIIIII 0123 YYYY

10 线 – 4 线优先编码器

VDD

I0

Y3

I3

I2

I1

I9

Y0

I4

I5

I6

I7

I8

Y2

Y1

VSS

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

40147 1 1 1 11 0 0 11 0 0 0 0 1 1 1 0 1 1 00 1 0 10 1 0 00 0 1 10 0 1 00 0 0 10 0 0 0

40147 10 线 – 4 线优先编码器真值表

0 0 0 0 0 0 0 0 0 0 1 1 0 1 0 0 1 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 01 0 0 0 0 0 0 0 0 0

987654321 0 IIIIIIIIII 0123 YYYY

10 线 – 4 线优先编码器( BCD 输出)

VDD

YS

YEX

I3

I2

I1

I0

Y0

I4

I5

I6

I7

ST

Y2

Y1

VSS

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

453214532

8 线 – 3 线优先编码器

注: * 348 为“ Z”, 即高组态

148 真值表

1 1 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 0 1 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 10 1 1 1 1 1 1 1

1*1* 1* 1*1* 1* 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

1 0000000 00

1 1 1 0 0 1 0 1 0 10 1 0 1 0 1 0 10 1

ST 76543210 IIIIIIII 012 YYY S EX YY

VCC

YS

YEX

I3

I2

I1

I0

Y0

I4

I5

I6

I7

ST

Y2

Y1

GND

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

148348

1

2

3

4

5

6

7

14

13

12

11

10

9

8

STRB

D 3

D 4

1Cn

1Cn+1

1S

GND

VCC

2A

2B

2Cn

2Cn+1

NC

2S

278

4 位可级联优先寄存器

149

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

RI0

RI1

RI2

RI3

RI4

RI5

RI6

RI7

RQE

GND

VCC

RO0

RO1

RO2

RO3

RO4

RO5

RO6

RO7

RQP

0 1 2 3 4 5 6 7

1 1 1 1 1 1 1 11 1 1 1 1 1 1 11 1 1 1 1 1 1 01 1 1 1 1 1 0 1 1 1 1 1 1 0 1 11 1 1 1 0 1 1 1 1 1 1 0 1 1 1 11 1 0 1 1 1 1 11 0 1 1 1 1 1 10 1 1 1 1 1 1 1

149 真值表

0 1 2 3 4 5 6 7

1 1 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 0 1 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 10 1 1 1 1 1 1 1

RQE

1 0000000 00

RQP

11

0 000000 0

输 入 输 出

8 线— 8 线优先编码器

加法器加法器类 别 品 种 代 号

门控全加器

2 位二进制全加器 4 位二进制全加器 双进位保留全加器 4 位 BCD 码全加器 三串行加法器 四串行加法器 / 减法器

注:对有下划线的型号,提供了真值表,其它型号可参照。

80

82

83 283 4008

183

583 4560 14560

4032 4038

385

1

2

3

4

5

6

7

14

13

12

11

10

9

8

B*

BC

Cn

Cn+1

GND

VCC

B2

B1

AC

A*

A2

A1

80

注:1.2. 当 A* 做输入端时, A1 、 A2 须为低电平 ; 当 B* 做输入端时 , B1 、 B2 须为低电平。3. 当 A1 和 A2 或 B1 和 B2 做输入端时 , A* 或 B* 必须分别开路或用来构成线与逻辑。

;* 21C AAAAA 。21C * BBBBB

门控全加器

80 门控全加器功能表

1 1 01 0 11 0 10 1 01 0 10 1 00 1 00 0 1

B ACn ΣΣ 1nC0 0 00 0 10 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

1

2

3

4

5

6

7

14

13

12

11

10

9

8

S1

A1

B1

VCC

C0

NC

NC

A2

B2

S2

GND

C2

NC

NC

82

2 位二进制控全加器82 2 位二进制控全加器功能表

0 0 0 01 0 0 00 1 0 01 1 0 0

0 0 01 0 01 0 0 0 1 0

A1 B1 A2 B2当 C0 = 0 当 C0 = 1 S1 S2 C2 S1 S2 C2

0 0 1 01 0 1 00 1 1 01 1 1 0

0 0 0 11 0 0 10 1 0 11 1 0 1

0 0 1 11 0 1 10 1 1 11 1 1 1

1 0 00 1 00 1 0 1 1 0

0 1 01 1 01 1 0 0 0 1

1 1 00 0 10 0 1 1 0 1

0 1 01 1 01 1 0 0 0 1

0 0 11 0 11 0 1 0 1 1

1 1 00 0 10 0 1 1 0 11 0 10 1 10 1 1 1 1 1

A4

S3

A3

B3

VCC

S2

B2

A2

B4

S4

C4

C0

GND

B1

A1

S1

1

2

3

4

5

6

7

8

83

16

15

14

13

12

11

10

9

S2

B2

A2

S1

A1

B1

C0

GND

VCC

B3

A3

S3

A4

B4

S4

C4

1

2

3

4

5

6

7

8

283

16

15

14

13

12

11

10

9

4 位二进制全加器

A4

B3

A3

B2

A2

B1

A1

VSS

VDD

B4

C4

S4

S3

S2

S1

C0

1

2

3

4

5

6

7

8

4008

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

14

13

12

11

10

9

8

1ANC

1B

1Cn

1Cn+1

1S

GND

VCC

2A

2B

2Cn

2Cn+1

NC

2S

183

双进位保留全加器

4 位 BCD 码全加器

A2

B2

A3

B3

A4

B4

C0

VSS

VDD

A1

B1

S1

S2

S3

S4

C4

1

2

3

4

5

6

7

8

456014560

16

15

14

13

12

11

10

9

B1

B2

B3

A3

Cn

Cn+1

S2

GND

VCC

A2

A1

A0

B0

S0

S1

S3

1

2

3

4

5

6

7

8

583

16

15

14

13

12

11

10

9

三组串行加法器

加法器

加法器

加法器

A1B1

A2B2

A3B3

转换 1

转换 2

转换 3时钟 CP

进位复位 CR

S1

S2

S3

S3

I3

CP

S2

I2

CR

I1

VSS

VDD

A3

B3

A2

B2

B1

A1

S1

1

2

3

4

5

6

7

8

40324038*

16

15

14

13

12

11

10

9

4038 的时钟为下降沿触发。

385

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

CP

1F

1S

1B

1A

2A

2B

2S

2F

GND

VCC

4F

4S

4B

4A

3A

3B

3S

3F

CR

四串行加法器 / 减法器

清 零A + BA – B

0 0 1 1 1

功 能S CR CP

385 真值表

比较器比较器类 别 品 种 代 号

4 位数值比较器8 位恒等比较器可编程 8 位恒等和 4 位比较器双 8 位数值比较器16 位恒等比较器 (可编程,反相输入)12 位恒等比较器(可编程) 注:对有下划线的型号,提供了真值表,其它型号可参照。

85 4063 4585 14585

518 519

527

682 683 684 685

526

528

520 521 522

688 689686 687

524

B3

A<B

A=B

A>B

FA>B

FA=B

FA<B

GND

VCC

A3

B2

A2

A1

B1

A0

B0

1

2

3

4

5

6

7

8

854063

16

15

14

13

12

11

10

9

4 位数值比较器

4 位数值比较器真值表

=<======

>A3 B3

比 较 输 入

<=====>

A2B2

====>

A1B1

===>

A0 B0

001001001

100100100

001

010010

100100100

FA>BFA=BFA<BA>BA=BA<B

输 出级 连 输 入

B2

A2

FA=B

A>B

A<B

A=B

A1

VSS

VDD

A3

B2

FA>B

FA<B

B0

A0

B1

1

2

3

4

5

6

7

8

458514585

16

15

14

13

12

11

10

9

518519*

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

G

P0

Q0

P1

Q1

P2

Q2

P3

Q3

GND

VCC

EQ

Q7

P7

Q6

P6

Q5

P5

Q4

P4

100

0 P = Q 0 P≠Q

1 ×

EQ G DATA

注: 519 为集电极开路输出。

8 位数值比较器

518 、 519 真值表

520521522*

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

G

P0

Q0

P1

Q1

P2

Q2

P3

Q3

GND

VCC

EQ

Q7

P7

Q6

P6

Q5

P5

Q4

P4

011

0 P = Q 0 P≠Q

1 ×

EQ G DATA

注: 522 为集电极开路输出。

8 位数值比较器

520 、 521 、 522 真值表

8 位数值比较器

524

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

S0

I/O0

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

GND

VCC

S1

SE

C/SI

C/SO

EQ

GT

LT

M

CP

保持—在移位寄存器中保存数据读—读寄存器中内容到数据总线移位—在下个时钟上升沿上允许串行移位装入—将总线上数据装入寄存器

0101

0011

作 用S1S0

选 择

数值比较二进制补码比较

01

作 用M

数表示选择

状 态

1010010

EQ

输 出

1111100

GT

1111001

LT

OA—OH > I/O0—I/O7

OA—OH = I/O0—I/O7

OA—OH < I/O0—I/O7

OA—OH > I/O0—I/O7

OA—OH = I/O0—I/O7

OA—OH < I/O0—I/O7

数据比较输 入

1000010

000111

1000000

C/SOC/SISE

可编程 8 位恒等和 4 位比较器

527

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

G

P0

P1

P2

P3

P4

P5

P6

P7

GND

VCC

P=Q

Q11

P11

Q10

P10

Q9

P9

Q8

P8

8 位数值比较器

682( 3S )683(OC)684 ( 3S )685 (OC)

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

P>Q

P0

Q0

P1

Q1

P2

Q2

P3

Q3

GND

VCC

P=Q

Q7

P7

Q6

P6

Q5

P5

Q4

P4

1 10 11 0

P < Q P = QP > Q

P = Q P > QP Q

682、 683输入上拉电阻682、 684三态输出683、 685集电极开路输出

682 、 683 、 684 、 685 真值表

8 位数值比较器

VCC

G2

P=Q

Q7

P7

NC

Q6

P6

Q5

P5

Q4

P4

686( 3S )687(OC)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

P>Q

G1

P0

Q0

P1

Q1

NC

P2

Q2

P3

Q3

GND

0 11 1

01 1

P = Q 0 0 P < Q 0 0P > Q 0 0 × 1 1

P = Q P > Q P Q G1 G2

686 、 687 真值表

01 11

P = Q 0

P < Q P > Q

× 1

P = Q P Q EN

688( 3S )689(OC)

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

EN

P0

Q0

P1

Q1

P2

Q2

P3

Q3

GND

VCC

P=Q

Q7

P7

Q6

P6

Q5

P5

Q4

P4

8 位数值相等检测器

688 、 689 真值表

可编程 16 位恒等比较器 ( 反相输入 )

526

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

G

P0

P1

P2

P3

P4

P5

P6

P7

GND

VCC

P=Q

P15

P14

P13

P12

P11

P10

P9

P8

可编程 12 位恒等比较器

528

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

G

P0

P1

P2

P3

P4

P5

GND

VCC

P=Q

P11

P10

P9

P8

P7

P7

数据选择器数据选择器类 别 品 种 代 号

16 选 1 数据选择器

8 选 1 数据选择器

双 4 选 1 数据选择器 双 4 选 1 数据选择器

150

151 251152

4052153 253 352 353

157 158

4051

250 850 851250 4067

16 选 1 数据选择器

VCC

D8

D9

D10

D11

D12

D13

D14

D15

A

B

C

150

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

D7

D6

D5

D4

D3

D2

D1

D0

S

W

D

GND

1D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

× × × × 1 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 0 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 0 1 1 0 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 1 0

WD B C A S

150 真值表

VCC

D8

D9

D10

D11

D12

D13

D14

D15

A

B

C

250

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

D7

D6

D5

D4

D3

D2

D1

D0

S

W

D

GND

×D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

× × × × 1 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 0 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 0 1 1 0 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 1 0

WD B C A S

16 选 1 数据选择器 / 多路转换器( 3S )

250 真值表

VCC

D8

D9

D10

D11

D12

D13

D14

D15

Y

S0

S1

S2

S3

850851

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28

27

26

25

24

23

22

21

20

19

18

17

16

15

D7

D6

D5

D4

D3

D2

D1

D0

GY

G

GW

CP/SC

W

GND

入选择

851850输入选择

1 或0

CP

10000000000000000

SC

Dn

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

× × × × 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1

S3 S2 S1 S0

16 选 1 数据选择器 / 多路分配器( 3S )

输出

Z ZZ ZD ZZ DD D

1 × × 0 1 0 0 0 00 1 10 0 1

Y W

G GY GW

850 、 851 真值表

16 选 1 模拟开关

VDD

(I/O) 8

(I/O) 9

(I/O) 10

(I/O) 11

(I/O) 12

(I/O) 13

(I/O) 14

(I/O) 15

INH

A2

A3

4067

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

O/I

(I/O)7

(I/O)6

(I/O)5

(I/O)4

(I/O)3

(I/O)2

(I/O)1

(I/O)0

A0

A1

GND

输 入

无0123456789

101112131415

× × × × 1 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 0 1 0 0 0 0 1 0 0 1 0 1 0 1 0 0 1 0 1 1 0 1 1 0 0 0 1 1 0 1 0 1 1 1 0 0 1 1 1 1 0

导通通道

A3 A2 A1 A0 INH

4067 真值表

8 选 1 数据选择器

D3

D2

D1

D0

Y

Y

EN

GND

VCC

D4

D5

D6

D7

S0

S1

S2

1

2

3

4

5

6

7

8

151 251

16

15

14

13

12

11

10

9

0 1D0 D0

D1 D1

D2 D2

D3 D3

D4 D4

D5 D5

D6 D6

D7 D7

1 × × ×0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 1

Y YEN S2 S1 S0

151 、 251 真值表

D4

D3

D2

D1

D0

W

GND

1

2

3

4

5

6

7

14

13

12

11

10

9

8

VCC

D5

D6

D7

A

B

C

152

8 选 1 数据选择器

D0

D1

D2

D3

D4

D5

D6

D7

0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1

WC B A

152 真值表

无X0

X1

X2

X3

X4

X5

X6

X7

1 × × × 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1

Y WENAB S2 S1 S0

8 路双向模拟开关

X4

X6

X

X7

X5

ENAB

VEE

VSS

VDD

X2

X1

X0

X3

S0

S1

S2

1

2

3

4

5

6

7

8

4051

16

15

14

13

12

11

10

9

4051 真值表

1G

S1

1C3

1C2

1C1

1C0

1Y

VSS

VDD

2G

S0

2C3

2C2

2C1

2C0

2Y

1

2

3

4

5

6

7

8

153 253

16

15

14

13

12

11

10

9

S1 S0 G Y

0 0 00 1 01 0 01 1 0× × 1

C0

C1

C2

C3

1 *

双 4 选 1 数据选择器

* 253 为 Z

153 、 253 真值表

双 4 选 1 数据选择器

1G

B

1C3

1C2

1C1

1C0

1Y

VSS

VDD

2G

A

2C3

2C2

2C1

2C0

2Y

1

2

3

4

5

6

7

8

352 353

16

15

14

13

12

11

10

9 * 353 为 Z

C0

C1

C2

C3

1 *

0 0 00 1 01 0 01 1 0× × 1

YB A G

352 、 353 真值表

无 无X0 Y0

X1 Y1

X2 Y2

X3 Y3

1 × × 0 0 0 0 0 1 0 1 0 0 1 1

X YENAB S1 S0

Y0

Y2

Y

Y3

Y1

ENAB

VEE

VSS

VDD

X2

X1

X

X0

X3

S0

S1

1

2

3

4

5

6

7

8

4052

16

15

14

13

12

11

10

9

双 4 路双向模拟开关

4052 真值表

四 2 选 1 数据选择器

SEL

1A

1B

1Y

2A

2B

2Y

VSS

VDD

G

4A

4B

4Y

3A

3B

3Y

1

2

3

4

5

6

7

8

157 158

16

15

14

13

12

11

10

9

11

010

1 × × × 0 0 0 × 0 0 1 ×0 1 × 00 1 × 1

YG SEL A B

00

101

1 × × × 0 0 0 × 0 0 1 ×0 1 × 00 1 × 1

YG SEL A B

157 真值表

158 真值表