第三章 组合逻辑电路设计

-

Upload

melyssa-patterson -

Category

Documents

-

view

66 -

download

4

description

Transcript of 第三章 组合逻辑电路设计

第三章 组合逻辑电路设计第三章 组合逻辑电路设计

§3-1 集成逻辑电路的电气特性

§3-2 常用组合逻辑模块

§3-3 组合电路的设计方法

§3-4 险象与竞争

§3-5 小结

组合逻辑电路: 输出仅和当前的输入有关。

门电路

用以实现基本逻辑运算和复合逻辑运算的单元电路。

获得高、低电平的基本原理

ViVo

Vcc

半导体二极管的开关特性

二极管的单向导电性--正向电压导通,反向 电压截止。

理想二极管:正向导通电阻为 0 ,反向内阻无穷大。

半导体三极管的开关特性

双极型三极管的开关特性 基本开关电路

MOS 管的开关特性

§3-1 §3-1 集成逻辑电路的电气特性集成逻辑电路的电气特性 集成电路的工艺: TTL: 晶体管 - 晶体管逻辑 ( 标准 ,S,LS,AS,ALS,F)

速度快、电源电压:典型值 5V, 一般 4.5 ~ 5.5V 肖特基--提高电路工作速度的一种电路结 构的名称。 MOS :金属 - 氧化物 - 半导体逻辑 ( PMOS,NMOS,CMOS) (HC,AHC,AC,HCT,ACT,AHCT,LV,LVC)

功耗低、工作电源电压范围宽( 3 ~ 18V) 、 输入阻抗高、驱动能力、抗干扰能力强。 ECL : 发射极偶合逻辑 速度更快

TTL : 74 系列 ( 0 - 70℃) 54 系列(- 55 - 125 ℃)

74S 系列:肖特基系列74LS 系列:低功耗肖特基系列74AS 系列:高级肖特基系列74ALS 系列:高级低功耗肖特基系列74H 系列:高速型

肖特基:提高电路工作速度的一种电路结构的名称, 74S 系列 采用了肖特基抗饱和三极管。

TTL 电路

例: SN74LS00

厂标系列名 类型

功能号

00 :含四个二输入与非门的集成电路02 :含四个二输入或非门04 :六组反相器

7400 外引线排列

TTL 与非门电路

输出级的特点:在稳定的工作状态下 T4 和 T5 总是一个导通另一个截至,有效地降低了输出级的静态功耗,提高了驱动负载的能力。称其为推拉式( PUSH - PULL) 电路。

集成逻辑电路的电气特性集成逻辑电路的电气特性

§3-1-1 集成电路的主要电气指标

§3-1-2 逻辑电路的输出结构

§3-1-3 正、负逻辑极性

§3-1-4 逻辑符号

§3-1-5 使用逻辑门的几个问题

§3-1-1 §3-1-1 集成电路的主要电气指标集成电路的主要电气指标TTL “ 与非门”电路

输出低电平 VOL :输出低电平时的最高电压。

输出高电平 VOH :输出高电平时的最低电压。

输入高电平 VIH(Von 开门电平 ) :输入高电平时的最低电压。

输入低电平 VIL(VOFF 关门电平 ) :输入低电平时的最高电压。

高电平抗干扰容限 VNH : VNH=VOH-VIH

低电平抗干扰容限 VNL : VNH=VIL-VOL

阈值电平 Vth: 粗略估算用。

注意:两块集成电路级联时,考虑电平匹配问题。

前级 VOH 大于后级 VIH ,前级 VOL 小于后级 VIL 。

1. 输出电压与输入电压

集成电路的电平参数表集成电路的电平参数表

2. 输出电流和输入电流IOH --输出端为高电平时可输出的最大电流。IIH --输入端为高电平时注入的最大电流。IOL --输出端为低电平时可注入的最大电流。IIL --输入端为低电平时由输入端流出的的最大电

流。

扇出系数:可以驱动同类门的个数 ,IOL/IIL

74LS00: IOH=400uA IIH=20uA

IOL=8mA IOH=0.4mA

注意: 1. 前级 IOL 大于后级 IIL 之和;

2. 关于未接输入信号的引脚

与:多余脚接逻辑高或输入并联

或:多余脚接逻辑低或输入并联;

3. TTL 电路的输入端开路或接一阻抗较大

的电阻时,输入电压为高电平。

平均传输延时时间 tpd :输出由高变低、由低变高的平均延时时间。

tpdL: 输出由高电平到低电平的传输延迟时间;tpdH: 输出由低电平到高电平的传输延迟时间。

不同门电路的延迟及功耗不同门电路的延迟及功耗

各类电路的应用态势各类电路的应用态势

1 、推拉式结构 输出端不能并联。

§3-1-2 §3-1-2 逻辑电路的输出结构逻辑电路的输出结构

VCC

VOL

VCC

VOH

输出端要加上拉电阻,可以并联 , 并联后的逻辑关系为与(线与)。

22 、开路输出(、开路输出( OCOC )结构)结构

VCC

VOL VOH

VCCVCC

F1·F2

F2

F1

输出端除 0 , 1 状态外,还有一种高阻态,等效于输出端开路。输出端可以并联,但要保证在同一时刻最多只有一个输出端不是高阻态。

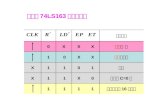

33 、三态输出结构、三态输出结构

c a b

0 × z

1 0 0

1 1 1

VCC

VOL

VCC

VOH

VCC

高阻

三态输出结构的应用三态输出结构的应用

数据选择器

§3-1-3 §3-1-3 正、负逻辑极性正、负逻辑极性1 、正逻辑: 0 表示低电平, 1 表示高电平。2 、负逻辑: 1 表示低电平, 0 表示高电平。

§3-1-4 §3-1-4 逻辑符号逻辑符号 逻辑符号用来 表示芯片的逻辑功能。1 、逻辑功能:与、或、非、与非、或非、异或、与或非。

2 、正、负逻辑:输入、输出脚上有无空心箭头。

3 、输出结构类型:推拉式结构、 OC 结构、三态输出结构。

4 、使能端:低电平有效、高电平有效。5 、管脚编号:

逻辑符号逻辑符号

7412574125 逻辑符号逻辑符号

几种芯片的逻辑符号几种芯片的逻辑符号

部分门电路及其传输延迟时间部分门电路及其传输延迟时间

§3-1-5 §3-1-5 使用逻辑门的几个问题使用逻辑门的几个问题1 、输入脚多余: 与:多余脚接逻辑高或输入并联。 或:多余脚接逻辑低或输入并联。2 、输入脚不足: 改变逻辑或用门电路扩展。3 、扇出系数: 采用功率门电路或改电路。

§3-2 §3-2 常用组合逻辑模块常用组合逻辑模块

§3-2-1 四位并行加法器

§3-2-2 数值比较器

§3-2-3 译码器

§3-2-4 数据选择器

§3-2-5 总线收发器

§3-2-6 其他常用器件

一个模块完成某个常用的特定的功能,如加法器、数值比较器、译码器、编码器及数据比较器等。

§3-2-1 §3-2-1 四位并行加法器四位并行加法器

一、 4位加法器逻辑图

图 1-1-3 加法器

《数字设计引论》 §1-1 数制

图 2-3-5 例 2-3-3 逻辑图

《数字设计引论》 §2-3 逻辑图

图 2-6-6 2 位加法器

《数字设计引论》 §2-6应用实例

二、加法器的级连

四位加法器级连成八位加法器

三、加法器的应用( 1 )

用 4位加法器构成余 3码到 8421码的转换器

加法器的应用( 2 )

一位BCD码加法器

图 1-2-3 1位BCD码加法器方框图

《数字设计引论》 §1-2 二值编码

§3-2-2 §3-2-2 数值比较器数值比较器

4位比较器

低位比较结果级连→

一、数值比较器逻辑图一、数值比较器逻辑图

数值比较器功能表数值比较器功能表

二、数值比较器的级连二、数值比较器的级连

4位比较器组成 8位比较器

三、数值比较器的应用三、数值比较器的应用

交通控制灯电路的一部分

§3-2-3 §3-2-3 译码器译码器

一、变量译码器

二、变量译码器的扩展

三、变量译码器实现组合逻辑函数

四、变量译码器构成数据分配器

五、显示译码器

一、变量译码器一、变量译码器

2-4译码器

3-8译码器

3-8译码器功能表

例 2-6-3 译码器

0010

1011

2012

3013

mbbY

mbbY

mbbY

mbbY

二、变量译码器的扩展二、变量译码器的扩展

74138

树形扩展

三、变量译码器实现组合逻辑函数三、变量译码器实现组合逻辑函数例 1 :变量译码器实现 1位全加器。

11111

01011

01101

10001

01110

10010

10100

00000

Σicoiyixicii

例 2 :译码器实现 1位 8421BCD码加法器

四、变量译码器构成四、变量译码器构成数据分配器数据分配器

五、显示译码器五、显示译码器

§3-2-4 §3-2-4 数据选择器数据选择器 (MUX)(MUX)一、数据选择器

8选 1MUX

4选 1MUX

74151 74253

YW

YST

Dm

DAAADAAA

DAAADAAA

DAAADAAA

DAAADAAAY

ST

iii

0)1(

)0(

7

0

70126012

50124012

30122012

10120012

:使能端不使能时

:当使能端使能时

数 8选 1MUX 功能表

二、数据选择器的扩展

74153

三、 MUX 实现组合函数

MUX 实现组合函数 (续 )

交通控制灯电路的一部分

§3-2-6 §3-2-6 常用组合逻辑器件常用组合逻辑器件

常用组合逻辑器件常用组合逻辑器件 ((续续 ))