perc.nersc

-

Upload

larissa-ayers -

Category

Documents

-

view

21 -

download

0

description

Transcript of perc.nersc

http://perc.nersc.gov

Performance Science and Engineering

Measuring memoryhierarchy performance

Analytic Performance Bounds for a PETSc Kernel

Mfl

op/s

0

100

200

300

400

500

600

700

800

900

SP Origin T3E Pentium Ultra II

Theoretical Peak Mem BW PeakOper. Issue Peak Observed

Bounding performancebased on fundamental

application characteristics

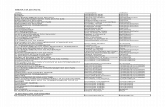

Block#

ProcedureName

Memory

Ref. Mem. Ref. %

L1 hit

Rate

L2 hit

RateRatio

Random

Memory Bandwidth

WeightedBandwidth

180155 dgemv_n 4.82E+09 0.9198 93.47 93.48 0.07 4166.0 3831.7

180159 dgemv_n 1.42E+08 0.0271 90.33 90.39 0.00 1809.2 49.1

180160 dgemv_n 1.22E+08 0.0232 94.81 99.89 0.00 5561.3 129.3

5885 MatSetValues 6.56E+07 0.0125 77.32 90.00 0.20 1522.6 19.0

MAPS for TCSini for random and non-random loads

Block #

Bandwidth180155180159180160

5885

2831.749.1

129.319.0

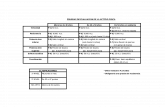

Convolvingapplication &

machine topredict

performance

Compilerframeworkto optimizehigh-level

abstractions

Infrastructurefor accessing

hardwareperformance

monitors

Infrastructurefor dynamic

instrumentation

Tools formeasuring &understanding

applicationperformance

ENABLING TECHNOLOGIESC O N V O L U T I O

N S

Enhanced Simulations

& Experiments

ApplicationSignatures

MachineSignatures

BoundModels

PhaseModels

PAPI Sigma++ DynInst

Scientific Simulations

& ExperimentsROSE SvPablo Tau

CacheSimulator

PredictionTool

MemoryRef Tool

dumpMap .addr

sourcefiles

.lstfiles

tracefiles

ProgramExecution

InstrumentedbinarySigma

Compile/Link

Infrastructurefor capturing& analyzing

memory accesses

Lawrence LivermoreNational LaboratoryDan QuinlanBronis de Supinski

Universityof Maryland

Jeff Hollingsworth

Oak RidgeNational LaboratoryPatrick Worley Jeffrey Vetter

San DiegoSupercomputing Center

Allan Snavely

University ofNorth Carolina

Dan Reed

ArgonneNational LaboratoryPaul HovlandBoyana Norris

Universityof Tennessee

Jack Dongarra

Lawrence BerkeleyNational LaboratoryDavid BaileyErich Strohmaier

Primary participants:

Supplementaryparticipants:

Technical Universityof Catalonia

Jesús Labarta

Los AlamosNational LaboratoryAdolfy HoisieHarvey Wasserman

Portland StateUniversity

Karen Karavanic

Universityof Oregon

Allen Malony

RiceUniversity

J. Mellor-Crummey

Universityof Wisconsin

Barton P. Miller

Thomas J. Watson Research CenterPO Box 218Yorktown Heights, NY 10598

IBMResearch

Luiz DeRose