Microprocessador 8085

-

Upload

maickson-leao -

Category

Documents

-

view

118 -

download

0

Transcript of Microprocessador 8085

20/04/2320/04/23 11

UFPA / ITEC / FEE

Microprocessadores

Microprocessador 8085

Prof. Daniel Cardoso

20/04/2320/04/23 22

EmentaEmenta

1. Arquitetura

2. Pinagem

3. Instruções

4. Sistema mínimo

5. Organização da memória

6. Temporização das instruções

7. Técnicas de E/S

8. Conclusão

Intel 8085

20/04/2320/04/23 44

Arquitetura da UCP IntelArquitetura da UCP Intel 8085A8085A

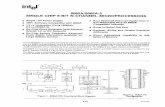

Pinagem da UCP IntelPinagem da UCP Intel 8085A8085A

• Pinos 1 e 2: X1 e X2X1 e X2 servem para a conexão de um cristal ou de um circuito RC ou LC. Eles vão definir a frequência do oscilador interno do 8085. O cristal é a melhor opção.

• Pino 3: RESET OUTQuando alto, indica que o 8085 está sendo inicializado. Este sinal vai para os dispositivos periféricos para inicializar todo o sistema. Quando RESET OUT torna-se baixo, o processamento começa.

• Pino 4: SODSaída serial de dados.

• Pino 5: SIDEntrada serial de dados.

Pinagem da UCP IntelPinagem da UCP Intel 8085A8085A

• Pinos 6 a 10:Cinco entradas para pedidos de interrupção, em ordem decrescente de prioridade. Se duas ou mais se tornarem ativas ao mesmo tempo, o 8085 vai atendê-las pela ordem de prioridade.

• Pino 11: INTASaída do reconhecimento de interrupção, para responder a um INTR.

• Pinos 12 a 19:Barramento de dados de 8 bits (D0–D7), multiplexado com a metade inferior do barramento de endereços (A0–A7). Isso mantém o número de pinos em 40.

Pinagem da UCP IntelPinagem da UCP Intel 8085A8085A

• Pinos 21 a 28: A8 - A15Metade superior do barramento de endereços.

• Pinos 29 e 33: S0 e S1

São sinais de saída conhecidos como sinais de status. Indicam o tipo de operação que o 8085 está executando no momento.

• Pino 30: ALEHabilitação do latch de endereços. É um sinal de saída para CI’s de memórias. A borda de descida do sinal ALE carrega o endereço presente no barramento no latch de endereços (REM) do CI de memória.

Pinagem da UCP IntelPinagem da UCP Intel 8085A8085A

• Pinos 31, 32 e 34: WR, RD e IO/MEstes três pinos funcionam em conjunto. Eles devem ser ligados às pastilhas de memória e de E/S. IO/M baixo indica uma operação com memória e IO/M alto indica uma operação de E/S. WR e RD indicam se se trata de uma operação de escrita ou de leitura, e nunca estão ambos ativos ao mesmo tempo.

• Pino 35: READYUm pino de entrada que recebe um sinal de prontidão de um periférico. Enquanto READY é baixo, o 8085 fica gerando estados de espera (WAIT). Quando READY é alto, o 8085 completa a transferência de dados. Utilizado para fazer handshaking com periféricos mais lentos que o 8085.

Pinagem da UCP IntelPinagem da UCP Intel 8085A8085A

• Pino 36: RESET INEntrada do sinal de RESET, que pode vir de um botão de pressão acionável pelo operador. Enquanto está em nível baixo, RESET IN reinicializa a UCP e envia o RESET OUT ao pino 3.

• Pino 37: CLK OUTSaída do sinal de relógio do 8085, que deve ser enviado para as pastilhas periféricas para sincronizar sua operação.

• Pinos 38 e 39: HLDA e HoldUsados para o 8085 entregar o controle dos barramentos a um controlador de ADM (Acesso Direto à Memória).

Circuito de relógioCircuito de relógio

1010

fmin = 500 kHz fmax = 3,125 MHz

• Um cristal gera uma frequência muito mais estável que os demais circuitos.

• A frequência do relógio é a metade da frequência do oscilador, pois o flip-flop divide por 2.

• O circuito LC tem uma tolerância de frequência de 10%.

• O circuito RC recomendado resulta numa frequência de relógio de 1,5 MHz.

Novas instruçõesNovas instruções

Sintaxe Operação Bytes

XCHG (DE) (HL) 1

STAX B ((BC)) (A) 1

STAX D ((DE)) (A) 1

LDAX B (A) ((BC)) 1

LDAX D (A) ((DE)) 1

LHLD endr. (L) (endr); (H) (endr + 1) 3

SHLD endr. (endr) (L); (endr + 1) (H) 3

PCHL (PC) (HL) 1

SPHL (SP) (HL) 1

XTHL (L) ((SP)); (H) ((SP+1)) 1

• Quando a soma de dois nibbles é < 9, o resultado já está certo em BCD.

• Quando a soma de dois nibbles é > 9, deve ser adicionado 610 (0110) ao resultado para gerar a forma BCD correta.

• Exemplos: fazer as somas em BCD:

8 + 5 = 13 9 + 8 = 17

Adição em BCDAdição em BCD

• Como se sabe quando a soma é > 9?• O nibble do resultado é inválido (1010 a 1111);• Ocorre transporte para o nibble superior seguinte.

• Esse transporte do bit 3 para o bit 4 é chamado de carry auxiliar (AC), e é mais um flag do 8085.

• Exemplos: fazer as somas em BCD:

98 + 84 = 182 48 + 39 = 87

Adição em BCDAdição em BCD

• Ajuste Decimal do Acumulador.

• Deve ser usada depois de qualquer operação na ULA que envolva números BCD.

• Corrige o conteúdo do acumulador para estar correto em BCD.

• A instrução DAA é a única que testa o valor do flag AC.

Instrução DAAInstrução DAA

• Só com o 8085 não se pode fazer nada de útil.

• É necessário conectá-lo a CI’s de memória e controladores de E/S para formar um sistema de computador útil.

• O sistema mínimo é o menor conjunto de CI’s que forma um computador funcional.

• O conjunto de CI’s compatíveis com o p é chamado de chipset.

Sistema mínimoSistema mínimo

Sistema mínimo com o 8085: famíSistema mínimo com o 8085: família MCS-85lia MCS-85

1616

• Durante alguns estados T, as linhas AD7 a AD0 fornecem a metade inferior do contador de programa, e em outros estados T, essas mesmas linhas fornecem um dado de 8 bits.

• A13 = 0: ativa a ROM 8355; A13 = 1: ativa a RAM 8156.

• O sinal ALE fica alto no início de cada ciclo de máquina, e durante o primeiro estado T, torna-se baixo. A borda de descida de ALE carrega o endereço vindo do 8085 no latch de endereço (REM) da pastilha de memória que estiver habilitada.

Sistema mínimo com o 8085: famíSistema mínimo com o 8085: família MCS-85lia MCS-85

• CLK OUT é o relógio do sistema, com a metade da frequência do oscilador.

• Um sinal READY alto entrando no 8085 indica que um periférico está pronto para uma transferência de dados.

• RD e WR indicam leitura e escrita tanto de uma pastilha de memória quanto de um dispositivo de E/S.

Sistema mínimo com o 8085: famíSistema mínimo com o 8085: família MCS-85lia MCS-85

• A 8156 é uma RAM estática organizada em 256 bytes (256 palavras x 8 bits). Seu barramento de endereços de 8 bits também é multiplexado com seu barramento de dados, tal como o 8085.

• A 8156 também tem três portas de E/S programáveis para funcionar como entradas ou saídas.

Sistema mínimo com o 8085: famíSistema mínimo com o 8085: família MCS-85lia MCS-85

• Quando alto, RESET OUT do 8085 inicializa o 8156.

• A 8355 é uma ROM de 2 KBytes (2048 palavras x 8 bits). As 11 linhas de endereço são multiplexadas com as 8 linhas de dados: A10 a A8 + AD7 a AD0.

• O sinal READY que sai da 8355 está baixo enquanto o endereço está sendo carregado na 8355. Depois da carga, READY sobe, avisando o 8085 para prosseguir com a leitura.

Sistema mínimo com o 8085: famíSistema mínimo com o 8085: família MCS-85lia MCS-85

Mapas de memóriaMapas de memória

• Quando A13 está baixo, a ROM está habilitada. Quando A13 está alto, a RAM está habilitada.

• No sistema mínimo, a ROM ocupa os endereços 0000H a 07FFH (2 KB), e a RAM ocupa os endereços 2000H a 20FFH (256 bytes).

• As 16 linhas de endereço do 8085 podem acessar um total de 64 KB. As linhas de endereço não usadas no sistema mínimo são irrelevantes ou « tanto faz ».

• Por causa disso, as seções de ROM e RAM se repetem no espaço de endereçamento total.

Mapas de memóriaMapas de memória

• Os endereços válidos de ROM são:XX0X X000 0000 0000 até

XX0X X111 1111 1111

• A ROM responderá a qualquer destes endereços porque A13 está baixo.

• Há um total de 15 sombras de ROM, áreas onde ela se repete. Diversos endereços acessam a mesma posição de ROM, p.ex. 0000H, 0800H, 1000H apontam para a primeira posição da ROM.

• A RAM também se repete: quando A13 está alto, os endereços válidos são:

XX1X XXXX 0000 0000 até XX1X XXXX 1111 1111

A primeira faixa de RAM é de 2000H a 20FFH, e as demais são sombras.

Usualmente, utiliza-se as faixas mais inferiores de ROM e de RAM na programação. As sombras não são utilizadas.

Mapas de memóriaMapas de memória

Ligando mais pastilhas de memória ao p, pode-se construir uma memória com qualquer tamanho até 64 KB.

A parte inferior da memória é geralmente reservada para instruções e dados fixos: sub-rotinas que operam o teclado, o vídeo etc.

A seguir, a área de dados variáveis usa uma RAM. É aqui que os programas do usuário e os resultados do processamento de dados são armazenados.

Mapas de memóriaMapas de memória

Mapas de memóriaMapas de memória

Diagramas de temporizaçãoDiagramas de temporização

20/04/2320/04/23 2626

20/04/2320/04/23 2727

Diagramas de temporizaçãoDiagramas de temporização

20/04/2320/04/23 2828

Diagramas de temporizaçãoDiagramas de temporização

20/04/2320/04/23 2929

Diagramas de temporizaçãoDiagramas de temporização

20/04/2320/04/23 3030

Diagramas de temporizaçãoDiagramas de temporização

Instruções de recomeço

Representam uma maneira eficiente de chamar sub-rotinas usadas com frequência.

Têm o mesmo efeito de uma CALL, usando apenas um byte;

Interrupções: recomeços por hardware

Prioridades das interrupções

Se duas ou mais interrupções forem ativadas ao mesmo tempo, o p as atenderá pela sua ordem de prioridade.

Disparo das interrupções

• Para atender a diferentes tipos de periféricos, existem interrupções ativadas por borda e por nível.

Circuitos de interrupção

Instrução SIM

Instrução RIM

Exemplo de E/S por InterrupçãoExemplo de E/S por Interrupção

20/04/2320/04/23 3939

Expansão das InterrupçõesExpansão das Interrupções

20/04/2320/04/23 4040

Acesso Direto à MemóriaAcesso Direto à Memória

20/04/2320/04/23 4141

Exercícios

1. No esquema de entrada programada, use o bit 0 da porta 10H para INICIO e o bit 1 da porta 11H para STATUS. Escreva um programa que recebe e armazena 256 bytes de dados nos endereços 5000H a 50FFH.

Exercícios

LXI H, 5000H MVI C, 00HLOOP: MVI A, 01H OUT 10HWAIT: IN 11H ANI 02H JZ WAIT IN 12H MOV M,A INX H MVI A, 00H OUT 10H DCR C JNZ LOOP HLT

2. Escreva um programa que transfira os conteúdos dos endereços 8000H a 83FFH para um dispositivo periférico, fazendo handshaking como na figura.

Exercícios

LXI H, 8000HLOOP: MOV A,M OUT 12H MVI A, 40H OUT 10HWAIT: IN 11H ANI 80H JZ WAIT INX H MVI A, 00H OUT 10H MOV A, H CPI 83H JNZ LOOP MOV A, L CPI FFH JNZ LOOP HLT

Exercícios

3. A UCP está processando o programa principal. Após um ciclo de instrução, ela constata que as interrupções pendentes I7.5, I6.5 e I5.5 estão todas altas. Que interrupção é atendida em primeiro pela UCP em cada um dos casos seguintes?

a) IE e M7.5 estão altos, M6.5 e M5.5 estão baixos.

b) IE, M7.5, M6.5 e M5.5 estão todos altos. c) IE está alto, M7.5, M6.5 e M5.5 estão baixos. d) IE está baixo.

Exercícios

Circuitos de interrupção

Exercícios

4. Sejam as instruções

MVI A, 1DH

SIM

Depois da execução de SIM, que interrupções estão mascaradas?

5. Uma sub-rotina de atendimento de interrupção termina com:5. Uma sub-rotina de atendimento de interrupção termina com:

RIM EI RETRIM EI RET

Se o acumulador contém CAH depois da execução de RIM, responda:Se o acumulador contém CAH depois da execução de RIM, responda:

a)a) O dado serial de entrada está alto ou baixo?O dado serial de entrada está alto ou baixo?

b)b) Quais são as interrupções pendentes?Quais são as interrupções pendentes?

c)c) O bit de habilitação de interrupção está alto ou baixo?O bit de habilitação de interrupção está alto ou baixo?

d)d) Que interrupções estão mascaradas?Que interrupções estão mascaradas?

20/04/2320/04/23 4949

Exercícios

6. Um programa para entrada de dados serial:6. Um programa para entrada de dados serial:

MVI B, 00HMVI B, 00H

MVI C, 08HMVI C, 08H

LOOP: RIMLOOP: RIM

ANI 80HANI 80H

ORA BORA B

RRC RRC

MOV B,AMOV B,A

DCR CDCR C

JNZ LOOPJNZ LOOP

RLCRLC

HLTHLT

Os bits SID sucessivos depois de cada execução de RIM são Os bits SID sucessivos depois de cada execução de RIM são 1,1,0,0,0,0,1,0.1,1,0,0,0,0,1,0.

20/04/2320/04/23 5050

Exercícios

a) Que contém o registrador B depois da primeira execução de MOV a) Que contém o registrador B depois da primeira execução de MOV B,A?B,A?

b) Que contém o registrador B depois da segunda execução de MOV b) Que contém o registrador B depois da segunda execução de MOV B,A?B,A?

c) Qual é o conteúdo do acumulador depois da execução de RLC? c) Qual é o conteúdo do acumulador depois da execução de RLC? Que letra é essa no código ASCII?Que letra é essa no código ASCII?

d) O bit SID correspondente ao LSB foi recebido em primeiro ou em d) O bit SID correspondente ao LSB foi recebido em primeiro ou em último lugar?último lugar?

20/04/2320/04/23 5151

Exercícios