DAC_F05

-

Upload

garcia-jesus -

Category

Documents

-

view

216 -

download

0

Transcript of DAC_F05

-

7/28/2019 DAC_F05

1/39

1

Digital to Analog Converter

Nov. 1, 2005Fabian Goericke, Keunhan Park,

Geoffrey Williams

-

7/28/2019 DAC_F05

2/39

2

Outline

What is a DAC?

Types of DAC Circuits

Resistor-string DAC

Binary weighted DAC

R-2R Ladder DAC

Specifications of DAC

Errors

Applications

-

7/28/2019 DAC_F05

3/39

3

A digital to analogconverter (DAC) is adevice that converts

digital numbers (binary)into an analog voltage orcurrent output.

01

0

1

00

1

1

01

1

1

10

0

1

10

0

1

10

1

0

10

1

1 DAC

What is a DAC?

-

7/28/2019 DAC_F05

4/39

4

What is a DAC?

10111001 10100111 10000110010101000011001000010000

Digital Input Signal

A

nalogOutputSi

gnal

-

7/28/2019 DAC_F05

5/39

5

Types of DAC Circuits

1. Resistor String

2. Binary Weighted Resistor

3. R-2R Ladder

-

7/28/2019 DAC_F05

6/39

6

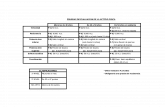

Components of a String DAC

Resistor String supply

discrete voltage levels

Selection Switches

connect the right voltage level

to op-amp according to input

bits

Op-amp amplifies the

discrete voltage levels to

desired range, keeps thecurrent low

Resistor String DAC

-

7/28/2019 DAC_F05

7/39

7

8

/ /(8 )

8 8

total

REF total REF

n n

nn REF

REF

R R

I V R V R

V R I n R I V n R I n

V VV R I

Resistor String

3

8

38 3

8

REFV V

V V V

Example

Resistor String DAC

-

7/28/2019 DAC_F05

8/39

8

1 1 0 6V 1 1 1 7V

1 0 0 4V 0 0 0 0V

Selection Switches

Resistor String DAC

-

7/28/2019 DAC_F05

9/39

9

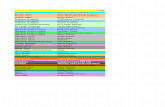

Advantages:

simple

fast for < 8 bits

Disadvantages:

high element count for higher resolutions, reason:

number of resistors:

number of switches:

slow for > 10 bits

2n

2 1n

Resistor String DAC

-

7/28/2019 DAC_F05

10/39

10

Basic Idea:

Use a summing

op-amp circuit

Use transistors toswitch between

high and ground

Use resistors

scaled by two to

divide voltage on

each branch by a

power of two

-

+

R

2R

4R

2n

R

Rf

Vout

refV

Binary Weighted Resistor DAC

-

7/28/2019 DAC_F05

11/39

11

non-inverting input on ground virtual ground atinverting input

KIRCHHOFFs current law and no input current intoop-amp I1 + I2 = 0

I1 = V1 / R + V2 / (2R) + V3 / (4R) +

31 2 4

2 1

( ) ...2 4 8out f f f

VV V VV R I R I R

R R R R

Binary Weighted Resistor DAC

-

7/28/2019 DAC_F05

12/39

12

Binary Weighted Resistor DAC

31 2 42 1

( ) ...2 4 8

out f f f

VV V VV R I R I R

R R R R

Terms have less influence

Mostsignificant

bit

Leastsignificant

bit

Vn = Vref, if bit is set

Vn = 0, if bit is clear

Rf = R / 2

-

7/28/2019 DAC_F05

13/39

13

Advantages

Simple

Fast

Disadvantages

Needs large range of resistor values (2000:1 for 12-

bit) with high precision in low resistor values

Needs very small switch resistances

Binary Weighted Resistor DAC

-

7/28/2019 DAC_F05

14/39

14

R-2R Resistor Ladder DAC

Simplest type of DAC

Requires only two precision resistance valuce (R and 2R)

Each bit controls a switch between

ground and the inverting input of the

op amp.

The switch is connected to ground ifthe corresponding bit is zero.

0 0 0 0

4 bit converter

Vref

-

7/28/2019 DAC_F05

15/39

15

R-2R DAC Example

Convert 0001 to analog

V0V1V2V3

1

1/ 2 1/ 2eqR R

R R

0 1 11

2

RV V V

R R

V0V1V0V1

=

1 2 21

2

RV V V

R R

2 3 31

2

RV V V

R R

Vref

-

7/28/2019 DAC_F05

16/39

16

R-2R DAC Example

Convert 0001 to analog

01

8refV V

2R

R

V0

out 0R 1

V2R 16

refV V

Vref

-

7/28/2019 DAC_F05

17/39

17

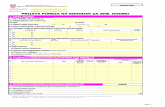

R-2R DAC Summary

Conversion results for each bit

Conversion equation forN-bit DAC

Digital bit Analog Conversion

0001

00100100

1000

,0 /16out ref V V

,1 /8out ref V V

,2 / 4out ref V V

,3 / 2out ref V V

3 ,3 2 ,2

1 ,1 0 ,0

out out out

out out

V b V b V

b V b V

for

3 2 1 0 ( 0 or 1)ib b b b b

( )1 2

Nref

out N i ii

VV b

Resolution2

ref

N

V

-

7/28/2019 DAC_F05

18/39

18

AdvantagesOnly two resistor values

Does not need the kind of precision as Binary

weighted DACs

Easy to manufacture

Faster response time

DisadvantagesMore confusing analysis

R-2R DAC Summary

-

7/28/2019 DAC_F05

19/39

19

Specification of DAC

Resolution

Speed

Settling time

Linearity

Reference voltage

-

7/28/2019 DAC_F05

20/39

20

The amount of variance in output voltage for

every change of the LSB in the digital input.

How closely can we approximate the desiredoutput signal(Higher Res. = finer detail=smaller

Voltage divisions)

A common DAC has a 8 - 16 bit Resolution

NLSB

VV

2Resolution

Ref

N = Number of bits

Specification - Resolution

-

7/28/2019 DAC_F05

21/39

21

Rate of conversion of a single digital input to its

analog equivalent

Conversion Rate depends on clock speed of input signal

settling time of converter

When the input changes rapidly, the DACconversion speed must be high.

Specification - Speed

-

7/28/2019 DAC_F05

22/39

22

The time required for the input signal voltage to settle to the

expected output voltage (within +/- of VLSB).

Ideally, an instantaneous change in analog voltage would occur

when a new binary word enters into DAC

Fast converters reduce slew time, but usually result in longer ring

time.

Specification Settling Time

tdelay

tslew tring

-

7/28/2019 DAC_F05

23/39

23

The difference between the desired analog

output and the actual output over the full range

of expected values.

Specification Linearity

-

7/28/2019 DAC_F05

24/39

24

Specification Linearity

Linearity(Ideal Case)

Digital Input

Perfect Agreement

Desired/Approximate Output

Analog

OutputVoltage

NON-Linearity(Real World)

Analog

OutputVoltage

Digital Input

Desired Output

Miss-alignment

Approximate

output

Ideally, a DAC should produce a linear relationship

between a digital input and the analog output, this is not

always the case.

-

7/28/2019 DAC_F05

25/39

25

A specified voltage used to determine how each

digital input will be assigned to each voltage

division. Types:

Non-multiplier DAC: Vref is fixed (specified by the

manufacturer)

Multiplier DAC: Vref is provided via an external source

Specification Reference Voltage

-

7/28/2019 DAC_F05

26/39

26

Full Scale Voltage

Defined as the output when digital input is all 1s.

Specification Reference Voltage

1

10

2 11

2 2

N Nref

fs refi Ni

VV V

-

7/28/2019 DAC_F05

27/39

27

Errors

Common DAC Errors:

Gain Error

Offset Error

Full Scale Error

Non Linearity Non-Monotonic

Resolution Errors

Settling Time and Overshoot

There are a multiple sources of error associated with DAC

-

7/28/2019 DAC_F05

28/39

28

Gain Error: Deviation in the slope of the ideal curve and

with respect to the actual DAC output.

Gain Error

High Gain Error: Stepamplitude is higher than

the desired output

Low Gain Error: Stepamplitude is lower thanthe desired output

Digital Input

Desired/Ideal Output

AnalogOutputVoltage

Low Gain

High Gain

-

7/28/2019 DAC_F05

29/39

29

Offset Error: Occurs when there is an offset in the outputvoltage in reference to the ideal output.

Offset Error

Digital Input

Desired/Ideal OutputOutput Voltage

Positive Offset

NegativeOffset

This error may bedetected when all inputbits are low (i.e. 0).

-

7/28/2019 DAC_F05

30/39

30

Full Scale ErrorFull Scale Error: occurs when there is an offset in

voltage form the ideal output and a deviation inslope from the ideal gain.

-

7/28/2019 DAC_F05

31/39

31

Differential Non-Linearity: Voltage step size changes

vary with as digital input increases. Ideally each step

should be equivalent.

Differential Non-Linearity

Digital Input

Ideal Output

AnalogOu

tputVoltage

VLSB

2VLSB Diff. Non-Linearity = 2VLSB

-

7/28/2019 DAC_F05

32/39

32

Integral Non-Linearity: Occurs when the output voltage is

non linear. Basically an inability to adhere to the ideal

slope.

Integral Non-Linearity

Digital Input

Ideal Output

1VLSB Int. Non-Linearity = 1VLSB

Analog

OutputVoltage

-

7/28/2019 DAC_F05

33/39

33

Non-Monotonic Output Error: Occurs when thean increase in digital input results in a lower

output voltage.

Non-Monotonic Output Error

Analog

OutputVoltage

Digital Input

Desired Output

Monotonic

Non-Monotonic

-

7/28/2019 DAC_F05

34/39

34

Resolution Errors

Poor Resolution(1 bit)

Vout

Desired Analogsignal

Approximate

output

2Volt.

Levels

Digital Input0 0

1

Does not accurately

approximate the desired

output due large voltage

divisions.

-

7/28/2019 DAC_F05

35/39

35

Resolution Errors

Better Resolution(3 bit)

Digital Input

Vout

Desired Analog signal

Approximate

output

8Vo

lt.

Levels

000

001

010

011

100

101

110

111

110

101

100

011

010

001

000

Better approximation of

the of the desired output

signal due to the smaller

voltage divisions.

-

7/28/2019 DAC_F05

36/39

36

Settling Time and Overshoot

Analog Output

Voltage

Expecte

d

Voltage

+VLSB

-VLSB

Settling time Time

Settling Time: The time required for the voltage to settle within +/-

the voltage associated with the VLSB

. Any change in the input time

will not be reflected immediately due to the lag time.

Overshoot: occurs when the output voltage overshoots the desired

analog output voltage.

-

7/28/2019 DAC_F05

37/39

37

Common Applications

Audio: Most modern audio signals are stored in

digital form (for example MP3s and CDs) and in

order to be heard through speakers they mustbe converted into an analog signal

Video:Video signals from a digital source, such

as a computer, must be converted to analog

form if they are to be displayed on an analog

monitor.

http://en.wikipedia.org/wiki/Digital-to-analog_converter

http://en.wikipedia.org/wiki/MP3http://en.wikipedia.org/wiki/Compact_dischttp://en.wikipedia.org/wiki/Compact_dischttp://en.wikipedia.org/wiki/MP3 -

7/28/2019 DAC_F05

38/39

38

References

Alciatore, Introduction to Mechatronics and MeasurementSystems, McGraw-Hill, 2003

Horowitz and Hill, The Art of Electronics, Cambridge UniversityPress, 2nd Ed. 1995

http://products.analog.com/products/info.asp?product=AD7224

http://courses.washington.edu/jbcallis/lectures/C464_Lec5_Sp-02.pdf

http://www.eecg.toronto.edu/~kphang/ece1371/chap11_slides.pdf

Previous students lectures on DAC

http://products.analog.com/products/info.asp?product=AD7224http://courses.washington.edu/jbcallis/lectures/C464_Lec5_Sp-02.pdfhttp://courses.washington.edu/jbcallis/lectures/C464_Lec5_Sp-02.pdfhttp://www.eecg.toronto.edu/~kphang/ece1371/chap11_slides.pdfhttp://www.eecg.toronto.edu/~kphang/ece1371/chap11_slides.pdfhttp://www.eecg.toronto.edu/~kphang/ece1371/chap11_slides.pdfhttp://www.eecg.toronto.edu/~kphang/ece1371/chap11_slides.pdfhttp://courses.washington.edu/jbcallis/lectures/C464_Lec5_Sp-02.pdfhttp://courses.washington.edu/jbcallis/lectures/C464_Lec5_Sp-02.pdfhttp://courses.washington.edu/jbcallis/lectures/C464_Lec5_Sp-02.pdfhttp://products.analog.com/products/info.asp?product=AD7224 -

7/28/2019 DAC_F05

39/39

39

Questions?