6비트덧셈기

-

Upload

herojoon1378 -

Category

Documents

-

view

450 -

download

4

description

Transcript of 6비트덧셈기

이산치

Project #6:

비트2-

덧셈기 설계

허규준09

김정무11

김종진11

정민정11

김슬기11

목차- -

개인별 업무-

일정계획-

회의록-

자료 조사-

알고리즘-

소스-

참고문헌 및 출처-

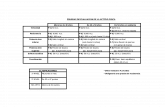

개인별 업무- -

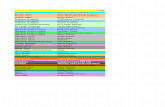

일정 계획- -

이름 역할

허규준08 알고리즘 구상

김종진11 알고리즘 구상 및 프로그램 설계

김정무11 자료조사

정민정11 자료조사 및 회의록 작성

김슬기11 조장 자료조사 및 보고서 작성 일정 계획: ,

월 일5 30 업무 분담 및 문제 파악

월 일6 2 조사내용 정리 및 이해 알고리즘 구상,

월 일6 6 최종 소스 토의 및 수정

회의록- -회의일시 년 월 일 수2012 5 30 ( ) 조 D0 작성자 정민정11참석자 허규준 정민정 김정무 김종진 김슬기09 , 11 , 11 , 11 , 11

회의내용

내용 비고

조원별 업무분담1.조장과 프로그램설계 명 관련사항 조사 명으로 팀을 구성했다1 , 3 .일정 계획2.다음 회의시간까지 자신이 맡은 업무를 수행해 와서 서로의 정보를교환하고 문제 해결을 위해 토의하기로 함.보고서 계획3.소집단보고서작성 및 자신들이 참고한 자료들과 출처를 조장에게 보내고 조장이 보고서 초안을 작성하기로 하였다.알고리즘 계획4.교수님이 설명해주신 내용을 바탕으로 소스를 어떻게 짤 것인가에 대한 대략적인 알고리즘을 구상하였다.

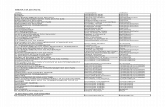

자료 조사

불 대수< >두 가지의 요소에 대하여 하나를 택하는 것과 같은 연산을 수행하는 논리 불 대수를 사- .용하면 컴퓨터 내부의 회로에 대한 것을 연산식으로 나타내고 그 결과를 회로에 대응시킬,수 있으므로 논리 회로를 다루는데 편리하다.

불 연산식<boolean expression( )>-불 대수에서의 연산식으로 단독의 변수나 정수 또는 그것들의 연산자로 조합시킨 것과,함수의 인용으로 표시한 식 예를 들면 개의 입력 가 있어 출력으로서 합 로 자리. , 2 X, Y , S올림한 가 얻어지는 연산식은 다음과 같이 나타낸다C .

불 대수의 기본 연산 논리 곱 논리 합 논리 부정 배타적 논리합: , , ,

논리곱(1)두 가지 명제의 조건이 연속될 때 앞의 것도 참이고 다음 것이 모두 참이어야 한다는o.

논리.두 개의 원소가 진 변수로서 와 라 한다면 이고 이어야 된다o. 2 A B A B .

와 같이 표현하고 와 같이 표현하기도 한다o. AB, A B, A B, A.B A AND B .∧ ∪표 은 두 개의 변수 와 에 대하여 논리곱 연산으로 조합되는 종류와 그 결과를o. 3-1 A B

보여 준다.

표 논리곱3-1.

A B A.B

0

0

1

1

0

1

0

1

0

0

0

1

논리합(2)두 가지 조건의 명제에서 둘 중 하나만 만족해도 되는 경우를 논리합이라 함o. .

로 표시한다o. A + B, A B, A B, A OR B .∨ ∪표 는 두 변수 와 에 대하여 논리합으로 조합되는 종류와 그 결과를 보여준다o. 3-2 A B .

표 논리합3-2.

A B A + B

0

0

1

1

0

1

0

1

0

1

1

1

논리 부정(3)현재의 명제를 부정하는 것o. .현재의 명제가 참인 경우 결과는 거짓이 된다.변수가 일 때 부정 와 같이 표현o. A , A' (A ), NOT A .가 인 경우 결과는 이 되고 이면 이 된다A 1 0 0 1 .표 은 변수 에 대한 논리 부정 연산에 대한 결과를 보여 준다o. 3-3 A .

표 논리 부정3-3.

A B'

0

1

1

0

배타적 논리합(4)두 개의 명제가 서로 반대되는 조건으로 논리합의 형태를 취하여 와 같o. AB' + A'B

은 논리 관계를 배타적 논리합 이라 한다(exclusive OR) .명제의 조건을 기억한 변수가 와 라면 와 같이 표현한다o. A B , A B, A XOR B .⊕표 는 두 개의 변수 와 에 대하여 배타적 논리합으로 조합되는 종류와 결o. 3-4 A B

과를 보여 준다.표 배타적 논리합3-4.

A B A (+) B

0

0

1

1

0

1

0

1

0

1

1

0

배타적 논리합은 대응되는 변수의 내용이 서로 다르면 결과가 이고 대응하는 내o. 1 ,용이 같으면 결과는 이다0 .

최소항의 논리합<disjunction of minterms( )>논리곱 형식을 최소항 논리합 형식을 최대항이라고 한다- , .

임의의 논리 변수 와 가 다음과 같은 조건일 때o. A B이면 결과가 이다1) A = 1, B = 0 1 .이면 결과가 이다2) A = 1, B = 1 1 .이면 결과가 이다3) A = 0, B = 1 0 .이면 결과가 이다4) A = 0, B = 1 0 .

결과가 인 경우는 과 이고 그 밖의 것은 이며 이에 대한 진리표와 최소항 및1 (1) (2) , 0 .최대항은 표 과 같다3-6 .

표 진리표와 최소항 및 최대항3-6

A B 결과(Y) 최소항 최대항

0 0 0 A' B' A + B0 1 0 A' B A + B'

1 0 1 AB' A' + B1 1 1 A B A' + B'

최소항에 의한 논리식(2)결과가 인 최소항을 논리합으로 결합한다o. 1 .표 에서 입력 변수가 인 경우를 정상형으로 표현하고 인 경우를 보수형으로3-6 1 , 0표현한다.정상형을 연산으로 묶어서 표현하면o. ANDY = A․B' + A․ B

이 경우를 최소항의 논리합이라 한다.

카르노 맵 맵<Karnaugh maps( /K )>논리식의 간소화 과정을 그림으로 나타내 주기 때문에 개 이하의 변수로 구성된- 5 - 6논리식을 간소화하는데 편리한 방법이다.

변수와 변수 카르노 맵(1) 1 2한 개의 논리 변수 의 값은 또는 이기 때문에 두 개의 칸으로 표시한A 0 1①

다.카르노 맵을 표현한 사각형의 오른쪽 칸을 에 대응하는 논리 변수 왼쪽 칸은 에 대1 , 0

응하는 논리 변수라 한다.그림 변수 카르노 맵3-1 1

A 0 1

X' X

논리 변수 개인 경우2②입력 가능한 값은 네 가지 조합.

여기에 대응하는 최소항을 사각형에 나타낸다.만일 입력 변수가 와 라면 를 행에 를 열에 위치시키고 행은 위에 을 위치시켜 교, A B A , B , 0차되는 지점에 최소항을 표현한다.그림 은 변수 입력에 대한 카르노 맵을 보여 준다3-2 2 .

그림 변수 카르노 맵과 최소항3-2 2변수 카르노 맵(a) 2

A

B0 1

0 A'B' AB'

0 A' B A B

변수 최소항(b) 2

X Y 최소항

0 0 A' B'

0 1 A' B

1 0 A B'

1 1 A B

카르노 맵의 교차되는 사각형은 최소항이 되므로 변수 진리표의 행에 해당되는 최소항과2같다 카르노 맵 내에 최소항의 결과인 과 을 표현한다. 1 0 .

카르노 맵으로 논리식을 간소화할 때에는 원래의 논리식에 의한 진리표에서 인 것만 카르1노 도에 표현하고 이웃한 항끼리 묵는다, 1 .묶여진 사각형에서 조건에 변화가 없는 것만 추출하여 논리합으로 표현 그림 은 논리식. 3-3

를 카르노 맵으로 간소화시키는 것을 보여 준다Y =A'B' + AB' + AB .

그림 변수 논리식의 간단화3-3 2

원 논리식 간단화된 논리식(a) (b)

변수 카르노 맵(2) 3어떤 논리식의 입력 변수가 세 개라면 세 변수로 결합되는 조합의 수는 가지이므8(23)

로 여덟 칸짜리 카르노 맵을 작성하면 된다 변수가 세 개라면 먼저 짝지어지는 두 개를 최.소항으로 만들어 행에 위치시키고 나마지 하나를 열에 위치시킨다, .이때 두 개의 짝지어진 것은 그레이 코드 순서인 의 순서로 배열한다 그림, (00, 01, 11, 10) .는 입력 변수 에 대한 카르노 맵과 최소항을 보여 준다3-4 A, B, C .

그림 변수 카르노 맵과 최소항3-4 3변수 카르노 맵(a) 3

AB

C00 01 11 10

0 A'B'C' A'BC' ABC' AB'C'

1 A'B'C A'BC ABC AB'C

변수 최소항(b) 3

A B C 최소항

0 0 0 A'B'C'0 0 1 A'B'C

0 1 0 A'BC'0 1 1 A'BC1 0 0 AB'C'

1 0 1 AB'C1 1 0 ABC'

1 1 1 ABC

변수가 세 개인 경우 양끝의 내용이 일 때는 이웃한 것으로 처리한다 인 것을 묶을 때1 .1 2,과 같이 의 배수가 되도록 하여 최대한 많이 묶는다4, 8 2 .

바이너리 디바이스<binary device( )>컴퓨터 과학에서의 진의 형태로 데이터를 기록하는 장치 또는 그러한 코드화된 데이터- 2 ,를 판독하는 장치.

논리게이트<logic gates( )>디지털 시스템의 회로를 구성하는 가장 기본적인 요소는 과 로 대변되는 논리대수에 의- 0 1한 연산을 집적회로 형태로 구현한 논리 게이트 이다 이 회로는 복잡한 논리를(logic gate) .간결하고 정확하게 표현할 수 있어 컴퓨터 등에 이용된다 이러한 논리대수의 기본이 되는.게이트로는 등이 있으며 이들의 조합으로 다양한 형태의 게이트가 만들어AND, OR, NOT ,진다.

게이트는 을 거짓 이라 하고 을 참 이라고 할 때 논리적으로 연AND 0 " " , 1 " " , "and"산자처럼 동작하기 때문에 그런 이름이 붙었다 아래 그림과 표는 게이트의. AND회로 기호와 논리조합을 보여주고 있다 기호에서 입력단자는 왼쪽에 있는 것이 (고 출력단자는 오른쪽에 있는 것이다 두 개의 입력이 모두 참 이면 출력도 참, ). " " , "이 되며 그렇지 않은 경우는 항상 거짓 이 된다" , " " .

AND gate

게이트는 논리적 포함관계인 의 방식으로 동작하기 때문에 그런 이름을 얻OR "or"었다 두 개의 입력중 하나만 참 이어도 출력은 참 이 되며 만약 두 개의 입력이. " " " " ,모두 거짓 이면 출력도 거짓 이 된다" " " " .

입력

1

입력

2출력

0 0 0

0 1 0

1 0 0

1 1 1

OR gate

게이트는 논리의 둘 중 하나 라는 식으로 동작한다 즉 두XOR (exclusive-OR) " " . ,개의 입력중 하나가 참 이면 출력도 참 이 된다 그러나 두 개의 입력 모두가" " " " . , "거짓 이거나 또는 두 개의 입력 모두가 참 이라면 출력은 거짓 이 된다 이러한" " " " " . 회로를 관찰하는 다른 방법으로는 두 개의 입력들이 서로 다르면 출력은 이 되, 1고 두 개의 입력이 서로 같으면 출력은 이 된다고 생각해도 된다, 0 .

XOR gate

다른 형태의 인버터 장치들과 구분하기 위해 때로는 게이트라고 불리는 논 NOT ,리 변환기는 오직 한 개의 입력만을 가지며 논리 상태를 정반대로 만들어 준다, .

인버터 또는 NOT gate

게이트는 게이트 바로 뒤에 게이트가 이어지는 것 같이 동작한NAND NOT AND다 두 개의 입력 모두가 참 인 경우에만 출력이 거짓 이 되고 그렇지 않은 경우. " " " " ,는 모두 참 이다" " .

NAND gate

게이트는 게이트 바로 뒤에 게이트가 이어지는 것 같이 동작한다NOR NOT OR .두 개의 입력이 모두 거짓 인 경우에만 출력이 참 이 되고 그렇지 않은 경우는" " " " ,모두 거짓 이다" " .

NOR gate

입력

1

입력

2출력

0 0 0

0 1 1

1 0 1

1 1 1

입력

1

입력

2출력

0 0 0

0 1 1

1 0 1

1 1 0

입력 출력

1 0

0 1

입력

1

입력

2출력

0 0 1

0 1 1

1 0 1

1 1 0

입력 입력 출력

1 2

0 0 1

0 1 0

1 0 0

1 1 0

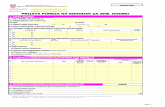

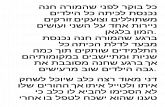

알고리즘< >이산 수학

비트 덧셈 연산기(2 )

먼저 비트의 진수를 형 변수 예 저장 한 후 연산을 시작 합니다2 2 int a, b, c, d .

가지의 함수로 연산이 진행 되는데2

이 함수로 진수의 비트 수를 각각 한int HalfAdderV(int x, int y) -> ((!x)&&y)||(x&&(!y)) 2 2

비트씩 덧셈 연산을 했을때에 나오는 값을 계산 할수 있습니다 단 캐리 값의 여부는 아직. (

알수 없습니다 )

이 함수로 연산 결과 캐리가 생기는지 알수 있습니다int HalfAdderU(int x, int y) -> x&&y .

입력 예제-

A B

+ C D

-------------

1 2 3

위와 같은 연산을 함수를 사용하여 와 그리고 와 의 덧셈연산 했을때의 결과HalfAdderV B D A C

값을 얻어 낼수 있습니다. 여기서 의 계산값은 를 통해 알 수 있습( 3 HalfAdderV ( B , D )

니다.

그 후 의 함수를 통해 연산 후 캐리가 생겼는지 알아본 후 그 결과 값과HalfAdderU B, D

함수를 통해 얻은 연산 값을 다시 함수를 통해 연산 결과를 내HalfAdderV A,C HalfAdderV

면 에서 생긴 캐리값과의 최종 덧셈 연산을 하여 의 최종적인 계산값을 알 수 있습니B,D 2

다.

의 계산값은 모두 일때 캐리가 발생하여 의 값이 일 될 수도 있고 값이 둘다1 A,C 1 1 1 A, C

일 아니어도 에서 올라온 캐리값과 계산돠어 최종 캐리가 발생하여 의 값이 이 될1 B, D 1 1

수 있으므로

를 통해 만 연산하여 캐리가 발생 되는지 확인 하고HalfAdderU A,C ,

의 값과 값 두 개의 값을 다시 로 캐리값HalfAdderV (A, C) HalfAdderU (B, D) HalfAdderU

이 발생하는지 확인하여

가지 결과 값을 연산자 를 통해 확인하여 두가지 결과값중 하나만 일 되더라도 의2 || (OR ) 1 1

값이 이 되도록 하여1

의 값을 얻을수 있습니다1 .

이런 방법으로 진 비트 연산기를 설계 하였습니다2 2 .

소스< >

#include <stdio.h>

int HalfAdderU(int x, int y);

int HalfAdderV(int x, int y);

int main()

{

int a,b,c,d,e,f,g;

int u1,v1,u2,u3;

를 입력하세요printf("a : ");

scanf("%d",&a);

를 입력하세요printf("b : ");

scanf("%d",&b);

를 입력하세요printf("c : ");

scanf("%d",&c);

를 입력하세요printf("d : ");

scanf("%d",&d);

u1=HalfAdderU(a,c);

v1=HalfAdderV(a,c);

u2=HalfAdderU(b,d);

g=HalfAdderV(b,d);

u3=HalfAdderU(v1,u2);

f=HalfAdderV(v1,u2);

e=u1||u3;

printf("e : %d, f : %d, g : %d\n",e,f,g);

return 0;

}

int HalfAdderU(int x, int y)

{

return x&&y;

}

int HalfAdderV(int x, int y)

{

return ((!x)&&y)||(x&&(!y));

}

참고문헌 및 출처자료 출처 -http://www.terms.co.kr/logicgate.html디지털 논리와 컴퓨터 설계 교보문고( )

http://hsol.tistory.com/196

블로그 한솔