3.1 正弦信号发生器的主要性能指标 3.2 低频信号发生器 3.2.1 低频信号发生器的基本组成 3.2.2 通用 RC 振荡器 3.3 高频信号发生器

实验 D 触发器及 JK 触发器

description

Transcript of 实验 D 触发器及 JK 触发器

实验 D触发器及 JK触发器一、实验目的二、实验仪器设备三、实验原理四、实验电路五、实验内容及步骤六、实验注意事项七、实验报告要求

一、实验目的 1 .掌握 D 和 JK 触发器的逻辑功能及测试方

法。 2 .进一步熟悉集成 JK 触发器和集成 D 触发

器的逻辑功能及其触发方式。 3 .掌握集成触发器的管脚排列。

二、实验原理1 . JK 触发器 在输入信号为双端的情况下, JK 触发器是功能完善、使用

灵活和通用性较强的一种触发器。本实验采用 74LS112 双 JK 触发器,是下降边沿触发的边沿触发器。引脚功能及逻辑符号见附录。

JK 触发器的状态方程为 :2 、 D 触发器 在输入信号为单端的情况下, D 触发器用起来最为方便,其

状态方程为 Qn+1 = Dn ,其输出状态的更新发生在 CP 脉冲的上升沿,故又称为上升沿触发的边沿触发器,触发器的状态只取决于时钟到来前 D 端的状态, D 触发器的应用很广,可用作数字信号的寄存,移位寄存,分频和波形发生等。有很多种型号可供各种用途的需要而选用。如双 D 74LS74 、

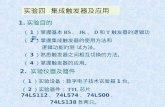

三、实验内容及步骤 1 .测试双 JK 触发器 74LS112 逻辑功能 (1) 测试 D 、 D 的复位、置位功能 任取一只 JK 触发器, D 、 D 、 J 、 K 端接逻辑开关输出插

口, CP 端接单次脉冲源, Q 、端接至逻辑电平显示输入插口。要求改变 D , D ( J 、 K 、 CP 处于任意状态),并在 D = 0 ( D = 1 )或 D = 0 ( D = 1 )作用期间任意改变 J 、 K 及 CP 的状态,观察 Q 、状态。自拟表格并记录之。

(2) 测试 JK 触发器的逻辑功能 按表 4-9-3 的要求改变 J 、 K 、 CP 端状态,观察 Q 、

状态变化,观察触发器状态更新是否发生在 CP 脉冲的下降沿(即 CP 由 1→0 ),记录之。

J K CPQn + 1

Qn= 0 Qn= 1

0 00→1

1→0

0 10→1

1→0

1 00→1

1→0

1 10→1

1→0

2 .测试双 D 触发器 74LS74 的逻辑功能 (1) 测试 D 、 D 的复位、置位功能。 测试方法同实验内容及步骤 1 ( 1) ,自

拟表格记录。 (2) 测试 D 触发器的逻辑功能。 按表 4-9-4 要求进行测试,并观察触发器状

态更新是否发生在 CP 脉冲的上升沿(即由 0→1 ),记录之。

D CPQn + 1

Qn= 0 Qn= 1

0

0→1

1→0

1

0→1

1→0

四、实验注意事项 1 .接线前首先检查所用集成块的好坏。 2 .实验时注意与 D 、 JK 触发器理论知识结

合。 3 .接线时应断开电源,严禁带电操作。

五、实验报告要求 1 .列表整理各类触发器的逻辑功能,测试

并记录。 2 .分析实验测试的数据说明触发器的触发

方式。 3 .分析回答利用普通的机械开关组成的数

据开关所产生的信号是否可作为触发器的时钟脉冲信号?为什么?是否可以用作触发器的其它输入端的信号?又是为什么?