(Introduction to IC Packaging) -...

Transcript of (Introduction to IC Packaging) -...

-

清大奈微所饒達仁教授

1

先進電子封裝設計導論 (Introduction to IC Packaging) 先進電子封裝設計導論先進電子封裝設計導論

(Introduction to IC Packaging)(Introduction to IC Packaging)饒達仁助理教授饒達仁助理教授 ((DaDa--JengJeng Jeffrey Jeffrey YaoYao))國立清華大學奈米工程與微系統研究所國立清華大學奈米工程與微系統研究所

-

清大奈微所饒達仁教授

2

Outline•

Traditional IC Packaging

•

Packaging Design•

First level of

Packaging

–

Wafer Bonding –

Chip (Die) Bonding and interconnection

–

Chip to Module Technology–

Enclose and Encapsulation

•

Second level of Packaging–

PCB Technology

•

Reliability•

Future Trend

-

清大奈微所饒達仁教授

3

積體電路

的製作流程

-

清大奈微所饒達仁教授

4

Why Worry About Packaging?

•

The package is integral to the final product–

You don’t have a product until its in a package

•

Package is 40-60%

of product cost•

Costumed packaging solutions have long lead time

•

Packaging design must be a part of product design, not an afterthough

•

Consider product trade-offs

upfront

-

清大奈微所饒達仁教授

5

Traditional IC Packaging

Traditional IC Traditional IC PackagingPackaging

-

清大奈微所饒達仁教授

6

An Overview of Packaging Process

•

Wafer level functional test

•

Separate into individual die (chip)

•

Mechanically attach to package or chip carrier (die bonding)–

Single chip module or multichip

module

–

Electrically attach to package (wire bonding)

•

Enclose, encapsulate, seal package

•

Functional test at package level

•

Sell

-

清大奈微所饒達仁教授

7

Typical Electronic Packaging Hierarchy

Source: Low cost flip-chip technologies, John Lau, 2000

First Level : Chip to module

(chip carrier)

Second Level: Module to PCB

(card)

Third Level: PCB to mother

board

Zero Level : Transistor

within IC

-

清大奈微所饒達仁教授

8Ref: Microelectronic Packaging, M.Datta

etc. pp. 16, CRC Press,2004

-

清大奈微所饒達仁教授

Chip-Packaging Interconnection

9Ref: Microelectronic Packaging, M.Datta

etc. pp. 19-20, CRC Press,2004

-

清大奈微所饒達仁教授

10

Package Family Characteristic Example

In-line Leads on one or opposing package side

SIP, PDIP, CERDIP

Small outline Leads on two or four sides, small body

SOJ, SOP, TSOP

Quad surface mount

Leads on four sides, large body

PLCC, PQFP, LDCC

Grid array Pins or pads placed in an array on body

Pin or pad grid array, BGA

金屬罐式構裝 單列式構裝 交叉引腳式構裝 雙列式構裝小型化構裝

四邊平面構裝 針格式構裝 無引腳晶料承載器 引腳晶料承載器

Also find from http://www.amkor.com

IC Package Families

-

清大奈微所饒達仁教授

11

Ref: 微系統封裝原理與技術, 邱碧秀著, 滄海書局, 2005

-

清大奈微所饒達仁教授

12Ref: 微系統封裝原理與技術, 邱碧秀著, 滄海書局, 2005

-

清大奈微所饒達仁教授

13

Glossary of Acronyms•

BGA: Ball grid array

•

CERDIP: Ceramic dual in-line package

•

CERQUAD: Ceramic quad flatpack•

CLCC: Ceramic leadless chip carrier

•

CPGA: Ceramic pin grid array•

C4: Controlled collapse chip connection

•

EQFP: Enhanced plastic quad flatpack

•

FQFP: Fine pitch quad flatpack•

GQFP: Guard ring quad flatpack

•

ILB: Inner lead bonding•

LDCC: Leaded ceramic chip carrier

•

LGA: Land grid array•

MCR: Molded carrier ring

•

MQFP: Metric quad flatpack•

MQUAD: Metal quad flatpack

•

OLB: Outer lead bonding•

PCB: Printed circuit board

•

PDIP: Plastic dual in-line package•

PGA: Pin grid array

•

PLCC: Plastic leaded chip carrier•

PQFP: Plastic quad flatpack

•

PWB: Printed wiring board•

QFP: Quad flatpack

•

SBA: Solder ball array•

SIP: Single in-line package

•

SOIC: Small outline integrated circuit

•

SOJ: Small outline J-bend•

SOP: Small outline gull wing

•

TAB: Tape automated bonding•

TCP: Tape carrier package

•

TQFP: Thin quad flatpack•

TSOP: Thin small outline package

•

VFQFP: Very fine pitch quad flatpack

•

ZIP: Zig-zag

in-line package

-

清大奈微所饒達仁教授

14

Packaging DesignPackaging DesignPackaging Design

-

清大奈微所饒達仁教授

15

IC Packaging Design•

Electrical design

•

Thermal management

•

Mechanical design

-

清大奈微所饒達仁教授

16

Microelectronic (IC) Packaging

•

Mechanical support by silicon substrate•

Electric connection–

Without wiring, IC is useless

–

Power distribution

(layout)•

Thermal management–

Heat dissipation problem

•

Protection from environment–

Life time

and reliability

•

Variability of packaging styles–

DIP, TAB, BGA, flip-chip, etc…

–

Cost, performance, and size trade-offs

-

清大奈微所饒達仁教授

17

Packaging in Electrical Design

•

Electrical problems relate to both –

Signal propagation

between the devices

–

Power distribution

required to operate these devices

-

清大奈微所饒達仁教授

18

Delay Caused by Package•

Circuit density

•

Input/Output (connections/cm2)•

Interconnection length

•

Wire material ability (line/cm)•

Propagation medium

•

Example: IBM 3090 CPU ~ 17.2 nsec

(>50% by package delay)

-

清大奈微所饒達仁教授

19

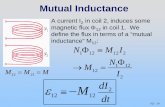

Microsystem

with Interference and Noise

•

Capacitive coupling: via stray capacitance C between the system and an external voltage

•

Magnetic coupling: via mutual inductance M between the system and an external current

•

Radiative

coupling: from electromagnetic radiation impinging on the system

•

Ground-loop coupling: from currents flowing between different ground points

Interference (controllable)

Noise (random)

-

清大奈微所饒達仁教授

20

Interference ProblemPower-line interference:

Resistive interference

-

清大奈微所饒達仁教授

21

Thermal Management

•

Heat Conduction

•

Heat Convection

•

Heat Radiation

bTT

q spcond)( −

= λ

)( paconv TThq −=

)( 44pa

TTqradi −= εσ封裝體表面溫度TP

-

清大奈微所饒達仁教授

22

Cooling Design for Products

Ref: 微系統封裝原理與技術, 邱碧秀著, 滄海書局, 2005

-

清大奈微所饒達仁教授

23

Mechanical Design: Ex: Stress Mismatch

-

清大奈微所饒達仁教授

24

Thermomechanical Deformation in Solder Joints

))(( 0max TTL cb −−αα

))(( 0min TTL cb −−αα

The expansion difference between board and carrier for hearing

The expansion difference between board and carrier for cooling

))(( minmax TTL cb −−=Δ αα

))(( minmax TThL

h cb−−=

Δ= ααγ

The difference in the displacement at heating and cooling is given by

The shear strain will be

-

清大奈微所饒達仁教授

25

Multidisciplinary Issues In Package Design

Decisions Factors ConsiderationsLeadcount

(no. of pins)Chip requirements

Electrical requirements, cost, size

Physical layout Electrical needs Size, power distributionForm (type) factor Chip protection

requirementsMechanical requirements (reliability), sealing, cost

Package material Thermal requirements

Cost, compatibility with other materials

Construction and layup

Supplier capability

Reliability requirements

Pin though-hole (PTH) or surface mount technology (SMT)

PCB assembly capability

Chip assembly capability

-

清大奈微所饒達仁教授

26

Manufacturing (Wafer and Chip Bonding)

ManufacturingManufacturing ((Wafer and Chip Bonding)Wafer and Chip Bonding)

-

清大奈微所饒達仁教授

27

Bonding Techniques on Each Level

Ref: 微系統封裝原理與技術, 邱碧秀著, 滄海書局, 2005

-

清大奈微所饒達仁教授

28

Classifying Wafer Bonding•

Direct wafer bonding–

No intermediate layer

•

Indirect wafer bonding–

An intermediate layer or adhesive

•

Heat-assisted bonding–

Fusion, Eutectic

•

Electrical field associated bonding–

Anodic

•

Chemistry-assisted bonding–

Adhesive

-

清大奈微所饒達仁教授

29

Fusion Wafer Bonding

For 200mm wafer with 0.35um process and above, the spec for curvature is < 50um.

-

清大奈微所饒達仁教授

30

Anodic Bonding

-

清大奈微所饒達仁教授

31

Eutectic Bonding

-

清大奈微所饒達仁教授

32

Application of Eutectic Bonding (Au-Si

Eutectic Bonding)

-

清大奈微所饒達仁教授

33

Example of Au-Si Eutectic BondingChip (Si)

SubstrateGold film

Chip (Si)

SubstrateGold film

Chip (Si)

SubstratePreform eutectic Au/Si

Procedure:Deposit 150Å

Cr/1500 Å

Pt/1500~5000Å

Au film on substrate.

Heat up to 425-500°C in N2 ambient.

(a)

(b)

(c)

-

清大奈微所饒達仁教授

34

Wafer Bonding Comparison•

Various methods with a range of characteristics

•

Anodic and direct bonding may need internal getter to get low vacuum levels in cavity

-

清大奈微所饒達仁教授

35

Wafer Bonding Systems

-

清大奈微所饒達仁教授

36

Manufacturing (Chip Bonding and Interconnection)

Manufacturing Manufacturing (Chip Bonding and Interconnection)(Chip Bonding and Interconnection)

-

清大奈微所饒達仁教授

37

First Level Package

Wafer -> Chip -> Die Attachment on a package -> Wire bonding -> Encapsulation

-

清大奈微所饒達仁教授

38

Ref: 微系統封裝原理與技術, 邱碧秀著, 滄海書局, 2005

-

清大奈微所饒達仁教授

39

Al or Au Wedge Wire Bonding

•

Al wedge to Al pad, Au wedge to Au pad–

Room temperature, pressure, and ultrasound

–

Metal intermixing results in solid joint

–

Ultrasound helps disrupts oxide films, enhances interdiffusion

–

Al-to-Au bond at package can cause purple plague (AuAl2

)

-

清大奈微所饒達仁教授

40

-

清大奈微所饒達仁教授

41

Tape Automated Bonding (TAB/TCP) Procedure

From Prof. Chih

Chen

-

清大奈微所饒達仁教授

42From Prof. Chih

Chen

-

清大奈微所饒達仁教授

43

Flip-Chip Bonding

•

Reduced signal inductance/ capacitance–

This is a key factor in high speed communication and switching devices

•

Reduced power/ground inductance –

Power can be brought directly into the core of the die, rather than having to be routed to the edges.

–

This greatly decreases the noise of the core power, improving performance of the silicon

•

Higher signal density/Die shrink –

The entire surface of the die can be used for interconnect, rather than just the edges.

–

Because flip chip can connect over the surface of the die, it can support vastly larger numbers of interconnects on the same die size

-

清大奈微所饒達仁教授

44

-

清大奈微所饒達仁教授

45

Chip to Module Technology

Chip to Module Chip to Module TechnologyTechnology

-

清大奈微所饒達仁教授

46Ref: 微系統封裝原理與技術, 邱碧秀著, 滄海書局, 2005

Traditional Single Chip Module Packaging

-

清大奈微所饒達仁教授

47

Module Assembly Schemes

Multichip Module (MCM)

-

清大奈微所饒達仁教授

48

•

For high density packaging•

Less lead

requirements, but more interconnections

•

Smaller size

but complicated design

(layout)

Single-Chip VS Multichip Module Packaging

-

清大奈微所饒達仁教授

49

Function of Multichip Package •

Remove heat effectively

from

the chips•

Provide interconnections

between all the chip with as many circuits as high a circuit performance as available to the multichip

substrate

•

Provide wiring density

with high-conductivity metal to interconnect all the chips with minimum chip-to-chip spacing

•

Provide multichip

substrate connections

for signal and

power distributions•

Provide protection to all the chip and the multichip

substrate itself

-

清大奈微所饒達仁教授

50

Packaging Efficiency of Various Packages

areapackagingmultichipactiveTotalareasiliconactiveTotalPeff =

-

清大奈微所饒達仁教授

51

Chip Stacked Packaging (CSP)

-

清大奈微所饒達仁教授

52

-

清大奈微所饒達仁教授

53

CSP VS Stacked MCM

-

清大奈微所饒達仁教授

54

3D Packaging

Ref: 微系統封裝原理與技術, 邱碧秀著, 滄海書局, 2005

-

清大奈微所饒達仁教授

55

Enclose and Encapsulation Enclose and Enclose and

Encapsulation Encapsulation

-

清大奈微所饒達仁教授

56

Seal and Encapsulation

•

Packaging sealing and encapsulation are for chip protection

•

Condensed moisture

on a device's surface during operation has been shown to lead to the principle causes of failure in the field

•

One packaging method designed to prevent performance degradation due to moisture's deleterious effects is the hermetic package

-

清大奈微所饒達仁教授

57

Ways for Encapsulation

Liquid EncapsulationPrinting Encapsulation

-

清大奈微所饒達仁教授

PCB Technology (Second Level Packaging)

PCB TechnologyPCB Technology (Second Level Packaging)(Second Level Packaging)

58

-

清大奈微所饒達仁教授

59Ref: Microelectronic Packaging, M.Datta

etc. pp. 16, CRC Press,2004

-

清大奈微所饒達仁教授

印刷電路板

在電子產業

中的定位

Ref: “印刷電路板概論-養成篇”, 台

灣電板產業學院, 全華科技2005.

-

清大奈微所饒達仁教授

基板材料之應用

-

清大奈微所饒達仁教授

印刷電路板結構分類

62Ref: “印刷電路板概論-養成篇”, 台

灣電板產業學院, 全華科技2005.

-

清大奈微所饒達仁教授

PCB Interconnection•

1950-1960間,主要是蝕刻銅的技術製造,使

其在單面形成金屬線路,接著在安裝電子零件 時,用焊接固定或連接。

•

由於零件縮小化,需要在一片PC板上,裝載更 多的零件,雙面線路配的方法即產生(如圖) 。

Ref: “印刷電路板概論-養成篇”, 台

灣電板產業學院, 全華科技2005.

-

清大奈微所饒達仁教授

線路製作流程

Ref: “印刷電路板

概論-養成篇”, 台灣

電板產業學院, 全華

科技2005.

-

清大奈微所饒達仁教授

多層PCB

Ref: “印刷電路板

概論-養成篇”, 台

灣電板產業學院, 全華科技2005.

VIA(用以提高

接線密度)

HOLE

-

清大奈微所饒達仁教授

66

ReliabilityReliabilityReliability

-

清大奈微所饒達仁教授

67

IC Package Reliability•

Problems in packaging affect your bottom line!

•

IC world has 40 years on the learning curve

-

清大奈微所饒達仁教授

68

Reliability

圖5.3 黏晶膠內吸收的水份加熱後蒸發成水蒸氣

而在黏晶膠內形成孔洞. (a)吸收的水份少, 孔

洞小; (b)吸收的水份多, 孔洞大, 造成爆米花

現象, 而產生剝離.

-

清大奈微所饒達仁教授

69

Failure Mechanisms and Design for Reliability

-

清大奈微所饒達仁教授

70

How to Solve the Reliability Problem?

-

清大奈微所饒達仁教授

71

Qualifying Packages•

How do you know your package is OK?–

US Military standard 883: how to test microelectronics

–

As a publicly available standard, specific testing methods are supported by test equipments

–

Also used in industry–

Failure mechanism well understood

•

US Military spec. available on-line•

http://www.dscc.dla.mil/programs/milspec/

default.asp•

Search for MIL-STD-883

•

7.7 Mbytes (685 pages)

http://www.dscc.dla.mil/programs/milspec/default.asphttp://www.dscc.dla.mil/programs/milspec/default.asp

-

清大奈微所饒達仁教授

72

Die Attach Strength•

Die shear strength (2019.5)–

Die shears

–

Die separates from DA –

Die and die attach separate from package

•

Failures: –

min shear strength (1.0X)

–

Die separation

-

清大奈微所饒達仁教授

73

Pull Test Used to Test Bond Integrity

-

清大奈微所饒達仁教授

74

Is a Sealed Package Hermetic?

•

Package leak rate–

MIL-STD 883 1014.9: leak rate < 5E-8 atm

cm3/s for

small packages –

0.1 cm3

takes about 3 weeks to exchange gas

–

Vacuum sealed package? •

Package moisture content–

MIL-STD 883 1018.2

–

Moisture < 5000 ppm–

Need low leak rate!

•

Hard to qualify packages for 20+ year lifetime!

-

清大奈微所饒達仁教授

Future TrendFuture TrendFuture Trend

75

-

清大奈微所饒達仁教授

76

IC產品特性驅動封裝技術 之演進及變革

Ref: 微系統封裝原理與技術, 邱碧秀著, 滄海書局, 2005

-

清大奈微所饒達仁教授

77

Evolution of Package Type

-

清大奈微所饒達仁教授

78

Future Trend

Flip-Chip

plus CSP

MCM

& PCB

solder bonding

-

清大奈微所饒達仁教授

79

Thank You!Thank You!Thank You!饒達仁教授饒達仁教授

((清華大學奈米工程與微系統研究所清華大學奈米工程與微系統研究所))

工程一館工程一館510510室室(03)5715131~42850(03)[email protected]@mx.nthu.edu.tw

先進電子封裝設計導論�(Introduction to IC Packaging)Outline投影片編號 3Why Worry About Packaging?Traditional IC PackagingAn Overview of Packaging ProcessTypical Electronic Packaging Hierarchy投影片編號 8Chip-Packaging InterconnectionIC Package Families投影片編號 11投影片編號 12Glossary of AcronymsPackaging DesignIC Packaging DesignMicroelectronic (IC) PackagingPackaging in Electrical DesignDelay Caused by PackageMicrosystem with Interference and NoiseInterference ProblemThermal ManagementCooling Design for ProductsMechanical Design:�Ex: Stress MismatchThermomechanical Deformation in Solder JointsMultidisciplinary Issues In Package DesignManufacturing�(Wafer and Chip Bonding)Bonding Techniques on Each LevelClassifying Wafer BondingFusion Wafer BondingAnodic BondingEutectic BondingApplication of Eutectic Bonding (Au-Si Eutectic Bonding)Example of Au-Si Eutectic BondingWafer Bonding ComparisonWafer Bonding SystemsManufacturing �(Chip Bonding and Interconnection)First Level Package投影片編號 38Al or Au Wedge Wire Bonding投影片編號 40Tape Automated Bonding (TAB/TCP) Procedure投影片編號 42Flip-Chip Bonding投影片編號 44Chip to Module TechnologyTraditional Single Chip Module PackagingModule Assembly SchemesSingle-Chip VS Multichip Module PackagingFunction of Multichip Package Packaging Efficiency of Various PackagesChip Stacked Packaging (CSP)投影片編號 52CSP VS Stacked MCM3D PackagingEnclose and Encapsulation Seal and EncapsulationWays for EncapsulationPCB Technology�(Second Level Packaging)投影片編號 59印刷電路板在電子產業中的定位基板材料之應用印刷電路板結構分類PCB Interconnection線路製作流程多層PCBReliabilityIC Package ReliabilityReliabilityFailure Mechanisms and Design for ReliabilityHow to Solve the Reliability Problem?Qualifying PackagesDie Attach StrengthPull Test Used to Test Bond IntegrityIs a Sealed Package Hermetic?Future TrendIC產品特性驅動封裝技術之演進及變革Evolution of Package TypeFuture TrendThank You!