Interface- und Kommunikationssynthese€¦ · – Kommunikations-Semantik: synchron / asynchron,...

Transcript of Interface- und Kommunikationssynthese€¦ · – Kommunikations-Semantik: synchron / asynchron,...

Interface- undKommunikationssynthese

Hw-Sw-Co-Design

Kommunikation und Interfaces

Motivation

Grundlagen

Systematisierung

Standards

Modellierung

Select

Integrate

Block ConstraintsSpec

Systemebene: Exploration

$ExternalInternal

Idea

VCs

Kommunikation und Interfaces

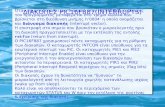

Beispiel– Prozess benötigt insgesamt 100 Sekunden CPU-Time

• 90 Sekunden für Berechnungen• 10 Sekunden für I/O (Kommunikation)

– Annahme: CPU-Leistung steigt pro Jahr um 50%– Frage: Wie viel mal schneller läuft der Prozess in

fünf Jahren?

0102030405060708090

100

CPU IO Gesamt % IO

012345

Kommunikation und Interfaces

Motivation

Grundlagen

Systematisierung

Standards

Modellierung

Kommunikation und Interfaces

Partitionierung– kommunizierende Einheiten– HW-HW, HW-SW, SW-SW

Schnittstellen– notwendig– Entwurf– Test– Integration

Eigenschaften– Bandbreite– Protokoll– Datenkodierung, Datenformat

Kommunikation und Interfaces

Kommunikation– Datentransfer zwischen Sender- und Empfängerprozess– hohe Abstraktionsebene

Interfaces– Schaltungen, Device driver– niedrige Abstraktionsebene

S E

asynchrone/synchrone Kommunikation

asynchrone Kommunikation

synchrone Kommunikation

S EBufferwrite read

S Ewrite read

(OCCAM, ADA)

FIFOs (first-in, first-out)

unbounded FIFO

bounded FIFO

S Ewrite read

inf

S Ewrite read

k

Read-modify-write

binäre, zählende Semaphore

Schutz gemeinsamer Ressourcen durch gegenseitigen Ausschluss (mutual exclusion)

S E

Datenstruktur

put() get()

writeread

Monitor (Modula-II)

Kommunikationsmodelle

Transmitters Receivers Buffer size Blockingreads

Blockingwrites

Asynchronous many many finite no no

Synchronous(Rendezvous) one one (one) zero yes yes

UnboundedFIFO one one unbounded yes/no no

BoundedFIFO one one bounded yes/no yes/no

Read-modify-write many many finite yes/no yes/no

Hardwareinterfaces (1)

asynchron– kein gemeinsamer Takt– Handshakeleitungen

S E

data

rdyack

clk1 clk2

rdy

ack

data

Hardwareinterfaces (2)

synchron– ein gemeinsamer Takt

S E

data

clk

control

clk

data

Softwareinterfaces

low-level interfaces

device drivers

user processes

RTOS (real-time operating system)

ISR (interrupt service routines)

Hardware

Kommunikation und Interfaces

Motivation

Grundlagen

Systematisierung

Standards

ISO / OSI ReferenzmodellTr

ansp

ort

Anw

endung

TCP / IP und ISO/OSI

Transmission Control Protocol / Internet Protocol– Vier Kommunikationsebenen

• Applikation: Authentifizierung, Kompression• Transport: Kontrolle des Datenfusses• Netzwerk: Paket Routing• Link: OS Device Driver

– Ebenen 5 / 6 / 7 des OSI Modells werden zusammengefasst– Sichere Übertragung wird nicht garantiert

Datenstrom im ISO/OSI Modell

Interface-SyntheseAbbildung von Kommunikation auf Interfaces – Kommunikations-Semantik: synchron / asynchron, …. – viele existierende Interfaceprotokolle: Interrupts, DMA,

dedicated ports, CAN, shared memory, …. – constraints: existierende I/O Module, Pinbeschränkungen, ...

Problemstellungen – formale, automatisierbare Methoden – Synthese mit minimalem Overhead (Hardware / Software) – Interfaces in dynamisch rekonfigurierbarer Hardware

(FPGAs)

Interfaces zwischen – HW / HW, SW / SW, HW / SW

Klassifikation - Interfacesynthese (1)

manual – zur Zeit am häufigsten verwendete Methode – große Anzahl von Standards und proprietären Protokollen

erschwert die Entwicklung automatisierter Methoden

library-based – komplette und getestete Schaltungen / Device Driver – wenn Plattform fix ist und wenige Komponenten hat

template-based – Codefragmente, die zur Synthesezeit angepasst werden

(Bsp: #define IOAdress <address> ) – größere Flexibilität als library-based, dafür mehr

Fehlerquellen

Klassifikation - Interfacesynthese (2)

pattern-based – pattern beschreiben typische Interface-Schemata, stellen

aber keine konkrete Implementierung dar – Wiederverwendung von Wissen, um Interfaces (manuell) zu

erzeugen

generator-based – zur Zeit noch wenige Ansätze, da die Komplexität und

Heterogenität der Komponenten groß ist – bekannte Ansätze:

• formale Beschreibungen von Timing-Diagrammen • Signal Transition Graphs

– kommerzielles tool: VCC (Cadence), Mischung aus library-based und generator-based

Klassifikation - Interfacesynthese (3)

component-based (IP) – Standard-Interfaces zwischen Komponenten eines Systems-on-a-

Chip, dadurch einfache Inter-Komponenten Kommunikation – Problem: Kompatibilität zwischen IP cores verschiedener

Hersteller ?

Beispiel: AMBA Advanced Microcontroller Bus Architecture (ARM Ltd.) – offener Standard einer on-chip Bus Spezifikation für Plattform-

basierte Designs (SoC) – IP Module: eingebettete Prozessoren, Speicher, periphere

Einheiten – Wiederverwendbarkeit der Module durch gemeinsamen “backbone”– 2 on-chip Busse mit einer Bridge verbunden

• high-speed bus: verbindet Prozessoren, DMA controller, on-chip memory, high-performance units

• low-speed, lower-power peripheral bus: einfacheres Protokoll, verbindet Timer, GPIO, SIO, ….

Beispiel: AMBA

Advanced Microcontroller Bus Architecture(ARM Ltd.) – offener Standard einer on-chip Bus Spezifikation für

Plattform-basierte Designs (SoC) – IP Module: eingebettete Prozessoren, Speicher, periphere

Einheiten – Wiederverwendbarkeit der Module durch gemeinsamen

“backbone”– 2 on-chip Busse mit einer Bridge verbunden

• high-speed bus: verbindet Prozessoren, DMA controller, on-chip memory, high-performance units

• low-speed, lower-power peripheral bus: einfacheres Protokoll, verbindet Timer, GPIO, SIO, ….

?

?

The Comprehension Boundary

The Abstract Model: Implementation Options:

ResetColor_DataIntensity_Data

Bulb 1

Bulb 2Data_InReq / AckTrigger

Bulb On

Bulb Off

SetReset

Set

Reset

Data

ConceptMaturity

From Comprehension to Interoperability

?

Provider Integrator

Block B

+

ComprehensionStandard

DocumentationPractices

Build Interface

Block ABlock A

Block ABlock A

Interoperability

Key Concept: Interface-Based Design

Implementation Options:

Intensity_Data

ResetColor_Data

Protocol 1

Data_InReq / AckTrigger

Protocol 2TriggerData

TriggerData

The Abstract Model:

Bulb On

Bulb Off

SetReset

Trigger

Data

ResetColor_Data

Protocol 1

Data_InReq / AckTrigger

Protocol 2TriggerData

TriggerData

Intensity_Data

Comprehension• Interface Specification

TriggerBulb On

Bulb Off

SetReset

Data

Inter-Operability• Standardised Interfaces• Data Types

RS232 Interface

Serielle DatenübertragungDefinition im Standard

RS232 Interface

Interfacesynthese

Berücksichtigung von Constraints– Applikation (Task)

• Sender oder Empfänger– Protokoll

• Synchron / asynchron …• Einfügung von Kontrolldaten

– Kanal• Physikalischen Eigenschaften

TaskTasks

Protocol

Medium

Kommunikation und Interfaces

Motivation

Grundlagen

Systematisierung

Modellierung

Standards

Interface - Modellierung

UML: Klassen – SequenzdiagrammeStrukturierung

Applikation Kanal

Target Platform

ProtocolIFB

Restrictions

Task

Medium

Modellierung: Kanal

Kanal: Medium & Protokoll

PhysicalProperties

MaxBitRateLatency

offers <<implements>>

consists of1..n

1

1

1

1

1

1..n

1..n

1

1

1

1

1..n

0..n

1fits to

hasschedule

buildthrough

owns

supports

consists of

1

1

consists of

2..n

includes

V24 Firewire USB

Medium

Protocol

SUBD RJ45 USB

USB BUSB A9 Pin 25 Pin

Connector

Gender

IF_Channel(from System)

KoaxialWire

KoaxialWire

TwistedPair

Protocol:Firewire

Protocol:V24

Protocol:USB

Timing1..n

Bit

Value

Paket

IDBit

Channel

Modellierung: Applikation

Task: Daten & Timing

hasapplied

set

Interface –Arrival-Time

Task

TimeRestrictions

currentTime

pretend

UseData access

ControlData from IFB

Data

consistsof

Deadlines

ComputationTime

Latency SequenceDiagram

ActivityDiagram

input for

input for

fitsto

inputfor

inputfor

Interface –Present-Data

currentData

pretend

DataDependency

predict

inputfor Computed

Data

Data Baseor Register

is at is at

<<dependency>>

ComputedData

Data Baseor Register

Algorithm

HW-Block

Statechart

IF_IFB(from Application Pck.)

Modellierung: Target - Platform

Target-Platform: HW & SW

RecommendedHDL-Code

HW-Target

uses

MaxClockRateSlack

#I/O-Pins#ComponentsVoltageLevels

PhysicalProperties

SynthesisProcess

owns

ProhibitedHDL-Code

pretends

describedby

ComponentLibrary

has11..n

FPGA

offers

Target Platform SW-Target

consistsof

consistsof uses

is a

is a is a

is a

µC

SWLibrary

CodegenerationProcess

has

1 1..n

Recommended Code

offers

TechnicalRequirements

Spyder Altera

Implementeirung der Anbindng

Interface Block

Channel

(from Channel Pck.)

IF_Channel

<<implements>>

IF_Block (IFB)

1..n

1

1..n

1

communicates

IF_IFB

(from Application Pck.)

Task

(from Application Pck.)

1

1..n

1

1..n

communicates

<<implements>>

Interface Block

IFB: Control Unit + Sequence Generator+ Protocol Generator

ProtocolGenerator

Channel(from Channel Pck.)

IF_Block (IFB)

Protocol(from Channel Pck.)

PG_Protocol

IFB Control

<<realizes>>

1

1

1

control SG

1

control PG

1 1hasControl Unit

SequenceGenerator

1

1

has

1

1

has

<<implements>>

IF_IFB(from Application Pck.)

1

1..n

control Task

preparedata

1 1 1 1

bus access

1

1..ncan generate

1

1..n

<<implements>>

<<dependency>>

1 1protocoltemplate

data template 11

must fitSG_Sequence 1 1

can generate

Kooperierende Automaten

Basis für Implementierung

controls

CUFSM

CHANNEL

T1 T2 S1 S2 S3 P1 P2

activates

status

PGFSM

SGFSM

TaskFSM

data

handshake status

Kooperierende Automaten

Sequence Generator (SG)– Kommunikation mit zugehörigen Tasks– Adaption von Daten an die Zieltask– Input für den Protokoll Generator

Protocol Generator (PG)– Erstellung der unterschiedlichen Protokolle– Steuerung des Buszugriffs– Realisierung meist in HW

Control Unit (CU)– Steuert die Kommunikation im IFB– Steuerung des Buszugriffs– Ermöglicht Echtzeitverhalten

Beispiel: V24-IFB (I)

V24: Protokol Generator

V24: Automaten-KommunikationV24

PGSGTask

CUIFB

D_OUT

D_IN

RD_E

WR_E

Pro

toco

lG

ener

ator TXD

RXDSeq

uenc

eG

ener

ator

Task

Direction

MotorNo.

Value

Handshake

CHANNEL

TXDGenerate

Ctrl-Signals

D_INRD_E

WR_E

CLK

RXDCounterClock

division

CounterClockdivision

D_OUT

Protocol Generator

ResetV24 S/P

P/S

realized as hardware module

V24

PGSGTask

CUIFB

Kommunikation und Interfaces

Motivation

Grundlagen

Systematisierung

Modellierung

Standards

Three Standards for System DesignCommon Comprehension:

The System-Level Interface (SLIF) – Behavioral Documentation Standard– Relates communication principles to implementation protocol– Common and complete documentation of interfaces

Common Inter-Operability Constraints:The On-Chip Bus Virtual Component Interface– Defines a common “bus-wrapper”– HW VCs can be authored to the common bus wrapper

The System-Level Data-Type Initiative– Defines a common set of type configurations– Defines a common set of type operations

SLIF - Standard: The System-Level Interface

Behavioral DocumentationStandard

Transaction, Attribute Typing & Protocol Def.

Protocol X

Port Attributes

Port StructuralDescriptors

Port A

Port B

Port C

Port D

Port E

dataType

eventType

event Type

dataType

dataType

Type Name

Port BehavioralDescriptors

transWrite

transEmit

transSense

transReadtransWritetransOpenChanneltransCloseChannel

transWrite

Port Transactions

VCInternal Behavior

SLIF Behavioral: Transaction ClassesSystem-level transactions for interface abstractions– messSense, messEmit– transReadObject, transWriteObject– transOpenChannel, transCloseChannel– transSynchronize - to synchronize operation without the necessity for

data-transfer– transControl - to alter interface operational mode– messReset

Transaction “classes” do not define implementation – Actual VC model may reduce the system-level transactions into any suitable

implementation standard (e.g., OMI)

– Any relationship between an abstract transaction and an implementation must be given

SLIF Behavioral: Attribute ClassesDefines attributes of a transactions Attributes:Control Class -– Blocking / Non-blocking– Priority – Exceptions handled / not handledData- Handling Class – Buffered / Non-buffered– Queued– Persistent– Pipelined– Multi-rate

Transactions / attribute classes provide the structure for presenting any detailed functional descriptions

Computation Domain Implications:e.g., Data-Flow

Blocking Read / Non-Blocking Write

Infinite

Concept Explicitly Supported

FIFO

Data-Flow Q

MemoryAddress

Q CntrlQ Cntrl

Data-Flow Q

MemoryAddress

Q CntrlQ Cntrl

SLIF Interface Hierarchy: Basic ConceptKey: Guarantee consistency of communication during refinement!

Conceptual Information Flow between tasks

Legacy Components:Layers Documented, Executables Optional

MemoryAddress

Q Cntrl

Bus Transactio

ns

(e.g., V

CI)

Non-Blocking Write

(NBW)

Blocking Read

(BW)Task A(VC)

Task B(VC)

Layer 1.0 Channel

Q

OCB - Standard:

The On-Chip Bus Virtual Component Interface

The Principle of the OCB VCI

Problem:– VC exchange is inhibited by the need to implement multiple

components to support different bus standards

Constraints:– Cannot restrict integrators choice in bus– Must provide common interface standard for VC authoring

Solution:– The “Virtual Component Interface”

• Common Interface Requirements for a VC• Simple protocol translators can be fit to any SoC

bus

VC Provided by Vendor

OCB VCI: The “Wrapping” Concept

Initiator Target

VCI

VCI VCI

VCI

Bus of SoC Integrator’s Choice

Master Wrapper Slave Wrapper

“Looks” point-to-point

Critical Element of Standard:• Efficient VCI for Low-Overhead Wrappers

OCB VCI: The BVCI Protocol

Initi

ator

Targ

et

Request Control

Request Details

Response Control

Response Details

valid

ack

details

Indentical for Request and Reply

OCB VCI: The BVCI Components

Op-Codes and Flags:– Command: nop, R, W, R-lock – Address modes: random, contiguous address, wrap,

FIFO

Packet Length and Chaining:– p_len (1 - 511 bytes or undefined), eop– c_len (count down over chain)– c_fixed (cmd, contig, wrap, etc.)

Address, Enable and Data:– address: as defined by flags– be: byte enable– data: separate read and write data-lines

OCB VCI: The BVCI Parameters

To allow the BVCI to be tuned to the specific OCB’s:

– Cell Size– Number of Error Bits– Number of Command Bits– Number of Chain-Length Bits– Split Cycle Actually Supported

SLIF Standard

VCI Transactions AVCI

BVCI

OCB VCI: The VCI DevelopmentPeripheral VCI:– 2 Wire Interface (non-split)– Read, Write, Burst– Error Reporting

Basic VCI:– 4 Wire Interface (split)– Read, Write, Read-Lock, Nop– Packet, Packet-Chain– Error Reporting

Advanced VCI:– Multi-Packet Model– Extended error/status and command set– Support for multi-threading

The VCI Transaction Language

PVCI

Top-Down Linkto Implementation