FFT IP Spec - disp.ee.ntu.edu.twdisp.ee.ntu.edu.tw/kinomoto/paper/FFT_SIP_Spec.pdfGeneral purpose...

Transcript of FFT IP Spec - disp.ee.ntu.edu.twdisp.ee.ntu.edu.tw/kinomoto/paper/FFT_SIP_Spec.pdfGeneral purpose...

-

1

Silicon Intellectual Property

nGeneral purpose high-speed pipelined 2 -point FFT/IFFT

960223

1 2

3 IP 4

-----------------------------------------------------------------------------

-

2

1 FFT/IFFT 2

1

2 81632641282565121024 radix2 FFT/IFFT

3 FFT/IFFT S/P S/P 4 802.11a/g 20MHz 80MHz 1 length 2 81632641282565121024

FFT/IFFT

3

4 Tr.txt Ti.txtFFT 5 Rr.txt Ri.txtIFFT 1 802.11a/g 3 81632641282565121024 FFT/IFFT

4 FFT/IFFT 1 MATLAB function 2 Verilog-XL 3 nLint IP 4 DFT Compiler 5 Synopsys Design Vision 1 MATLAB FFT/IFFT 2 Verilog-XL behavior 3 dump MATLAB 4 Synopsys Design Vision 5 23 Gate Level

-

3

1 Xilinx FPGA FPGAVirtexXC2V15002 length802.11a/g 1 802.11a/g 2 FFT/IFFT 3 MIMO-OFDM

(Abstract) IEEE 802.11 a/g (OFDM)

OFDM /(FFT/IFFT)

1.

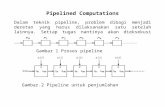

1.1 FFT/IFFT (Functional Description and Architecture) (multicarrier)(subchannel)802.11

a/g OFDM

1-1 FDM OFDM

1-1 FDM OFDM

1-2

-

4

1-2 (a)(b)

(IDFT)(DFT)

(FFT)

1.1.1

FFT/IFFT -

802.11a/g 64 FFT/IFFT

1-3

1-3 IFFT

1-3

1-2

1-2

-

5

1.1.2

1-3 64 FFT/IFFT

1-3 64 FFT/IFFT

1-4

1-4 CLOCK 0~CLOCK 32

1-4 Xin XrXi

Xout XoXio

MUX1 1 1-4 Xin FIFO

FIFO 32 CLOCK 97~128

33 CLOCK MUX1 MUX3 MUX1 0 MUX3

-

6

0 FIFO 1-5

a

1-5 CLOCK 0~CLOCK 32

FIFO 32 CLOCK 65 CLOCK

MUX3 1 1-4 FIFO

Buffer 6

1.1.3

1-6 64 FFT/IFFT radix2

64 FFT/IFFT 32 CLOCK

32 FFT/IFFT 16 CLOCK

1-6

1-7

1-6 64 FFT/IFFT

-

7

1-7 64 FFT/IFFT

1.2 (Key Feature and Claims)

802.11a/g 64 FFT/IFFT 20MHz

radix2 8163264128256512

1024 FFT/IFFT

1.3 (Configuration Information and Parameters)

length FFT/IFFT IP

radix2 1-10 8

16 32 64 128 256 512 1024 FFT/IFFT

GUI

FFT/IFFT

16 testbench length

*4 bits 2 testbench length *1 bits

-

8

fftifftsel FFT IFFT

rst

clk

1.4 (Comprehensive Technical Specification and Data Sheet)

1.4.1 FFT/IFFT

N DFT(Discrete Fourier Transform) 1

0[ ] [ ] 0 , 1 . . . 1

Nn k

Nn

X k x n k NW

1.1

NIDFT(Inverse Discrete Fourier Transform) 1

0

1[ ] [ ] 0 , 1 , . . . 1N

n k

Nn

x k X n k NN W

1.2

( 2 / ) 2 2c o s ( ) s i n ( )n k j N n kNn k n kj

N NW e 1.3

DFT IDFT 2 W

IDFT N DFT

IDFT FFT/IFFT 2N Radix-2

Radix-4Radix-2/4

1.4.2 Radix-2 FFT

(1.1) k = 2r(1.4) 1

( 2 )

0( / 2 ) 1 1

2 2

0 / 2

( / 2 ) 1 ( / 2 ) 12 2

0 0

( / 2 ) 1

/ 20

[ 2 ] [ ]

[ ] [ ]

[ ] [ ( / 2 ) ]

( [ ] [ ( / 2 ) ] )

Nn r

NnN N

n r n r

N Nn n N

N Nn r s r N r

N N Nn s

Nn r

Nn

X r x n

x n x n

x n x s N

x n x n N

W

W W

W W W

W

(1.4)

/ 2n s N ( 2 / ) ( 2 ) 1N r j N N r j rNW e e 2 ( 2 / ) 2 ( 2 / ( / 2 ) )

/ 2

n r j N n r j N n r n r

N NW e e W

(1.1) k = 2r + 1(1.5)

-

9

1( 2 1 )

0( / 2 ) 1 1

( 2 1 ) ( 2 1 )

0 / 2

( / 2 ) 1 ( / 2 ) 12 2 / 2

0 0

( / 2 ) 1

/ 20

[ 2 1] [ ]

[ ] [ ]

[ ] [ ( / 2 ) ]

( [ ] [ ( / 2 ) ] )

Nn r

Nn

N Nn r n r

N Nn n N

N Nn r n s r s N r N

N N N N N Nn s

Nn n r

N Nn

X r x n

x n x n

x n x s N

x n x n N

W

W W

W W W W W W

W W

(1.5)

/ 2n s N 1N rNW / 2 ( 2 / ) / 2 1N j N NNW e 2 ( 2 / ) 2 ( 2 / ( / 2 ) )

/ 2

n r j N n r j N n r n r

N NW e e W

[ ] [ ] [ / 2]g n x n x n N [ ] ( [ ] [ / 2]) nNh n x n x n N W ( / 2) 1

/ 20

( / 2) 1

/ 20

[2 ] [ ]

[2 1] [ ]

Nnr

Nn

Nnr

Nn

X r g n

X r h n

W

W

(1.6)

radix 2

64

FFT/IFFT 1-11

-

10

1.4.3 Radix-2 FFT

1-8 N=64 Radix-2

-

11

2.

802.11a/g FFT/IFFT 64 16bits

ASIC FPGA

2.1 Provided Design Models

1-12 Verilog code

FFT/IFFT

Matlab FFT/IFFT

1-9

2.2

ASIC FPGA

-

12

2.2.1 ASIC

FFT/IFFT tsmc .18

Synopsys design division Verilog code

37bits xr16bitsxi16bits

fftifftsel FFT IFFTrst1bitclk1bit

xo16bitsxio16bits

gate level

2.2.2 FPGA

FFT/IFFT

XILINX

ISE 6.1

ModelSim XE II 5.7c

FPGA ISE

FPAGROMROM

Download Pattern Generator

LA

-

13

FPGA XILINX VirtexII XC2V1500

Pattern Generator

PG2050 50

ChannelsInternal Clock Range 100MHz

~1Hz

LA

LA2132P Sample Rate 200 MHz

100 Hz32 Channels

2.3

802.11a spec

2-1 802.11 ab

MATLAB 64 ifftshift

ifft fft fftshift

Matlab

3. IP

3.1 Application method ( IP?)

- FFT/IFFT

CORE

-

14

GEN FFT/IFFT

3.2 Application example

802.11aFFT/IFFT

FFT/IFFT

3-1 IEEE 802.11a