cours_Xilinx_2006

-

Upload

beau-algerie -

Category

Documents

-

view

220 -

download

0

Transcript of cours_Xilinx_2006

-

8/7/2019 cours_Xilinx_2006

1/113

Les circuits FPGA

Concepts de base, architecture et applications

Cours Master Recherche

S ystmes Intelligents et Communicants

Franois Verdier

www-etis.ensea.fr/~verdier/

Universit de Cergy-Pontoise Laboratoire ETIS - UMR CNRS 8051

-

8/7/2019 cours_Xilinx_2006

2/113

Plan du coursPlan du cours

1 - Technologie et densit

2 - La famille des circuits logiques

2.1 - Les fonctions logiques

2.2 - Les technologies

3 - Architecture des FPGA XILINX3.1 - Architecture gnrale

3.2 - Les interconnexions

3.3 - Les CLB

3.4 - Les IOB

3.6 - La configuration des

circuits3.5 - Les canaux de routage

3.6 - La mmoire interne

3.7 - Configuration des FPGA

3.8 - Evolution des produits

4 - Mthodologie de conception

4.1 - Le flot de conception

4.2 - LesIntelectual Properties

4.3 - La production en volume

5 - Applications : Les FCCM5.1 - Exemples de machines5.2 - Le CoDesign

6 - La reconfiguration dynamique

7 - Des FPGA aux SOPC7.1 - Architecture Virtex2-Pro

7.2 - Architecture Virtex47.3 - ALTERA Excalibur-ARM

7.4 - XPP de PACT

8 - Conclusion

9 - Pistes

-

8/7/2019 cours_Xilinx_2006

3/113

1 - Technologie et densit

Les systmes lectroniques modernes sont de plus en

plus complexes,

Les contraintes de taille, de puissance dissipe et de

performances sont de plus en plus svres (tlphoniemobile, ordinateurs, traitement du signal, de l'image,

etc...).

Accroissement spectaculaire des densits.

-

8/7/2019 cours_Xilinx_2006

4/113

Les techniques de circuit imprims trousLes techniques de circuit imprims trous

traversantstraversants

Carte en fibre epoxy

Pistes de cuivre

Trous mtalliss

Insertion des

composants

Soudure

Densit limite par la surface !

-

8/7/2019 cours_Xilinx_2006

5/113

Les techniques de circuit imprims Les techniques de circuit imprims

montage en surfacemontage en surface

Carte en fibre epoxy

Pistes en cuivre

multicouches

Dpt et collage

des CMS

Composants sur les deux faces !

Densit multiplie par 10

-

8/7/2019 cours_Xilinx_2006

6/113

Les contraintes physiques, technologiques et commerciales

imposent aujourd'hui la conception de systmes de plus en

plus :

- compacts,

- conomes en nergie,

- rapides concevoir,

- fiables et peu coteux.

La contrainte de time to market devient la plus

importante et rend inefficace dsormais les cycles classiques

de dveloppement / vrification / ralisation physique.

=> besoin d'une technologie fiable, abordable et souple...

-

8/7/2019 cours_Xilinx_2006

7/113

2 - La grande famille des circuits2 - La grande famille des circuits

logiqueslogiques La logique standardLa logique standard

Les mmoires (RAM, PROM, EPROM...)Les mmoires (RAM, PROM, EPROM...)

Les rseaux logiques programmables (PLA, PLD,Les rseaux logiques programmables (PLA, PLD,

EPLD, CPLD...)EPLD, CPLD...)

rseaux ET/OUrseaux ET/OU

technologie fusibles/anti-fusiblestechnologie fusibles/anti-fusibles

rseaux logiques programmables sur site (FPGA)rseaux logiques programmables sur site (FPGA)

technologie RAM/SRAMtechnologie RAM/SRAM

logique LUTlogique LUT

-

8/7/2019 cours_Xilinx_2006

8/113

2.1 - Les diffrentes techniques de2.1 - Les diffrentes techniques de

ralisation dralisation dune fonction logiqueune fonction logique

S = (A . B) +S = (A . B) +

CC

BB

CSS

-

8/7/2019 cours_Xilinx_2006

9/113

2.1.1 - La logique standard2.1.1 - La logique standard

Utilisation de circuits TTL / CMOS ...Utilisation de circuits TTL / CMOS ...

SS

74087408 74327432

densit :

-

8/7/2019 cours_Xilinx_2006

10/113

2.1.2 - La logique mmoire : LUT2.1.2 - La logique mmoire : LUT

partir d partir dune table de vritune table de vrit

S = (A . B) + CS = (A . B) + C

C B A S0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 11 0 1 1

1 1 0 1

1 1 1 1

et det dune mmoire (8x1bit)une mmoire (8x1bit)

0

0

0

1

11

1

1

A

B

C

S

-

8/7/2019 cours_Xilinx_2006

11/113

2.1.3 - Les connexions2.1.3 - Les connexions

programmables : Les circuits PALprogrammables : Les circuits PAL

rseau de portes ET

rseau de portes OU

A

B

C

S = A.B + C

LLquation se programme sous sa premire formequation se programme sous sa premire forme

canonique (somme de produits)canonique (somme de produits)

A.B CConnexions base

de fusibles

-

8/7/2019 cours_Xilinx_2006

12/113

2.1.4 - Les FPGA2.1.4 - Les FPGA

(Field Programmable Gate Array)(Field Programmable Gate Array)

LUT

LUT

LUT

LUT

Un ensemble de mmoires LUTUn ensemble de mmoires LUT

Un ensemble deUn ensemble de

chemins dechemins deroutageroutage

A

B

C

ET

OU S = A.B + C

Programmation des mmoiresProgrammation des mmoires

et tablissement des connexionset tablissement des connexions

-

8/7/2019 cours_Xilinx_2006

13/113

2.1.4 - Les FPGA2.1.4 - Les FPGA

A

B

C

ET

OU S = A.B + C

Cellule mmoire

Connexions par transistors MOSConnexions par transistors MOS

-

8/7/2019 cours_Xilinx_2006

14/113

2.2 - Classification des technologies2.2 - Classification des technologies

Logique standardLogique standard

LogiqueLogique

ASICASIC

PLDPLD

PALPAL CPLDCPLD

EPROMEPROM

EEPROM/FLASHEEPROM/FLASH

FPGAFPGA

anti-fusiblesanti-fusibles

SRAMSRAM

-

8/7/2019 cours_Xilinx_2006

15/113

Les circuits FPGA SRAM deviennent des solutions de

remplacement avantageuses pour les systmes numriques

haute intgration.

Les cycles de dveloppement et de prototypage (test et

vrification en conditions relles) sont acclrs et mme

confondus. Spcification

Conception

Vrification

Ralisation

-

8/7/2019 cours_Xilinx_2006

16/113

3 - Architecture des circuits FPGA3 - Architecture des circuits FPGA

(XILINX)(XILINX) Un FPGA ralise une fonction logique complexe. Il estUn FPGA ralise une fonction logique complexe. Il est

programmableprogrammable, et, et re-programmablere-programmable dans sondans son

environnementenvironnement Les circuits FPGA XILINX sont disponibles en deLes circuits FPGA XILINX sont disponibles en de

nombreuses configurations de taille, de vitesse et denombreuses configurations de taille, de vitesse et de

prixprix

Des outils logiciels puissants et automatiquesDes outils logiciels puissants et automatiques

permettent de raliser facilement un systme surpermettent de raliser facilement un systme sur

FPGA.FPGA.

-

8/7/2019 cours_Xilinx_2006

17/113

Evolution de la technologie des circuitsEvolution de la technologie des circuits

FPGA XILINXFPGA XILINX

198 5 /8 6 19 94 1995 19 96/9 7 2000 2 001Nombre de

Tra nsist ors 8 5 K 3 ,5 M 6 M 1 2 M 7 5 M > 1 0 0 MNombre de

Port es 8 0 0 2 5 K 5 0 K 1 0 0 K 5 0 0 K 1 0 M

Couches de

Mt a l 2 3 3 3 - 4 4 - 5 8

-

8/7/2019 cours_Xilinx_2006

18/113

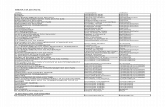

Famille # portes # E/S # bascules # RAM bits # CLB

XC2000* 0.6 - 1.5K 58 - 74 122 - 174 0 64-100

XC3000* 1.3 - 9K 64 - 176 256 - 1320 0 64-484

XC4000 2 - 180K 80 - 448 360 - 7168 3K - 100K 100-3136XC6200* 9K - 100K 192 - 512 2K - 16K 0 2K - 16K

XC4000XV 75K - 500K 448 10K - 20K 131K - 270K 2.5K-5K

SPARTAN 2K - 200K 77 - 284 360 - 2016 16K - 57K 238 - 5292

VIRTEX 58K - 1M 180 - 512 1728 - 27K 32K - 131K 384-6144

VIRTEX2 40K - 10M 88 - 1108 256 - 61K 72K - 3.4M 64-15360*

Les diffrentes familles FPGA XILINXLes diffrentes familles FPGA XILINX

* produits obsoltes

-

8/7/2019 cours_Xilinx_2006

19/113

3.1 - Architecture gnrale3.1 - Architecture gnrale

Un FPGA est un rseau (matrice) deUn FPGA est un rseau (matrice) de

blocs combinatoires et squentiels (CLB)blocs combinatoires et squentiels (CLB)

Des blocs dDes blocs dentre/sortie (IOB) sontentre/sortie (IOB) sont

associs aux broches du circuitassocis aux broches du circuit

Les CLB et IOB sont interconnects entreLes CLB et IOB sont interconnects entre

eux par des dispositifs variseux par des dispositifs varis Les matrices sLes matrices sorganisent de 8x8 organisent de 8x8

128x120128x120

-

8/7/2019 cours_Xilinx_2006

20/113

3.1 - Architecture gnrale3.1 - Architecture gnrale

CLBCLB

IOBIOB

matrices dematrices de

connexionconnexion

lignes delignes de

connectionsconnections

-

8/7/2019 cours_Xilinx_2006

21/113

-

8/7/2019 cours_Xilinx_2006

22/113

3.2 - Les interconnexions3.2 - Les interconnexions

(directes)(directes)

CLB CLB

CLB CLB

2 ns

5 nsDELAIS DEPENDANTDELAIS DEPENDANT

DU ROUTAGE !!!DU ROUTAGE !!!

-

8/7/2019 cours_Xilinx_2006

23/113

3.2 - Les interconnexions3.2 - Les interconnexions

(matrices)(matrices)

CLB CLB

CLB CLB

-

8/7/2019 cours_Xilinx_2006

24/113

3.2 - Les interconnexions (lignes)3.2 - Les interconnexions (lignes)

CLB CLB

CLB CLB

-

8/7/2019 cours_Xilinx_2006

25/113

3.3 - Structure des CLB3.3 - Structure des CLB

Une table de transcodage combinatoire (LUT)Une table de transcodage combinatoire (LUT)

pouvant implanter :pouvant implanter :

deux fonctions indpendantes 4 variablesdeux fonctions indpendantes 4 variables

une fonction complte 5 variablesune fonction complte 5 variables

une fonction incomplte 6 variablesune fonction incomplte 6 variables

Deux cellules squentielles (bascules D)Deux cellules squentielles (bascules D)

Des multiplexeurs de configurationDes multiplexeurs de configuration

-

8/7/2019 cours_Xilinx_2006

26/113

3.3.1 - Structure d3.3.1 - Structure dun CLB 3000un CLB 3000

-

8/7/2019 cours_Xilinx_2006

27/113

3.3.2 - Structure d3.3.2 - Structure dun CLB 4000un CLB 4000

-

8/7/2019 cours_Xilinx_2006

28/113

3.3.3 - Structure d3.3.3 - Structure dun CLBun CLB

SPARTANSPARTAN

-

8/7/2019 cours_Xilinx_2006

29/113

3.4 - Structure des IOB3.4 - Structure des IOB

Ports dentre/sortie totalement programmables :

Seuil dentre TTL ou CMOS

Slew-rate programmable

Buffer de sortie programmable en haute

impdance

Entres et sorties directes ou mmorises

Inverseur programmable

-

8/7/2019 cours_Xilinx_2006

30/113

3.4.1 - Structure des IOB (XC3000)3.4.1 - Structure des IOB (XC3000)

-

8/7/2019 cours_Xilinx_2006

31/113

3.4.2 - Structure des IOB (XC4000)3.4.2 - Structure des IOB (XC4000)

-

8/7/2019 cours_Xilinx_2006

32/113

3.4.3 - Structure des IOB3.4.3 - Structure des IOB

(SPARTAN)(SPARTAN)

-

8/7/2019 cours_Xilinx_2006

33/113

3.5 - Canaux de routage3.5 - Canaux de routage

-

8/7/2019 cours_Xilinx_2006

34/113

Routage inter-CLB

Matrices d'interconnexions

(Programmable Switch Matrix)

3 6 U ili i d CLB3 6 Utili ti d CLB

-

8/7/2019 cours_Xilinx_2006

35/113

3.6 - Utilisation des CLB en3.6 - Utilisation des CLB en

mmoiresmmoires

-

8/7/2019 cours_Xilinx_2006

36/113

-

8/7/2019 cours_Xilinx_2006

37/113

-

8/7/2019 cours_Xilinx_2006

38/113

Mode de configuration srie (EEPROM srie)Mode de configuration srie (EEPROM srie)

Circuit principal Circuits en daisy chain

-

8/7/2019 cours_Xilinx_2006

39/113

Mode de configuration parallleMode de configuration parallle

(EPROM parallle)(EPROM parallle)

-

8/7/2019 cours_Xilinx_2006

40/113

Mode de configuration parallle asynchroneMode de configuration parallle asynchrone

(mode priphrique de processeur)(mode priphrique de processeur)

-

8/7/2019 cours_Xilinx_2006

41/113

3.8 - Evolution des produits3.8 - Evolution des produits

La technologie micro-lectronique continue d'voluer de manire

exponentielle (en densit, en vitesse, en taille et en consommation) :

La taille des puces augmente : les entres/sorties sont plus

nombreuses

La densit augmente : le grain des FPGA augmente

La technologie SRAM se fiabilise : la quantit de mmoire augmente

Les nouvelles familles apparaissent :

- XC4000(X)

- VIRTEX

- VIRTEX-II

- VIRTEX-II PRO

- VIRTEX-4

-

8/7/2019 cours_Xilinx_2006

42/113

La technologie volue (premier FPGA

avec une technologie 0.25 microns)

et la densit des circuits augmente...

...tandis que la consommation

diminue

3.8.1 - XC4000X3.8.1 - XC4000X

-

8/7/2019 cours_Xilinx_2006

43/113

Frquences inter-circuits Frquences intra-ciruits

Les performances augmentent avec

la finesse de la technologie

3.8.1 - XC4000X3.8.1 - XC4000X

-

8/7/2019 cours_Xilinx_2006

44/113

Les produits XC4000(X)

-

8/7/2019 cours_Xilinx_2006

45/113

CLB Logic Block SelectRAM

Device # gate Array Cells RAM bit bits Max I/

XCV50 58K 16 x 24 1728 32768 24576 180

XCV100 109K 20 x 30 2700 40960 38400 180XCV150 164K 24 x 36 3888 49152 55296 260XCV200 236K 28 x 42 5292 57344 75264 284XCV300 323K 32 x 48 6912 65536 98304 316

XCV400 468K 40 x 60 10800 81920 153600 404XCV600 661K 48 x 72 15552 98304 221184 512XCV800 888K 56 x 84 21168 114688 301056 512

XCV1000 1.1M 64 x 96 27648 131072 393216 512

3.8.2 - La famille VIRTEX3.8.2 - La famille VIRTEX

-

8/7/2019 cours_Xilinx_2006

46/113

Acclration

des dlais

de routage

Avec la densit qui augmente,

intgration de la notion

d' Intelectual Properties

(IP = Macro-Cellules tierces)

3.8.3 - La famille VIRTEX-II3.8.3 - La famille VIRTEX-II

-

8/7/2019 cours_Xilinx_2006

47/113

-

8/7/2019 cours_Xilinx_2006

48/113

Protection de la proprit industrielle :

leReverse Engineering est impossible

3.8.3 - La famille VIRTEX-II3.8.3 - La famille VIRTEX-II

-

8/7/2019 cours_Xilinx_2006

49/113

3.8.3 - La famille VIRTEX-II3.8.3 - La famille VIRTEX-II

CLB SelectRAMDevice # gate Array SlicesMax RAM Kbit Multiplier Kbits Max I/

XC2V40 40K 8 x 8 256 8 4 72 88

XC2V80 80K 16 x 8 512 16 8 144 120XC2V250 250K 24 x 16 1536 48 24 432 200

XC2V500500K 32 x 24 3072 96 32 576 264

XC2V1000 1M 40 x 32 5120 160 40 720 432XC2V1500 1.5M 48 x 40 7680 240 48 864 528XC2V2000 2M 56 x 48 10752 336 56 1008 624XC2V3000 3M 64 x 56 14336 448 96 1728 720XC2V4000 4M 80 x 72 23040 720 120 2160 912XC2V6000 6M 96 x 88 33792 1056 144 2592 1104XC2V8000 8M 112 x 10446592 1456 168 3024 1108XC2V1000 10M 128 x 12061440 1920 192 3456 1108

-

8/7/2019 cours_Xilinx_2006

50/113

3.8.3 - Architecture VIRTEX-II3.8.3 - Architecture VIRTEX-II

Matrice de Slices

Blocs d'E/SBlocs de mmoire Multiplieurs 18x18

Gnrateurs d'horloge

-

8/7/2019 cours_Xilinx_2006

51/113

4 - Mthodologie de conception4 - Mthodologie de conception

Les systmes concevoir devenant de plus en plus complexes, les

types de descriptions deviennent de plus en plus varis :- schmas,

- VHDL structurel, fonctionnel,

- ABEL (machines tats), Verilog,

- code C / C++ ?

Plus les systmes deviennent complexes concevoir, plus les

tapes de vrification sont ncessaires :

- simulation fonctionnelle,

- analyse des timings (chemins critiques),

- simulation post-routage (temporelle),...

Avec l'augmentation de la densit des circuits, les notions de

placement gomtrique deviennent indispensables :

- floorplanning

4 1 L fl t d ti4 1 L fl t d ti

-

8/7/2019 cours_Xilinx_2006

52/113

4.1 - Le flot de conception4.1 - Le flot de conception1- Description du systme :

- Schmas (hirarchie),

- code VHDL (Verilog, ABEL)2- Compilation du code VHDL :

- synthse si code fonctionnel

3- Simulation fonctionnelle :

- vrification de la description

4- Placement relatif et estimation du routage :- floorplanning et gestion des contraintes d'E/S

5- Compilation du circuit :

- conversion du Netlist,

- optimisation combinatoire,

- placement / routage des cellules

- retro-annotation temporelle

6- Vrification finale :

- simulation temporelle,

- configuration / validation

-

8/7/2019 cours_Xilinx_2006

53/113

-

8/7/2019 cours_Xilinx_2006

54/113

-

8/7/2019 cours_Xilinx_2006

55/113

-

8/7/2019 cours_Xilinx_2006

56/113

-

8/7/2019 cours_Xilinx_2006

57/113

-

8/7/2019 cours_Xilinx_2006

58/113

LesIP sont des macro-celulles (pr-places et/ou pr-routes)disponibles comme des cellules de bibliothque proposant sous

forme de boites noires des fonctions complexes entirement

simulables et respectant la proprit industrielle.

On transpose directement la mthodologie de conception d'unsystme complexe (associant logique discrte, composants

standards, circuits spcifiques) dans un seul circuit FPGA...

La description complte du systme associe saisie de schmas,

spcifications de haut niveau (structurelle et/ou fonctionnelle)

en langage VHDL ou Verilog et langage C.

4.2 - Les4.2 - LesIntelectual Properties (IP)Intelectual Properties (IP)

-

8/7/2019 cours_Xilinx_2006

59/113

Spcification

C

Spcification

VHDL

Bibliothque

standard

Bibliothque

IPCOMPILATEUR

PLACE & ROUTE

Rtro-

annotation

temporelle

Simulation

Modle de

composant

Programmation

du composant

Validation

-

8/7/2019 cours_Xilinx_2006

60/113

Les bibliothques dLes bibliothques d'Intelectual Properties'Intelectual Properties

IP Type Provider

C2910a Microprogram contr oller CAST Inc.

C8051 Micro Cont roller CAST Inc.

ARC32 32 -bit Conf igurable ARC Cores

RISC Processor

D80530 8-bit Micro Cont ro lle r CAST Inc.

C2901 Microprocessor Slice CAST Inc.W65C02S Micro Processor West ern Design Cent er

Mini-RISC Micro Processor OpenCores.orgOpenRISC-1000 RISC Processor OpenCores.org

LavaCORE Java Microprocessor Der iva t ion System Inc.

Free-RISC8 Microprocessor The Free IP Project

LEON-1 SPARC-com pat ible Eu ropean Space Agen cy

Micro Processor (ESA)

-

8/7/2019 cours_Xilinx_2006

61/113

Les bibliothques dLes bibliothques d'Intelectual Properties'Intelectual Properties

IP Applica t ion

Encodeu r Reed -Solomon Transmission de donn es

Dcodeur Reed-Solomon Transmission de donn esInte rface PCI-X Bus de comm unicat ion

Contrleur HDLC Connect ion couche physique

Codeur/dcodeur ADPCMTransmission, compr ession

4 3 L d i l H dWi4 3 L d i l H dWi

-

8/7/2019 cours_Xilinx_2006

62/113

4.3 - La production en volume : HardWire4.3 - La production en volume : HardWireTMTM

Le cot de production d'une solution sur FPGA devient

considrable sur de grands volumes. Le surcot introduit

par les capacits de re-programmabilit devient prohibitif.

=> Transformation FPGA -> ASIC (Gate Array)

La technologie HardWireTM permet le passage d'une version

prototype (reprogrammable) valide une version de

production en grande srie.

Les cibles FpgASIC sont totalement compatibles et vrifies.

Volume

Dure de vie du produit

Fin de vie

Dbut de production

FPGA FPGA

Circuits FpgASIC

HardWire

5 A li i d FPGA5 A li i d FPGA

-

8/7/2019 cours_Xilinx_2006

63/113

5 - Application des FPGAs :5 - Application des FPGAs :

Les machines (re)configurablesLes machines (re)configurables

L'existence de composants logiques (re)programmables in-situ etperformants conduit un nouveau paradigme de programmation :

la fonction cable reconfigurable

Un traitement complexe se pense dsormais en termes d'oprateursmatriels optimiss configurables et programmables l'infini.

Les FCCM (FPGA-based Custom Computing Machines) deviennent

de rels (co)processeurs de calcul optimiss.

Des traitements coteux deviennent possibles : le temps-rel

embarqu devient possible (codage/dcodage, TI, TS, etc..).

-

8/7/2019 cours_Xilinx_2006

64/113

FPGA

FPGA

FPGA

FPGA

Mem. Mem.

Mem.

Processeur

hte

Le concept de FCCMLe concept de FCCM

Plusieurs circuits FPGARseau d'interconnexion

Mmoiresde travail

5 1 Q l l d5 1 Q l l d

-

8/7/2019 cours_Xilinx_2006

65/113

Machine FPGA Processeur Mmoire Bus

9204/FPGA 2 x XC4025 T9000 64Ko + 8Mo Transputer DS-Lin

DVC1 2 x XC4013 1Mo + FIFOs Sbus

EDgAR-2 4 x XC4013 PCI

Functional M emory Compu8 x XC4010 + 3 x XC4013 1Mo PCI

LIRMM 2 x XC4013 TMS 320C40 2 x 1Mo ISA ou SbusMARC-1 25 x XC4005 6 Mo SbusMORRPH-ISA 6 x XC4025 DdiCARMeN VIRTEX XCV1000 ARM 8Mo + 2Mo PCI, CAN, et c...

OPART 2 x XC4028EX Pent ium + PP 2Mo + FIFO Compact PCI

ARDOISE ATMEL At40K DSP 2Mo / modul Ddi

5.1 - Quelques exemples de5.1 - Quelques exemples de

FCCMFCCM

5 1 1 L hi ARMEN5 1 1 La machine ARMEN

-

8/7/2019 cours_Xilinx_2006

66/113

5.1.1 - La machine ARMEN5.1.1 - La machine ARMENLaboratoire d'Informatique de BrestLaboratoire d'Informatique de Brest

Universit de Bretagne OccidentaleUniversit de Bretagne Occidentale

Processeurs Transputer T805

FPGA XC3090

-

8/7/2019 cours_Xilinx_2006

67/113

-

8/7/2019 cours_Xilinx_2006

68/113

5 2 P ti d FCCM5 2 Programmation des FCCM :

-

8/7/2019 cours_Xilinx_2006

69/113

5.2 - Programmation des FCCM :5.2 - Programmation des FCCM :

LeLe CODESIGNCODESIGN

Application

?

DSP Rseau FPGA

-

8/7/2019 cours_Xilinx_2006

70/113

Les projets d'outils de CODESIGNLes projets d'outils de CODESIGN

COSI IRISA (Rennes) ASIC : Syst em On Ch ip

SYNDEX INRIA Trait em ent du signal

MCSE IRESTE (Nant es) Spcif icat ion pour le Codesign

MOSARTS Univers it de Nice-Ant ipo lis T lcom. : par t i t ionnem ent

LIRMM Un iv e r sit d e M on tp ellie r T lco m . Sy n th se et v rif ica t io n

SKIPPER Univ . de Clerm ont-Ferrand Paral l lisa t ion de code en TICOSMOS TIMA (Grenoble) IP + p rocesseurs classiques

POLIS Univ . de Berkeley Concept ion m ix t e / FSMCOWARE Belgique IP et st andardisat ion

CodeX Un iv . de Kaiser Slau t er n Rseau x m i xt e s sy st o liqu es

CHINOOK Univ . de Wash ingt on Syst m es m ix t es indust riels

Form alisation des langages de descript ion :

Hande lC Anglet er re Langage de descr ipt ion m ix t e (OCCAM)LCC Univ . de Virgin ie Langage m ix t e DSP + FPGA

Sys t emC COWARE / Front ier / SynopsysLangage et com pilat eur C+ + m ixt e

5 2 1 L bl d5 2 1 L bl t d C D iC D i

-

8/7/2019 cours_Xilinx_2006

71/113

5.2.1 - Les problmes ouverts du5.2.1 - Les problmes ouverts du CoDesignCoDesign

Spcification de haut niveau

(C, C++)

Analyse

du code

Bibliothque

standard et IP

Extraction

du paralllisme

Analyse des dpendances

de donnes

Analyse des ressoucesmmoire

Compilateur

squentielDSP

Place / RouteFPGA

Gestion des

communication

s

Modle

d'architecture

-

8/7/2019 cours_Xilinx_2006

72/113

5.2.2 - Le flot classique de conception5.2.2 - Le flot classique de conception

Modle niveau systme

C / C++

ANALYSE

Rsultats de test

Dveloppe

ment

Description

VHDL / Verilog

SIMULATION

SYNTHESE

Traduction

5 2 2 - Un nouveau standard : SystemC5 2 2 - Un nouveau standard : SystemCTMTM

-

8/7/2019 cours_Xilinx_2006

73/113

5.2.2 Un nouveau standard : SystemC5.2.2 Un nouveau standard : SystemC(Synopsys + CoWare + Frontier Design :(Synopsys + CoWare + Frontier Design : www.systemc.orgwww.systemc.org))

Modle SystemC

Amlioration

Modle temporel

Partitionnemen

t

Modle Bus

Amlioration

Modle cycle

synthtisable

Modle abstrait

RTOS

Amlioration

Cible RTOS

Essais d'architectures

Analyse de

performances

Harware / Software

http://www.systemc.org/http://www.systemc.org/http://www.systemc.org/http://www.systemc.org/ -

8/7/2019 cours_Xilinx_2006

74/113

6 La Reconfiguration Dynamique des FPGA6 La Reconfiguration Dynamique des FPGA

Les architectures de type FPGA offrent la possibilit de modifier

la demande lagencement structurel ainsi que la fonctionalit des

ressources internes de la puce.

Lexploitation de ce concept introduit la notion de fonction

cble programmable :

Paralllisme spatial (de donnes)

Paralllisme temporel (pipeline)Flexibilit

La machine ARDOISE (Atmel)La machine ARDOISE (Atmel)

-

8/7/2019 cours_Xilinx_2006

75/113

ARDOISE :

Architecture Reconfigurable Dynamiquement Oriente Image et Signal Embarqu

( )

Action incitative inter-GDR (ETIS)Action incitative inter-GDR (ETIS)

Prototype dun module

Carte mre + 3 modules

Objectifs du projet ARDOISEObjectifs du projet ARDOISE

-

8/7/2019 cours_Xilinx_2006

76/113

Objectifs du projet ARDOISEObjectifs du projet ARDOISE

1. Utiliser la reconfiguration dynamique des FPGA

Reconfiguration totale = 0,8 ms

Reconfiguration partielle possible

Changement dalgorithmes en temps rel sur le mme

circuit

Vitesse des architectures cbles, flexibilit desarchitectures programmables

2. Dvelopper larchitecture, les mthodes et les outils

ARDOISE = prototype exprimental (acadmique)

Applications en segmentation dimages

Applications en camras intelligentes

Application en compression / dcompression dimages

(MPEG)

-

8/7/2019 cours_Xilinx_2006

77/113

Ac quisition, traitem entet visualisation en temps rel

Proc esseur front-end de c ontrle des

c onfigurations ADSP SHARC 21161 Reconfiguration partielle et dynamiquedes c irc uits FPGA ATMEL AT40K40

A hi dARDOISE

-

8/7/2019 cours_Xilinx_2006

78/113

Architecture dARDOISE :Architecture dARDOISE :

ARDOISE = application du principe deARDOISE = application du principe de

-

8/7/2019 cours_Xilinx_2006

79/113

reconfiguration dynamique en traitementreconfiguration dynamique en traitement

d'images :d'images :

Image i

Image i-1

Image i-2

Image i+1

op1 op2

op1

C f i h 1

-

8/7/2019 cours_Xilinx_2006

80/113

Conf. Deriche1

FPGA

GTI1

FPGA

GTI2

GTI1 GTI2

Deriche 1

Mmoire

256kx32

Mmoire256kx32

BC

IN OUT

E D i h 1 / C f D i h 2

-

8/7/2019 cours_Xilinx_2006

81/113

Exec. Deriche1 / Conf. Deriche 2

FPGA

GTI1

FPGA

GTI2

GTI1 GTI2

Deriche 1

Mmoire

256kx32

Mmoire256kx32

BC

IN OUT

-

8/7/2019 cours_Xilinx_2006

82/113

Exec. Deriche 2 / Conf. Contours

FPGA

GTI1

FPGA

GTI2

GTI1 GTI2

Deriche 2

Mmoire

256kx32

Mmoire256kx32

BC

IN OUT

E C / C f F 1

-

8/7/2019 cours_Xilinx_2006

83/113

Exec. Contours / Conf. Fermeture 1

FPGA

GTI1

FPGA

GTI2

GTI1 GTI2

Contours

Mmoire

256kx32

Mmoire256kx32

BC

IN OUT

E F 1 / C f F 2

-

8/7/2019 cours_Xilinx_2006

84/113

Exec. Fermeture 1 / Conf. Fermeture 2

FPGA

GTI1

FPGA

GTI2

GTI1 GTI2

Fermeture1

Mmoire

256kx32

Mmoire256kx32

BC

IN OUT

-

8/7/2019 cours_Xilinx_2006

85/113

E R i 1 / C f i 2

-

8/7/2019 cours_Xilinx_2006

86/113

Exec. Rgion 1 / Conf. rgion 2

FPGA

GTI1

FPGA

GTI2

GTI1 GTI2

Rgion1

Mmoire

256kx32

Mmoire256kx32

BC

IN OUT

E R i 2 / C f D i h 1

-

8/7/2019 cours_Xilinx_2006

87/113

Exec. Rgion 2 / Conf. Deriche 1

FPGA

GTI1

FPGA

GTI2

GTI1 GTI2

Rgion2

Mmoire

256kx32

Mmoire256kx32

BC

IN OUT

E D i h 1 / C f D i h 2

-

8/7/2019 cours_Xilinx_2006

88/113

Exec. Deriche 1 / Conf. Deriche 2

FPGA

GTI1

FPGA

GTI2

GTI1 GTI2

Deriche 1

Mmoire

256kx32

Mmoire256kx32

BC

IN OUT

ARDOISE : Estimation de performancesARDOISE : Estimation de performances

-

8/7/2019 cours_Xilinx_2006

89/113

ARDOISE : Estimation de performancesARDOISE : Estimation de performances

Application de segmentation dimagesApplication de segmentation dimages

-

8/7/2019 cours_Xilinx_2006

90/113

Application de segmentation d imagesApplication de segmentation d images

-

8/7/2019 cours_Xilinx_2006

91/113

7.1 Architecture des Virtex2-Pro7.1 Architecture des Virtex2-Pro

-

8/7/2019 cours_Xilinx_2006

92/113

7.1 Architecture des Virtex2 Pro7.1 Architecture des Virtex2 Pro

Transceivers

RocketIO 622 Mbps

Transceivers

RocketIO 622 Mbps

Transceivers

RocketIO 622 Mbps

Transceivers

RocketIO 622 Mbps

Architecture FPGAVitexII

Processeur PowerPC

32 bits 400MHz

-

8/7/2019 cours_Xilinx_2006

93/113

7.1 Architecture des Virtex2-Pro7.1 Architecture des Virtex2-Pro

-

8/7/2019 cours_Xilinx_2006

94/113

7.1 Architecture des Virtex2 Pro7.1 Architecture des Virtex2 Pro

PPC405

7.1 Architecture des Virtex2-Pro7.1 Architecture des Virtex2-Pro

-

8/7/2019 cours_Xilinx_2006

95/113

7.1 Architecture des Virtex2 Pro7.1 Architecture des Virtex2 Pro

PPC405

EthernetI/O

Mmoire

Internal Configuration

Acces Port

Auto-reconfiguration complte de la plate-forme !

7.2 Architecture des Virtex4-multiPlatform7.2 Architecture des Virtex4-multiPlatform

-

8/7/2019 cours_Xilinx_2006

96/113

7.2 Architecture des Virtex4 multiPlatform

Une famille de composants plate-forme

diffrencis en fonction des besoins : LX : logique haute performances

FX : TS trs hautes performances

SX : traitement embarqu et connectivit

rapide

Virtex-4 LX FPGA Devices

Virtex-4 SX FPGA Devices

Virtex-4 FX FPGA Devices

-

8/7/2019 cours_Xilinx_2006

97/113

-

8/7/2019 cours_Xilinx_2006

98/113

-

8/7/2019 cours_Xilinx_2006

99/113

7.3 Architecture Excalibur-ARM7.3 Architecture Excalibur-ARM

-

8/7/2019 cours_Xilinx_2006

100/113

-

8/7/2019 cours_Xilinx_2006

101/113

7.4 Architecture XPP7.4 Architecture XPPTMTM de PACTde PACT

-

8/7/2019 cours_Xilinx_2006

102/113

Du SOPC au RSoC :Reconfigurable System on Chip

-

8/7/2019 cours_Xilinx_2006

103/113

Architecture interne organise autour dun rseau de communication :

Processeur central intgr (ARM 32 bits)

Mmoire intgre

Ressources dentre/sortie

Priphriques Zone reconfigurable dynamiquement (64 ALUs reconfigurables)

Applications de type multimdia

8 CONCLUSION8 CONCLUSION

-

8/7/2019 cours_Xilinx_2006

104/113

Lvolution des performances de la technologie reconfigurable rend

les RSoC conomiquement faisables et meilleurs candidats pour les

machines de typeplateformes.

La technologie est mre, matrise et les concepts de configuration

statique largement accepts.

Les SOPC et RSoC deviennent de plus en plus intgrs, parallles et

htrognes. Leurs applications se dplacent progressivement vers le

temps rel mou et dur .

Besoin de dvelopper des mthodologies dexploitation efficace deces machines :

OS embarqus temps-rel

mthodologies de conception par composants

exploitation de la reconfiguration dynamique en ligne

9 PISTES9 PISTES

-

8/7/2019 cours_Xilinx_2006

105/113

Le challenge scientifique est aujourdhui de concevoir des plate-

formes embarques totalement autonomes dotes des capacits de

reconfiguration partielle dynamique (RSoC).

Complexit architecturale + complexit des applications

+ htrognit des ressources + HW/SW

= nouvelles mthodologies de conception

-

8/7/2019 cours_Xilinx_2006

106/113

Applications : radio-logicielle, plate-formes multimdia portables,

contrle/commande embarqu

Ressources : processeurs RISC (ARM, PPC), processeurs DSP,

Contrleurs, mmoire(s), bus, rseaux, IP ddies,

ARD, I/O

Concepts : Reconfiguration dynamique (ARD), routage

dynamique (rseaux), SW+HW, RTOS,

paralllisme, squentiel, reprogrammabilit en ligne ,

qualit de service

Mthodes : Gnie logiciel, modlisation, concepts objets,

portabilit, validation haut niveau

Modle logiciel des plate-formesModle logiciel des plate-formes

-

8/7/2019 cours_Xilinx_2006

107/113

ARD1 ARD2DSPProc.

Reconf. HAL Reconf. HAL

MV MM MM MV MV MM

noyau noyau noyau noyau noyau noyau

Communications flexibles Communications flexibles

noyau noyau

Interconnexions (rseau, bus...)

OS pour SOC+ARD

reconfigurablenon-reconfigurable

Application

OS pour ARD

-

8/7/2019 cours_Xilinx_2006

108/113

p

PROCESSEUR CENTRAL

MACHINE VIRTUELLEMODULE MATERIEL

main

entrepot

de config.

OS_createMV()

OS_createMM()

Zone reconfigurable

Gestion

des

communications

rseau de communication

flexible

-

8/7/2019 cours_Xilinx_2006

109/113

OS pour ARD changement de contexte

-

8/7/2019 cours_Xilinx_2006

110/113

PROCESSEUR CENTRAL

changements

de contexte

Migration

soft / soft

Migration

hard / soft

Premption

matrielle

MODULE MATERIEL MACHINE VIRTUELLE

Zone reconfigurable

Ordonnancement

Modlisation UML des plate-formesModlisation UML des plate-formes

-

8/7/2019 cours_Xilinx_2006

111/113

Flot de modlisation, dabstraction et de raffinementFlot de modlisation, dabstraction et de raffinement

-

8/7/2019 cours_Xilinx_2006

112/113

http://oversoc.ensea.frhttp://oversoc.ensea.frProjet ANR 2005-2008Projet ANR 2005-2008

-

8/7/2019 cours_Xilinx_2006

113/113