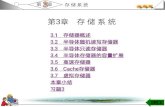

本章目录 4.1 主存储器处于全机中心地位 4.2 主存储器分类 4.3 主存储器的主要技术指标 4.4 主存储器的基本操作 4.5 读/写存储器 ( 即随机存储器

模块 1 数据与存储器的操作训练

-

Upload

josephine-fischer -

Category

Documents

-

view

106 -

download

2

description

Transcript of 模块 1 数据与存储器的操作训练

-

1 1 1 MSC-512 MSC-511 ROM2 RAM2

-

1 2 /3

-

151 AT89C51/52 AT89S51/52 5151AT89C51323334

-

2ATMELAVR AVRATTINY12/13/15AT90S2313ATMEGA8/16/64 AVR ATTINY2313ATMEGA168/169ATMEGA1280/2560

-

3MicroChip

-

4Motorola68

-

1

-

2

-

3

-

4

-

5

-

1D10D2B10010101B01223H1AH019AB CDEF1616

-

122217373 = 01001001B2101101B

-

31638686 = 56H41649AH

-

584215110010108 4 2 18 4 2 11 1 0 0 1 0 1 0 B11001010B=0CAH

-

50D9HD=13=81+41+20+11=1101B9=81+40+20+11=1001B0D9H=11011001B6

-

01101001B1AH0B2C5H 108 16

-

CPU8

RAM256RAM128128

ROM4KBROM

/16/

I/O48I/OP0P1P2P352/2 16MHZ12MHZ

-

51CPU8RAM256RAM128128ROM4KBROM/16/I/O48I/OP0P1P2P352/2 16MHZ12MHZ

-

P3VCCVSSXTAL2 XTAL1RSTP0. 0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7P1. 0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2. 0ALEP3. 0 P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.72XTAL1XTAL23RST4P0P1P2P37ALE1VCC(+5V)VSS()MCS-51

-

/P0. 0 P0.1 P0.2 P0.3 P0.4 P0.5 P0.6 P0.7P1. 0 P1.1 P1.2 P1.3 P1.4 P1.5 P1.6 P1.7P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2. 0P3. 0 P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.748I/OP0P1P2P3I/O(1) P0 8 P28P1I/O P3

-

(2)ALE1MOV P1,#00H2MOV P1,#0FFH3MOV P1,#0AAH4CLR P1.05SETB P1.00+5V

-

(3)ALE MOV P3, #11111111BMOV A, P3 89C51AI/O1FET P3.4A01

-

2

-

21Vcc40+5VVss20 2

-

23(1819)CPU

-

24 RST10msRST ?

-

CPU2ToscXTAL1Tcy12Tcy=12Tosc

-

CPU2Torder Torder= TcyTorder= 2Tcy Torder= 4Tcy

-

CPU212MHz Tcy=12Tosc=1usTorder=2Tcy=2us

-

20000HSP=07H P0-P3RAM

ACC00HTMOD00HB00HTCON00HPC0000HTL000HPSW00HTH000HSP07HTL100HDPTR0000HTH100HP0-P30FFHSBUFIPXX000000BSCON00HIE0X000000BPCON0XXX0000B

-

80318751805189C51

256B4K64K64K

-

1ROM(PC)

-

2RAMRAM RS0RS1

-

12821SFR 11SFR

-

1ACCA MOV A, #2 ADD A, #52B MUL AB DIV AB

-

3PSW CY(PSW.7) CY1CY 0CYC AC(PSW.6) 44AC1AC 0

-

OV(PSW.2) OV10 PSW.1PPSW.0ALU 1A1 P1P0FO(PSW.5) 3PSW

-

RS1(PSW.4)RS0(PSW.3) RS1RS0 2-13PSW

-

4DPTRDPH8DPL816

-

[] [] []NEXT: MOV A , R0 ;A(R0)1~34

-

ORG 0000H LJMP START ORG 0030HSTART: LCALL DELAY NOP LJMP STARTDELAY: NOP RET END1ORGORG 2ENDEND 3JMPLJMP AJMP SJMP

-

ORG 0000H LJMP START ORG 0030HSTART: LCALL DELAY NOP LJMP STARTDELAY: NOP RET END4CALLLCALL ACALL LCALL DELAY LCALL DELAYDELAYDELAYRET5RET

-

1 MOV A, 0E8H#

-

2 MOV A50H50H MOV21H,30H30H21H

-

3 8R0R7ABDPTRC MOV P1R4 CLR A A MOV AB

-

4@MOV A, @R05 ;MOVC A, @DPTR+A@RnR0R1

-

6 7 CLR P1.0 P10 PCLJMP START DJNZ R7,DEL

-

1MOV MOV A,#2 MOV 10H,A MOV R0,#50H MOV A,R0 MOV R1,#10H MOV A,@R1;(A)=2;(10H)=2;(R0)=50H;(A)=50H;(R1)=10H;(A)=2

-

2CLR ACC80CLR bit CLR A

-

3SETB1SETB C SETB P3.0 SETB RS1

-

1AT89C51 4 251EA31 3RST 4 5PC SP P0~P3

10ms 0000H 07H FFH

-

612MHZ 7 8 1/12us 1us 4us ROM RAM 0000H~0FFFH 00H~0FFH

-

ORG 0000H LJMP MAIN ORG 0030HMIAN: CLR P1.0 LCALL DELAY SETB P1.0 LCALL DELAY LJMP STARTDELAY: MOV R7,#0FFH DL0: MOV R6,#100 DJNZ R6,$ DJNZ R7,DL0 RET END1

-

280C51 MOV A, 4AH A B C D380C51 MOV A, @R0 A B C D4@Rii A1 B01 C2 D12

-

5RAM60H=50H50H=20HP1P1=5BH MOV R0 , #60H MOV A , @R0 MOV R1 , A MOV B , @R1 MOV R2 , P1 R0= (A)= (R1)= (B)= (R2)=

-

6R1=40H, (A)=30H, (40H)=60H, (50H)=08H, MOV A , @R1 MOV 50H , A MOV R1 ,#7FHA= (50H)= (R1)=

-

7SETB C C= CLR C C=

8A= MOV A,#8BH LJMP NEXT CLR ANEXT: MOV A,#02H END