The MOS Transistor - NTUA

Transcript of The MOS Transistor - NTUA

Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών

Ηλεκτρονική ΙΙΙωάννης Παπανάνος

Άδεια ΧρήσηςΤο παρόν εκπαιδευτικό υλικό υπόκειται σεάδειες χρήσης Creative Commons. Για εκπαιδευτικόυλικό, όπως εικόνες, που υπόκειται σε άδεια χρήσηςάλλου τύπου, αυτή πρέπει να αναφέρεται ρητώς.

2 2 National Technical University of Athens

Microelectronic Circuit Design Group

From Bipolar to CMOS

Yannis Papananos

Analog & RF IC Lecture Notes

Ref. Toshiba [from W. Sansen: ‘Analog Design Essentials’]

3 3 National Technical University of Athens

Microelectronic Circuit Design Group

Technology Roadmap

Yannis Papananos

Analog & RF IC Lecture Notes

4 4 National Technical University of Athens

Microelectronic Circuit Design Group

Technology Roadmap – cont’d

Yannis Papananos

Analog & RF IC Lecture Notes

5 5 National Technical University of Athens

Microelectronic Circuit Design Group

Technology Trends

SiGe BiCMOS

Technology nodes include 0.18μm, 0.13μm and, recently 90 nm.

The latter can provide bipolar transistors with a unity gain frequency

beyond 200GHz.

CMOS

Technology nodes include 0.18μm down to 22nm or even smaller.

• Applications from cellular telephony transceivers (1-2 GHz) to WLAN

applications (5GHz) to UWB (10GHz) and radar applications (40GHz – 60GHz)

• RF front-end designs as high as 100GHz have been recently reported using a

65nm digital CMOS process (ISSCC 2008)

Yannis Papananos

Analog & RF IC Lecture Notes

6 6 National Technical University of Athens

Microelectronic Circuit Design Group

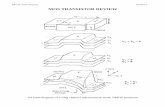

The MOS Transistor

G B

S

G B

S

D D

• Substrate doping ≈ 1016 atoms/cm3

• Gate material : low – resistivity polysilicon

• Gate SiO2 thickness : 100 Ǻ to only a few

atoms in modern nm processes (SiO2 to be

replaced by high-k dielectric materials in deep

nm processes)

• Conditions for proper operation of the nMOS

device :

VSB ≥ 0

VDB ≥ 0

The BS and BD diodes are always reverse –

biased.

• The MOS transistor is a bilateral device but

we always consider the condition :

VDS ≥ 0

dov dov

n+ n+

p-sub

GD

B Body

Source

S

SiO2Gate

Drain

W

L

Yannis Papananos

Analog & RF IC Lecture Notes

nMOS device

symbol

7 7 National Technical University of Athens

Microelectronic Circuit Design Group

Operation of the MOS Transistor

n+

p-sub

G D

B

S+-

VGS

VSB

n+

+-

n+

p-sub

G D

B

S+-

VGS

VSB

n+

+-

VDS = 0

VSB > 0

VDB > 0

(i) VGS < 0 : holes are accumulated at the surface.

As VGS increases, the holes concentration is

reduced.

(ii) VGS = VFB (FB – flat-band voltage) : The surface

becomes electrically neutral (fig. (a))

(iii) VGS > VFB : As VGS increases, the depletion

region under the gate is as deep as is around

the S and D regions (fig. (b)). Electrons are now

free to move in the channel : the surface is

inversed.

(iv) Depending on the VGS value, three inversion

regions are defined :

• Weak

• Moderate

• Strong

Yannis Papananos

Analog & RF IC Lecture Notes

( a )

( b )

8 8 National Technical University of Athens

Microelectronic Circuit Design Group

Operation of the MOS Transistor - cont’d

n+

p-sub

G D

B

S

+-

VGS

VSB

n+

+-

VDS

-+

The Body effect

• The body effect is caused by VSB : an increase in the VSB value increases the

depletion regions under the S and D regions. Therefore, a higher VGS value is

now demanded in order for the inversion layer to become equally thick compared

to the S and D regions.

The Drain Current

• A drain to source voltage is now applied (VDS > 0)

Thus : VDB = VDS + VSB : the depletion region

under the D region becomes deeper.

• A free electron approaching the D region is now

swiftly pulled towards the drain. This phenomenon

defines the drain current (ID) with a conventional

direction from the drain to the source.

Yannis Papananos

Analog & RF IC Lecture Notes

9 9 National Technical University of Athens

Microelectronic Circuit Design Group

The MOS Transistor : I – V Characteristics

Non

satu

ratio

nID

VDS

VGS =VGS4

VSB = const. ≥0

VGS =VGS3

weak and moderate inversion

Sat

urat

ion

VGS =VGS2

VGS =VGS1

0

+-

VDS+

-

ID

VGSVSB

+

-

VGS

0

DI

DI ~ (VGS-VT)

straight

line

exponential

VT

Mo

de

rate

inve

rsio

n

We

ak

inve

rsio

n

Strong

inversion

Yannis Papananos

Analog & RF IC Lecture Notes

( a )

( b )

( c )

10 10 National Technical University of Athens

Microelectronic Circuit Design Group

The MOS Transistor : Operation in Strong Inversion

We mostly focus in strong inversion operation (VGS is larger than VT by

100 – 200 mV min.) In strong inversion, the following equations apply :

ID

VDS

0VDS‘

Nonsaturation Saturation

+-

VDS+

-

ID

VGSVSB

+

-

1

Kk

C2

1,

1

VVV o x

TGSDS

. )sat(VV,)VV(L

Wk

. )satn o n(VV,V)1(V)VV(2L

WK

I

DSDS

2

TGS

DSDS

2

DSDSTGS

D

μ = carrier mobility

C’ox = oxide capacitance per unit area

δ = between 0 and 1

Yannis Papananos

Analog & RF IC Lecture Notes

11 11 National Technical University of Athens

Microelectronic Circuit Design Group

Operation of the MOS Transistor: Body Effect

0VTTO SBVV

ox

SA

C

qN2

q = electron charge

NA = body’s doping concentration

εS = Si permittivity

φΒ = 0.6V ÷ 0.7V

Threshold voltage

for VSB = 0

ID

VDS

VGS =VGS3

VGS2

VGS1

0

ID

VDS

VGS =VGS3

for VSB=VSB1>0

VGS2

VGS1

0

VT

VSB0

VTO

slope =

SBSB

T

V2V

Vb

Yannis Papananos

Analog & RF IC Lecture Notes

)V(VV SBTOT

TSB VV

(Body effect)

12 12 National Technical University of Athens

Microelectronic Circuit Design Group

Operation of the MOS Transistor: Saturation Region

ID dependence on VDS in saturation region

(channel length modulation)

DSDS

A

DSDS2

TGSD VV,V

VV1)VV(

L

WkI

• VA is a process – dependent parameter, equivalent

to the Early voltage of bipolar transistors

• VA ~ L

ID

V’DS VDS0VA

Yannis Papananos

Analog & RF IC Lecture Notes

13 13 National Technical University of Athens

Microelectronic Circuit Design Group

MOS Transistor Modeling

Small - signal equivalent circuit : low – frequencies model

BSDS V,VGS

Dm

V

Ig

DSGS V,VBS

Dmb

V

Ig

BSGS V,VD S

Dd

V

Ig

transconductance body transconductance output conductance

+-

ID+ΔID

VGS+ΔVGS

ID+ΔID

VBS+ΔVBS

+-

ID+ΔID

VDS+ΔVDS

+-

gmΔVGS gmbΔVBS

d

s

g b

Yannis Papananos

Analog & RF IC Lecture Notes

14 14 National Technical University of Athens

Microelectronic Circuit Design Group

Small – signal equivalent circuit : low frequencies

Small – signal parameters in strong inversion

.sat,VL

WK2

.satno n,VL

WK2

g

DS

DS

m

SB

mm bV2

b.satnonand.sat,bgg ,

.satV

Ι

.satnonV)1(VVL

WK2

g

A

D

DSTGS

d

,

,

DSdBSm bGSmD VgVgVg Applying superposition :

Yannis Papananos

Analog & RF IC Lecture Notes

15 15 National Technical University of Athens

Microelectronic Circuit Design Group

The MOS Transistor

Velocity Saturation

• Further increase in VGS leads to high electric fields in the channel :

electrons move at maximum speed υsat (≈ 107 cm/s)

• The transconductance reaches a maximum value at velocity saturation :

strong

inversionvelocity

saturationweak

inversion

VGS

ID

(independent of L)

strong

inversion

velocity

saturation

weak

inversion

VGS

gm

gmVS= W Cox

'υsat

Fig. a

Fig. b

Yannis Papananos

Analog & RF IC Lecture Notes

16 16 National Technical University of Athens

Microelectronic Circuit Design Group

The MOS Transistor

Overdrive voltage

• The value (VGS – VT) is often called overdrive voltage (Vod).

• Typical values for Vod for operation in strong inversion are around 0.2V (low

end) and 0.5V (high end).

• The max. Vod value for the transition between strong inversion and velocity

saturation is proportional to the channel length L.

LVVV TGSod 5)( maxmax,

Yannis Papananos

Analog & RF IC Lecture Notes

17 17 National Technical University of Athens

Microelectronic Circuit Design Group

The MOS Transistor

Geometry (μm) VDD (V) VT (V) Vod,max (V)

0.5 3.6 0.6 2.5

0.18 2 0.4 0.9

0.13 1.6 0.3 0.65

0.09 1 0.27 0.45

0.065 1 0.24 0.32

nm CMOS : The challenge

• As geometry shrinks, Vod,min and Vod,max approach each other : no margin

left between strong inversion and velocity saturation.

• As geometry shrinks, the design of analog and RF ICs becomes more

challenging in terms of biasing.

Yannis Papananos

Analog & RF IC Lecture Notes

18 18 National Technical University of Athens

Microelectronic Circuit Design Group

Small – signal equivalent circuit : moderate frequencies

The MOS device capacitances formed

are shown in the figure. The following

types of capacitances are formed :

(A) Overlap capacitances

(B) Junction capacitances

SB

02j

2S

SB

01j

1SbdebseV

1

CA

V1

CACC

AS1 = junction’s bottom area

AS2 = junction’s sidewall area

C’j0i = unit area junction capacitance for VSB = 0

Φo = junction potential

Depletion

region

dov dov

Cgde

Cbsi Cbdi

Cbde

CgdiCgsi

Cbse

Cgse

“Intrinsic”

transistor

Yannis Papananos

Analog & RF IC Lecture Notes

19 19 National Technical University of Athens

Microelectronic Circuit Design Group

Small – signal equivalent circuit : moderate frequencies – cont’d

VDS

2/3 Cox

1/2 CoxCgsi

V’DS

Cox = C’ox(WL)

Cbsi ≈ bCgsi

Cbdi ≈ bCgdi

0

Cgdi

gmΔVGS gmbΔVBS

d

s

g b

Cgd

Cgs

Cbd

Cbs

Cbb’

Cox = C’ox(WL)

Cbsi ≈ bCgsi

Cbdi ≈ bCgdi

(C) Intrinsic capacitances

where

Based on the above definitions, the

small – signal equivalent circuit of

Fig. (b) for moderate frequencies is

formed.

where Cxy = Cxyi + Cxye

Cbb’ is the body-substrate

capacitance and applies only

to triple-well devices. (b) : Small – signal equivalent circuit

for moderate frequencies

Yannis Papananos

Analog & RF IC Lecture Notes

( a )

20 20 National Technical University of Athens

Microelectronic Circuit Design Group

• The internal cutoff frequency fTi

- The gate current at dc or low frequencies is practically zero.

- At high frequencies, a capacitive gate current appears

- Considering the intrinsic part of the transistor, the small – signal

equivalent circuit is derived.

ugs

+- Cgsi Cgbi

gmugs

d

s, b

Cgdi = 0 in saturation

- The internal (or intrinsic) cutoff frequency is defined as the value

of f at which the amplitudes of drain and gate currents become

equal.

The MOS Transistor at High Frequencies

Yannis Papananos

Analog & RF IC Lecture Notes

21 21 National Technical University of Athens

Microelectronic Circuit Design Group

MOS Transistor SPICE Models

• Most popular MOS transistor SPICE models

- BSIM3v3

- BSIM4

- PSP

- EKV

• For RF devices, a complete subcircuit is built around the intrinsic transistor

model.

• SPICE – like MOS transistor models usually exhibit non physical behavior due

to poor implementation.

• Benchmark tests have been developed to reveal modeling problems.

Yannis Papananos

Analog & RF IC Lecture Notes

22 22 National Technical University of Athens

Microelectronic Circuit Design Group

Other MOS Devices

The pMOS transistor The triple-well nMOS transistor

dov dov

p+ p+

n-sub

GD

B Body

Source

S

SiO2Gate

Drain

W

L

dov dov

n+ n+

deep n-well

GD

B Body

Source

S

SiO2Gate

Drain

W

L

p-sub

p-well

Yannis Papananos

Analog & RF IC Lecture Notes

23 23 National Technical University of Athens

Microelectronic Circuit Design Group

The MOS Transistor in Weak and Moderate Inversion

• In weak inversion, the transistor exhibits

an exponential ID – VGS characteristic.

• In moderate inversion, no simple expression

for the I-V characteristic can be denoted.

• The limits of the three regions of inversion (VK, VM, VH) are process-dependent,

closed formulae exist but are not handy.

• The lower limit (VK, IK) is the threshold where leakage currents are comparable to

the drain current.

Yannis Papananos

Analog & RF IC Lecture Notes

National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

Το Τρανζίστορ ως Δίοδος

• Το MOS τρανζίστορ γίνεται στοιχείο δύο ακροδεκτών.

• άρα

το τρανζίστορ είναι ΠΑΝΤΑ στον κορεσμό.

δίοδος με τετραγωνική

I – V χαρακτηριστική

Κυκλώματα Πόλωσης

+

-

I

V

I

VVT

TGSDSDSGS VVVVV

2

T )VV(L

WkI

(α)

(β)

24

National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

Μετατοπιστές – Διαιρέτες Τάσης

25

+

+

-V

I I II

-V

+

-V

+

-

V

I

V

W/L=10

W/L=1

W/L=0.1

Μετατοπιστές τάσης (level shifters)

Διαιρέτες τάσης (voltage dividers)

+VDD

-VSS

Vx

+VDD

-VSS

Vx

+VDD

-VSS

Vx

+

-

R I

Vx

I

0

A

B

R

VVVI

VVL

WkI

xSSDD

2

Tx

Αν αυξηθεί το VDD + VSS, η γραμμή φόρτου γίνεται έτσι.

Το σημείο λειτουργίας από Α γίνεται Β → Τα Vx δεν αλλάζει πολύ

Με αντιστάσεις : Με τρανζίστορ : Μικτοί :

26 National Technical University of Athens

Microelectronic Circuit Design Group

Βασικά Δομικά Στοιχεία Ενισχυτών – Αναστροφέας με Αντίσταση

Yannis Papananos

Analog & RF IC Lecture Notes

.

ID

+VDD

-VSS

VOUTM1

+

-

R

VIN

+

-

ολικήτάση εισόδου

Στον κορεσμό :

ID

VOUT

0

VDD + VSS

L

V

VΙΝ

LVDD + VSS

M1

OFF

M1

( κορεσμός)

M1

( μη κορεσμός)

M’

M′

2

TOIN

1

SSDDOUT

DSSDDOUT

2

TOIN

1

D

VVL

WkRVVV

RIVVV

VVL

WkI

OUT

27 National Technical University of Athens

Microelectronic Circuit Design Group

Αναστροφέας με Αντίσταση - συνέχεια

Yannis Papananos

Analog & RF IC Lecture Notes

.

ΙΚΑΣ (σε χαμη λές συχνότητες) :

g m u in u in r d = 1 / g d

+

-

R

+

-

u out

R // r g

u

R // r u g

u

u A d m

in

d in m

in

out o

Για μεγάλη ενίσχυση χρειάζεται μεγάλο R , άρα μεγάλο εμβαδόν στο Ο.Κ. Μια καλύτερη λύση δίνεται παρακάτω.

28 National Technical University of Athens

Microelectronic Circuit Design Group

Αναστροφέας CMOS

Yannis Papananos

Analog & RF IC Lecture Notes

.

+VDD

-VSS

VOUT

MP

+

-VIN

+

-MN

πόλωση+

-

B’

A’

IN

IN

VDSNVDD+VSS

VDSN

IP

VDSP

VOUT

VΙΝ

ΑVDD + VSS

MΝ,ΜP

OFF

MN KOΡ.

ΜP ΜΗ ΚΟΡ.

MN KOΡ.

ΜP ΚΟΡ.MN ΜΗ KOΡ.

ΜP ΚΟΡ.

B

29 National Technical University of Athens

Microelectronic Circuit Design Group

Αναστροφέας CMOS - συνέχεια

Yannis Papananos

Analog & RF IC Lecture Notes

gmΝ uinuin

gdN

+

-

gdP

+

-

uout

D

APAN

N

N

AP

D

AN

D

D

N

N

dP

Nmo

I

1

V

1

V

1

L

Wk

2

V

I

V

I

IL

Wk

2

gg

gA

Για μεγάλοΑο , υποθ. σταθερό DI και σταθερό NLW , χρειάζονται μεγάλαVAN ,

VAP, άρα μεγάλα L. Επίσης, για σταθερά W και L , D

oI

1~A .

ID

Αο

o

o1

~AI

Πραγματική

καμπύλη λόγω

μέτριας και ασθ .

αναστροφής

Για μεγάλο Αο , χρειάζεται λοιπόν μικρό DI άρα, για σταθερά W και L , χρειάζεται

μικρό TGS VV .

gmΝ uinuin

gdN

+

-

gdP

+

-

uoutgmΝ uinuin

gdN

+

-

gdP

+

-

uout

D

APAN

N

N

AP

D

AN

D

D

N

N

dPdN

mo

I

1

V

1

V

1

L

Wk

2

V

I

V

I

IL

Wk

2

gg

gA

D

APAN

N

N

AP

D

AN

D

D

N

N

dPdN

mo

I

V

1

V

L

Wk

2

V

I

V

I

IL

Wk

2

gg

gA

Για μεγάλοΑο , υποθ. σταθερό DIDI και σταθερό NLW NLW , χρειάζονται μεγάλαVAN ,

VAP, άρα μεγάλα L. Επίσης, για σταθερά W και L , D

oI

1~A

D

oI

1~A .

ID

Αο

o

o1

~AI

Πραγματική

καμπύλη λόγω

μέτριας και ασθ .

αναστροφής

ID

Αο

o

o1

~AIo

o1

~AI

Πραγματική

καμπύλη λόγω

μέτριας και ασθ .

αναστροφής

Για μεγάλο Αο , χρειάζεται λοιπόν μικρό DIDI άρα, για σταθερά W και L , χρειάζεται

μικρό TGS VV TGS VV .

30 National Technical University of Athens

Microelectronic Circuit Design Group

Αναστροφέας Cascode

Yannis Papananos

Analog & RF IC Lecture Notes

.

Για περισσότερη ενίσχυση, η αγωγιμότητα φορτίου πρέπει να είναι μικρότερη

από dPdN gg . Χρησιμοποιούμε ένα στάδιο cascode :

+VDD

-VSS

VOUT

gy

gx

M4

M3

M2

M1

BIAS4

BIAS3

BIAS2

VIN

2d

2m

1d

x

g

g

gg και

3d

3m

4d

y

g

g

gg

yx

1mo

gg

gA

Με κοινό σώμα για τα Μ3, Μ4 μπορούμε να χρησιμοποιήσουμε κοινό πηγάδι.

31 National Technical University of Athens

Microelectronic Circuit Design Group

Ακόλουθος Πηγής (Source Follower)

Yannis Papananos

Analog & RF IC Lecture Notes

.

+VDD

-VSS

VIN

VOUT

VIN

VOUT VGS=σταθ.

Αο=1 για ιδανική

πηγή ρεύματος

και VA=∞Κλίση

= 1

+VDD

-VSS

VIN

VOUT

VIN

VOUT

Αο<1 λόγω του

«φαινομ. σώματος»

VGS όχι σταθ.

32 National Technical University of Athens

Microelectronic Circuit Design Group

Ακόλουθος Πηγής (Source Follower) - συνέχεια

Yannis Papananos

Analog & RF IC Lecture Notes

.

+VDD

-VSS

VIN

VOUT

R

R1gg

gA

dm

mo

Υπολογισμός κέρδους με ΙΚΑΣ

R=εσωτ. αντίσταση πηγής ρεύματος

Αγνοούμε φαιν. Early και φαιν. σώματος

33 National Technical University of Athens

Microelectronic Circuit Design Group

Το Διαφορικό Ζεύγος

Yannis Papananos

Analog & RF IC Lecture Notes

.

Differential Mode (DM)

Common Mode (CM)

+-

+-

+VDD

-VSS

ΦΟΡΤΙΟ ΦΟΡΤΙΟ

Μ1 Μ2

Ι1 Ι2

VI1 VI2

VO1 VO2

ΙSS

Μη

ιδανική

x y

2I1IID VVV

2

VVV 2I1I

IC

+-

+-

+-

x y

VIC

VIB/2 VID/2

2OI1OOD VVV

2

VVV 2O1O

OC

34 National Technical University of Athens

Microelectronic Circuit Design Group

Το Διαφορικό Ζεύγος - συνέχεια

Yannis Papananos

Analog & RF IC Lecture Notes

Κέρδος διαφ. σήματος id

od

dmV

VA

Κέρδος κοινού σήματος ic

oc

cmV

VA

Λόγος απόρριψης κοινού σήματος cm

dm

A

A)CMRR(

Για την εύρεση του dmA :

+-

+-

go

V ≈ 0

gL gL

-Vod/2Vod/2

-Vid/2Vid/2

L

mdm

L

idm

od

idm

g

gA

g

Vg

V

Vgi

1

22

2

35 National Technical University of Athens

Microelectronic Circuit Design Group

Το Διαφορικό Ζεύγος - συνέχεια

Yannis Papananos

Analog & RF IC Lecture Notes

Για την εύρεση του cmA :

+- go

x

gL gL

VocVoc

VicIss

Υποθ. mo gg

Δείτε το σαν ακολουθητή πηγής. icx VV

L

ocm

o

ico

L

ssoc

icoxoss

g

gA

g

Vg

g

iV

VgVgi

2

2

1

2

36 National Technical University of Athens

Microelectronic Circuit Design Group

Το Διαφορικό Ζεύγος – Ανάλυση Μεγάλου Σήματος

Yannis Papananos

Analog & RF IC Lecture Notes

Από KVL :

άρα

οπότε

αντικαθιστώντας :

0VVVV 2i2gs1gs1i

)L/W(k

I2VV d

Tgs

L

W

2

k

IIVVV

2d1d

2i1iid

TAIL2d1d III

2

i dTAIL

i dTAIL

1d V)L/W(k

I4V

L

W

4

k

2

II

0Vov

0V

1di d

i d

i d

V2)L/W(k

I22V

National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

• Οι καθρέφτες ρεύματος χρησιμοποιούνται για τη

δημιουργία πόλωσης από ένα ρεύμα αναφοράς.

• Το κέρδος ρεύματος του καθρέφτη καθορίζεται

από τις γεωμετρικές διαστάσεις των τρανζίστορ.

• Ιδανικά το κέρδος ρεύματος είναι ανεξάρτητο από

τη συχνότητα.

• Ιδανικά το ρεύμα εξόδου είναι ανεξάρτητο της

τάσης εξόδου (ιδανική πηγή ρεύματος).

• ΜΗ ΙΔΑΝΙΚΟΤΗΤΕΣ

- Εξάρτηση του κέρδους ρεύματος από τη

συχνότητα.

- Εξάρτηση του ρεύματος εξόδου από την

τάση (πεπερασμένη αντίσταση εξόδου).

- Σφάλμα κέρδους (συστηματικό/τυχαίο)

Καθρέφτες Ρεύματος

VDD

Vin Vout

Rout

Iout

Iref

Είσοδος Έξοδος

Είσοδος Έξοδος

VDD

VinVout

Rout

Iout

Iref

(α)

(β)

37

National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

•

•

υποθέτοντας (αγνοούμε φαινόμενο Early)

• Έτσι :

Απλός Καθρέφτης MOS

• Ένταξη φαινομένου Early στον καθρέφτη ρεύματος

1

1DT1GS

2

2DT2GS

LWk

I2VV

LWk

I2VV

0gd

1D

1

22D I

LW

LWI

ύόLW

LW

1

2

1GS2GS VV

A

1DS2DS1D

1

22D

V

VV1I

LW

LWI

(α)

(β)

VDD

Vin

Vout

Iref

Μ1 Μ2

-VSS

1D

1

2 ILW

LW ID2

0 VD’S VDS1

VDS2 = Vout

VGS2 = VGS1

38

National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

Απλός Καθρέφτης MOS - συνέχεια

• Το συστηματικό σφάλμα ορίζεται ως

• Άρα η αλλαγή στο ρεύμα πόλωσης (ID2) θα επηρρεάσει τη VDS2 και κατά συνέπεια

θα μεταβάλλει το συστηματικό σφάλμα Ε.

• Η επίδραση της τάσης εισόδου στο ρεύμα πόλωσης :

• Τυχαίο σφάλμα :

Οφείλεται σε μη ταίριασμα μεταξύ των τρανζίστορ Μ1 και Μ2 κατά τη διαδικασία

κατασκευής του ολοκληρωμένου κυκλώματος

)v o ltag eo v erd riv e(VVVV odT1GSi n

Dod I~V

A

1DS2DS

V

VVE

39

National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

Κασκοδικός Καθρέφτης MOS

• Συνδεσμολογία cascode :

Υπολογισμοί αντίστασης εξόδου

ΙΚΑΣ

• Η αγωγιμότητα εξόδου της συνδεσμολογίας cascode (gout) είναι πολύ μικρότερη

αυτής του απλού τρανζίστορ (gd).

x

xout

i

ur

22

11

dm

dout

out gg

gg

r+

-

gd2

gd1

ux

ix

i1-gm2uy

uy(α)

(β)

+- Vx

ix

Μ1

Μ2

-VSS

40

National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

Κασκοδικός Καθρέφτης MOS - συνέχεια

• Με βάση την προηγούμενη ανάλυση :

[έχει ληφθεί υπόψη και το φαινόμενο σώματος]

• Ο κασκοδικός καθρέφτης βοηθά να φτιαχτεί

πηγή ρεύματος πιο κοντά στην ιδανική.

• Ακόμη μεγαλύτερη βελτίωση μπορεί να επιτευχθεί

εάν χρησιμοποιηθεί διπλός κασκοδικός

καθρέφτης.

• Μειονέκτημα είναι η δυσκολία πόλωσης των

κυκλωμάτων όπου χρησιμοποιούνται κασκοδικοί

καθρέφτες ρεύματος – ιδιαίτερα σε χαμηλές τάσεις

τροφοδοσίας.

1d1d2mb2m2dout rrgg1rR

Μ1

Μ2

Μ3

Μ4

Iout

Vin Vout

VDD

Iref

Rout

-VSS

(α)

(β)

41

National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

Καθρέφτης Ρεύματος Wilson

• Μηχανισμός αρνητικής ανάδρασης επιτυγχάνει τη

σταθερότητα του ρεύματος εξόδου :

- Υποθέτουμε ότι το Iout αυξάνεται.

- VGM1 αυξάνεται.

- VGM3 αυξάνεται.

- Αναγκαστικά VDM3 μειώνεται διότι Iref σταθερό

- Άρα VGM2 μειώνεται και Iout μειώνεται.

• Στο διπλανό σχήμα φαίνεται μια βελτιωμένη

έκδοση του καθρέφτη ρεύματος Wilson.

Μ1

Μ2

Μ3

Iout

Vin

Vout

VDD

Iref

-VSS

(α)

(β)

42

National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

Καθρέφτης Ρεύματος Wilson - συνέχεια

• To συστηματικό σφάλμα κέρδους του απλού καθρέφτη Wilson δίνεται από τη

σχέση :

• Το τρανζίστορ M4 του βελτιωμένου καθρέφτη Wilson έρχεται να εξισώσει τις

τάσεις VDS και έτσι να ελαχιστοποιήσει το συστηματικό σφάλμα.

A

2GS

A

3DS1DS

V

V

V

VVE

43

National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

Πηγή Ρεύματος Widlar

• Εάν χρειάζονται μικρά ρεύματα πόλωσης σε ένα κύκλωμα, τότε οι

προαναφερθείσες συνδεσμολογίες καθρεφτών δεν ενδείκνυνται εάν θέλουμε

χαμηλή κατανάλωση και περιορισμό του εμβαδού στην επιφάνεια του πυριτίου.

• Στην περίπτωση αυτή χρησιμοποιείται η πηγή ρεύματος Widlar του σχήματος.

- Επειδή το Iout εξαρτάται πολύ λιγότερο από το

ρεύμα εισόδου και την τάση τροφοδοσίας γι’ αυτό

το κύκλωμα ονομάζεται πηγή ρεύματος και όχι

καθρέφτης ρεύματος.

- Η ύπαρξη της αντίστασης R2 δημιουργεί

διαφορετική VGS στο M2 από το Μ1 (κάτι που δεν

ισχύει στους απλούς καθρέφτες). Έτσι το Iout

μπορεί να είναι σημαντικά μικρότερο.

2

1od2

22

outR2

VR4LWk

2

LWk

2

I

Μ2Μ1

Iout

VDD

-VSS

R1

Iin

R2

44

45 National Technical University of Athens

Microelectronic Circuit Design Group

Απόκριση Συχνότητας - Αναστροφέας

Yannis Papananos

Analog & RF IC Lecture Notes

.

+VDD

-VSS

ΜP

VOUT

ΜN

ΠΟΛΩΣΗ

VΙΝ

CL

+-

VOUT

CL

gdP

gdN

CbdP

gmPVgsP

CgdN

CgsN

CgsP

CgdP

CbdN

VIN

gmNVIN

VgsP

+

-

-+

CgsN gmNVINVIN

gt VOUT

+

-Ct

CgdN

𝑔𝑡 = 𝑔𝑑𝑁 + 𝑔𝑑𝑃, 𝐶𝑡 = 𝐶𝑏𝑑𝑃 + 𝐶𝑏𝑑𝑁 + 𝐶𝑔𝑑𝑃 + 𝐶𝐿

46 National Technical University of Athens

Microelectronic Circuit Design Group

Απόκριση Συχνότητας - Αναστροφέας

Yannis Papananos

Analog & RF IC Lecture Notes

)CC(sg

1V)sCg(V

gdNtt

i ngdNmOUT

)CC(sg

sCg

V

V)s(A

g d Ntt

g d Nm

IN

OUT

t

g d Nt

mg d N

t

m

g

CCs1

)gC(s1

g

g

p

s1

z

s1

A o

t

mo

g

gA

!ίόό

gdN

m

C

gz

gdNt

t

CC

gp

Μετατροπή κατά Norton :

IAoI

IPI ω

ω

180°

90°

IA(jω)I (dB)

A(jω)

0

47 National Technical University of Athens

Microelectronic Circuit Design Group

Απόκριση Συχνότητας – Ακόλουθος Πηγής

Yannis Papananos

Analog & RF IC Lecture Notes

. +VDD

-VSS

VOUT

VΙΝ

CLRI

VOUT

CL

gdCdb

gmVgsCgd

Cgs

Cbb’R

VIN

Vgs+

-

Χωρητικότητα

σώματος -

υποστρώματος

+-

uin

Cgd

Cgs

ugs+ -

gmugsgt

Ct

uout

+

-R

1gg dt

𝐶𝑡 = 𝐶𝑏𝑑 + 𝐶𝐿 + 𝐶𝑏𝑏′

48 National Technical University of Athens

Microelectronic Circuit Design Group

Απόκριση Συχνότητας – Ακόλουθος Πηγής

Yannis Papananos

Analog & RF IC Lecture Notes

p

s1

z

s1

AV

V)s(A o

IN

OUT

tm

tg s

m

m

t

tg s

m

g s

m

tm

mo gg

CC

g

g

g1

CC

gp,

C

gz,

gg

gA

αν

|A(jω)|

(dB)

0|P| |Z|

ω (Λογ.)

1C)A1(CCC gdogsgdi n

tmmtm

x

xout gg,ggg

I

Vg αν

Στις χαμηλές συχνότητες, η χωρητικότητα εισόδου είναι :

Αγωγιμότητα εξόδου :

49 National Technical University of Athens

Microelectronic Circuit Design Group

Απόκριση Συχνότητας – Στάδιο Cascode

Yannis Papananos

Analog & RF IC Lecture Notes

ΠΟΛ.

ΠΟΛ.

ΠΟΛ.

Vout

+

--VSS

+VDD

Vin

M1

M2

x

M3

M4

wvout ggg

3d3m

4d

w

2d2m

1d

vgg

gg,

gg

gg

Ολική αγωγιμότητα στον κόμβο εξόδου :

Ολική χωρητικότητα στον κόμβο εξόδου :

L3db3gd2bd2gdt CCCCCC

φορτίουταχω ρητικότη

τυχόν

50 National Technical University of Athens

Microelectronic Circuit Design Group

Βαθμίδες Εξόδου – Ο Ακόλουθος Πηγής

Yannis Papananos

Analog & RF IC Lecture Notes

Lmbm

Lm

i

o

R)gg(1

Rg

V

V

LR

x1

1

gg

g

V

V

mbm

m

i

o

3.01.0x 9.07.0

κλίση : για

όπου άρα κλίση από

Vi

IQ

+VDD

I

-VDD

M2

M1

M3

VoRL

𝑉𝑖 = 𝑉𝑔𝑠1 + 𝑉𝑜 = 𝑉𝑜𝑣1 + 𝑉𝑇1 + 𝑉𝑜

𝑉𝑖 = 𝑉𝑜 + 𝑉𝑇𝑂 + 𝛾 2φΒ + 𝑉𝑜 + 𝑉𝐷𝐷𝑉𝑆𝐵

− 2φΒ +2 𝐼𝑄+

𝑉𝑜𝑅𝐿

𝑘′ 𝑊 𝐿 1

𝑉𝑖 𝑉𝑜=0 = 𝑉𝑇𝑂 + 𝛾 2φΒ + 𝑉𝐷𝐷 − 2φΒ +2𝐼𝑄

𝑘′ 𝑊 𝐿 1

51 National Technical University of Athens

Microelectronic Circuit Design Group

Παραμόρφωση Ακόλουθου Πηγής

Yannis Papananos

Analog & RF IC Lecture Notes

οπότε

όπου

2/5

DDoo

2/3

DDoo

2/1

DDoo

)2VV(8

3)V(f

)2VV(4

)V(f

)2VV(2

1)V(f

𝑉𝑖 = 𝑉𝐼 + 𝑣𝑖 = 𝑓(𝑛) 𝑉𝑜 = 𝑉𝑂 𝑉𝑜 − 𝑉𝑂

𝑛

𝑛!

∞

𝑛=0

𝑉𝑖 = f 𝑉𝑜 = 𝑉𝑜 + 𝑉𝑇𝑂 + 𝛾 𝑉𝑜 + 𝑉𝐷𝐷 + 2𝜑𝐵 − 2𝜑𝐵 + 𝑉𝑜𝑣1

𝑉𝑖 = 𝑏𝑛(𝑣𝑜)𝑛

∞

𝑛=0

𝑏𝑛 =𝑓𝑛(𝑉𝑜 = 𝑉𝑂)

𝑛!

52 National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

Παραμόρφωση Ακόλουθου Πηγής - συνέχεια

Αντικαθιστώντας έχουμε :

Εξισώνοντας τους συντελεστές, βρίσκουμε :

οπότε

...

bb0

b1

2

1221

11

1

1b

1

3

1

22

b

b

𝑣𝑖 = 𝑏𝑛

∞

𝑛=1

𝑣𝑜𝑛

𝑣𝑜 = 𝑎𝑛∞𝑛=1 𝑣𝑖

𝑛 = 𝑎1𝑣𝑖 + 𝑎2𝑣𝑖2+𝑎3𝑣𝑖

3 +⋯

𝑣𝑖 = 𝑏1(𝑎1𝑣𝑖 + 𝑎2𝑣𝑖2+𝑎3𝑣𝑖

3 +⋯) + 𝑏2(𝑎1𝑣𝑖 + 𝑎2𝑣𝑖2+𝑎3𝑣𝑖

3 +⋯)2+…

53 National Technical University of Athens

Microelectronic Circuit Design Group

Yannis Papananos

Analog & RF IC Lecture Notes

Αντικαθιστώντας τέλος τις τιμές για τα bn έχουμε :

Με βάση τα παραπάνω, υπολογίζεται η παραμόρφωση για ημιτονοειδές

σήμα εισόδου :

γραμμική εξάρτηση από το πλάτος του σήματος εισόδου

Παραμόρφωση Ακόλουθου Πηγής - συνέχεια

𝑎2 =

𝛾8 𝑉𝑂 + 𝑉𝐷𝐷 + 2𝜑Β

−3 2

1 +𝛾2 V𝑂 + 𝑉𝐷𝐷 + 2𝜑Β

−1 2 3

𝑎1 =1

1 +𝛾2 V𝑂 + 𝑉𝐷𝐷 + 2𝜑Β

−1 2

𝐻𝐷2 =𝛾

16

V𝑂 + 𝑉𝐷𝐷 + 2𝜑Β−3 2

1 +𝛾2 V𝑂 + 𝑉𝐷𝐷 + 2𝜑Β

−1 2 2

HD2 =𝑎2𝑣𝑖

2

2

1

𝑎1𝑣𝑖 =1

2

𝑎2𝑎1

𝑣𝑖

𝑣𝑖 = 𝑣𝑖 sin𝜔𝑡

𝑣𝑜 = 𝑎1𝑣𝑖 sin𝜔𝑡 + 𝑎2𝑣𝑖 2sin2𝜔𝑡 + 𝑎3𝑣𝑖

3sin3𝜔𝑡 +⋯ =

𝑎1𝑣𝑖 sin𝜔𝑡 + 𝑎2𝑣𝑖

2

2(1 − cos 2𝜔𝑡) + 𝑎3

𝑣𝑖 3

4(3 sin𝜔𝑡 − sin 3𝜔𝑡) + ⋯

ΧρηματοδότησηΤο παρόν εκπαιδευτικό υλικό έχει αναπτυχθεί σταπλαίσια του εκπαιδευτικού έργου του διδάσκοντα.Το έργο «Ανοικτά Ακαδημαϊκά Μαθήματα» του ΕΜΠ έχειχρηματοδοτήσει μόνο την αναδιαμόρφωση του υλικού.Το έργο υλοποιείται στο πλαίσιο του ΕπιχειρησιακούΠρογράμματος «Εκπαίδευση και Δια Βίου Μάθηση»και συγχρηματοδοτείται από την Ευρωπαϊκή Ένωση(Ευρωπαϊκό Κοινωνικό Ταμείο) και από εθνικούς πόρους.