S7-300 Instruction List - Eltexmanuali.eltex.biz/Manuali_Siemens/opli_e.pdf · L 0.0 to 255.7 0.0...

Transcript of S7-300 Instruction List - Eltexmanuali.eltex.biz/Manuali_Siemens/opli_e.pdf · L 0.0 to 255.7 0.0...

S7-300 Instruction List

CPU 312 IFM, 314 IFM,313, 314, 315, 315-2 DP, 316

6ES7 398-8AA02-8BN0Edition 3

Contents

���� � ����!����� � ���� ������!��� ����� ��� �� �� �� �� �� �� �� ��

����#��!��� � ���� ������� ���� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� ��

���� !�� ���� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� ��

%����� � ��� ���� ��� ���� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� ��

%��"!���� ���� � $�!�� �������!� ���� ��� ���� �� �� �� �� �� �� �� ��

�� !� ��� �� !�"�!��� ���� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� �� ��Bit Logic Instructions 26. . . . . . . . . . . . . . . . . . . . . . . Bit Logic Instructions with Parenthetical

Expressions 36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . ORing of AND Operations 38. . . . . . . . . . . . . . . . . . . Logic Instructions with Timers and Counters 40. . . . . Word Logic Instructions with the Contents of

Accumulator 1 44. . . . . . . . . . . . . . . . . . . . . . . . . . . Evaluating Conditions Using AND, OR and

EXCLUSIVE OR 46. . . . . . . . . . . . . . . . . . . . . . . . Edge-Triggered Instructions 62. . . . . . . . . . . . . . . . . . Setting/Resetting Bit Addresses 64. . . . . . . . . . . . . . . . Instructions Directly Affecting the RLO 70. . . . . . . . . Timer Instructions 72. . . . . . . . . . . . . . . . . . . . . . . . . . Counter Instructions 76. . . . . . . . . . . . . . . . . . . . . . . . . Load Instructions 78. . . . . . . . . . . . . . . . . . . . . . . . . . . Load Instructions for Timers and Counters 88. . . . . . . Transfer Instructions 90. . . . . . . . . . . . . . . . . . . . . . . . Load and Transfer Instructions for Address

Registers 98. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Load and Transfer Instructions for the Status Word 102Load Instructions for DB Number and Data Length 104Integer Math (16 Bits) 106. . . . . . . . . . . . . . . . . . . . . . . Integer Math (32 Bits) 108. . . . . . . . . . . . . . . . . . . . . . . Floating-Point Math (32 Bits) 110. . . . . . . . . . . . . . . . . Square Root and Square Instructions (32 Bits) 112. . . . Logarithmic Function (32 Bits) 114. . . . . . . . . . . . . . . . Trigonometrical Functions (32 Bits) 116. . . . . . . . . . . . Adding Constants 118. . . . . . . . . . . . . . . . . . . . . . . . . . . Adding Using Address Registers 120. . . . . . . . . . . . . . .

Comparison Instructions with Integers (16 Bits) 122. . . Comparison Instructions with Integers (32 Bits) 124. . . Comparison Instructions with Real Numbers

(32 Bits) 126. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Shift Instructions 128. . . . . . . . . . . . . . . . . . . . . . . . . . . Rotate Instructions 130. . . . . . . . . . . . . . . . . . . . . . . . . . Accumulator Transfer Instructions, Incrementing

and Decrementing 132. . . . . . . . . . . . . . . . . . . . . . . . Program Display and Null Operation Instructions 134. . Data Type Conversion Instructions 136. . . . . . . . . . . . . Forming the Ones and Twos Complements 140. . . . . . . Block Call Instructions 142. . . . . . . . . . . . . . . . . . . . . . Block End Instructions 148. . . . . . . . . . . . . . . . . . . . . . . Exchanging Shared Data Block and Instance Data

Block 150. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Jump Instructions 152. . . . . . . . . . . . . . . . . . . . . . . . . . . Instructions for the Master Control Relay (MCR) 160. .

������!����� ����%� ��� �� !�"�!��� ����� �� �� �� �� �� �� �� �� �� �� �� �� �� �� ��

Convention:

In the following, the CPU 312 IFM is called CPU 312*.

In the following, the CPU 314 IFM is called CPU 314*.

In the following, the CPU 315-2 DP is called CPU 315-2.

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

0 1

Contents Contents

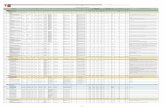

Address Identifiers and ParameterRanges

Addr. Parameter Ranges DescriptionAddr.ID 312* 313 314 314* 315/316 315-2

Q 0.0 to 31.7 0.0 to 127.7 0.0 to 123.7 0.0 to 127.7 Output bit (in PIQ)Q

124.7 to127.7

– 124.0 to127.7

– ... integrated outputs

QB 0 to 31 0 to 127 0 to 123 0 to 127 Output byte (in PIQ)Q

124 to 127 – 124 to 127 – ... integrated outputs

QW 0 to 30 0 to 126 0 to 122 0 to 126 Output word in (PIQ)Q

124 to 126 – 124 to 126 – ... integrated outputs

QD 0 to 28 0 to 124 0 to 120 0 to 124 Output double word(in PIQ)

124 – 124 – ... integrated outputs

B – – Byte with general register-indirect addressing

W – – Word with general regis-ter-indirect addressing

D – – Double word with generalregister-indirect addres-sing

DBX 0.0 to 8191.7 0.0 to 8191.7 Data bit in data block

DB 1 to 63 1 to 127 1 to 127 Data block

DBB 0 to 6143 0 to 8191 0 to 8191 Data byte in DB

DBW 0 to 6142 0 to 8190 0 to 8190 Data word in DB

DBD 0 to 6140 0 to 8188 0 to 8188 Data double word in DB

Addresses Identifiers and Parameter Ranges Addresses Identifiers and Parameter Ranges

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

2 3

Addr. Parameter RangesDescription

Addr.ID 312* 313 314 314* 315/316 315-2

Description

DIX 0.0 to 8191.7 0.0 to 8191.7 Data bit in instance DB

DI 1 to 63 1 to 127 1 to 127 Instance data block

DIB 0 to 6143 0 to 8191 0 to 8191 Data byte in instance DB

DIW 0 to 6142 0 to 8190 0 to 8190 Data word in instance DB

DID 0 to 6140 0 to 8188 0 to 8188 Data double word in instance DB

I 0.0 to 31.7 0.0 to 127.7 0.0 to 123.7 0.0 to 127.7 Input bit (in PII)

124.0 to127.7

– 124.0 to127.7

– ... integrated inputs

IB 0 to 31 0 to 127 0 to 123 0 to 127 Input byte (in PII)

124 to 127 – 124 to 127 – ... integrated inputs

IW 0 to 30 0 to 127 0 to 122 0 to 126 Input word (in PII)

124 to 126 – 124 to 126 – ... integrated inputs

ID 0 to 28 0 to 124 0 to 120 0 to 124 Input double word (in PII)

124 – 124 – ... integrated inputs

L 0.0 to 255.7 0.0 to 255.7 Local data bit

LB 0 to 255 0 to 255 Local data byte

LW 0 to 254 0 to 254 Local data word

LD 0 to 252 0 to 252 Local data double word

M 0.0 to 127.7 0.0 to 255.7 0.0 to 255.7 Bit memory bit

MB 0 to 127 0 to 255 0 to 255 Bit memory byte

MW 0 to 126 0 to 254 0 to 254 Bit memory word

MD 0 to 124 0 to 252 0 to 252 Bit memory double word

Addresses Identifiers and Parameter Ranges Addresses Identifiers and Parameter Ranges

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

4 5

Addr. Parameter RangesDescription

Addr.ID 312* 313 314 314* 315/316 315-2

Description

PQB 0 to 31 0 to 31 0 to 767 0 to 751 0 to 767 0 to 1023 Peripheral output byte(direct I/O access)

Q

124

p p y(direct I/O access)

256 to 383 256 to 383

PQW 0 to 30 0 to 30 0 to 766 0 to 750 0 to 766 0 to 1022 Peripheral output word(direct I/O access)

Q

256 to 382 256 to 382

p p(direct I/O access)

PQD 0 to 28 0 to 28 0 to 764 0 to 748 0 to 764 0 to 1020 Peripheral output double word(direct I/O access)

Q

256 to 380 256 to 380

p p(direct I/O access)

PIB 0 to 31 0 to 31 0 to 767 0 to 751 0 to 767 0 to 1023 Peripheral input byte(direct I/O access)

124 to 125

p p y(direct I/O access)

256 to 383 256 to 383

PIW 0 to 30 0 to 30 0 to 766 0 to 750 0 to 766 0 to 1022 Peripheral input word(direct I/O access)

124

p p(direct I/O access)

256 to 382 256 to 382

PID 0 to 28 0 to 28 0 to 764 0 to 748 0 to 764 0 to 1020 Peripheral input double word(direct I/O access)

256 to 380 256 to 380

p p(direct I/O access)

T 0 to 63 0 to 127 0 to 127 Timer

Z 0 to 31 0 to 35 0 to 63 0 to 63 Counter

Para-meter

– – Instruction addressed via parameter

B# – – Constant, 2 or 4 bytes

Addresses Identifiers and Parameter Ranges Addresses Identifiers and Parameter Ranges

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

6 7

Addr. Parameter RangesDescription

Addr.ID 312* 313 314 314* 315/316 315-2

Description

D# – – IEC data constant

L# – – 32-bit integer constant

P# – – Pointer constant

S5T# – – S5 time constant (16 bits) 1

T# – 2 2 Time constant (16/32 bits)

TOD# – – IEC time constant (32 bits)

C# – – Counter constant (16/32 bits)

2# – – Binary constant (16/32 bits)

16# – – Hexadecimal constant (16/32 bits)

1 for loading of S5 timers 2 T#1D_5H_3M_1S_2MS

Addresses Identifiers and Parameter Ranges Addresses Identifiers and Parameter Ranges

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

8 9

Abbreviations and MnemonicsThe following abbreviations and mnemonics are used in theInstruction List:

Abbre-viations

Description Example

k8 8-bit constant 32

k16 16-bit constant 62 531

k32 32-bit constant 127 624

i8 8-bit integer –155

i16 16-bit integer +6523

i32 32-bit integer –2 222 222

m P#x.y (pointer) P#240.3

n Binary constant 1001 1100

p Hexadecimal constant EA12

q Real number (32-bitfloating-point number)

12.34567E+5

LABEL Symbolic jump address(max. 4 characters)

DEST

Abbreviations and Mnemonics Abbreviations and Mnemonics

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

10 11

RegistersACCU1 and ACCU2 (32 Bits)

The accumulators are registers for processing bytes, words ordouble words. The operands are loaded into the accumulators,where they are logically gated. The result of the logic operation(RLO) is in ACCU1.

The accumulators are 32 bits long.

Accumulator designations:

ACCU Bits

ACCU1 ACCU2 Bits 0 to 31

ACCU1-L ACCU2-L Bits 0 to 15

ACCU1-H ACCU2-H Bits 16 to 31

ACCU1-LL ACCU2-LL Bits 0 to 7

ACCU1-LH ACCU2-LH Bits 8 to 15

ACCU1-HL ACCU2-HL Bits 16 to 23

ACCU1-HH ACCU2-HH Bits 24 to 31

Address Registers AR1 and AR2 (32 Bits)

The address registers contain the area-internal or area-crossing ad-dresses for instructions using indirect addressing. The address regis-ters are 32 bits long.

The area-internal and/or area-crossing addresses have the followingsyntax:

� Area-internal address

00000000 00000bbb bbbbbbbb bbbbbxxx

� Area-crossing address

10000yyy 00000bbb bbbbbbbb bbbbbxxx

Legend: b Byte addressx Bit numbery Area identifier (see section “Examples of

Addressing”)

Status Word (16 Bits)

The status word bits are evaluated or set by the instructions.

The status word is 16 bits long.

Bit Assignment Description

0 FC First check bit *

1 RLO Result of (previous) logic operation

2 STA Status *

3 OR Or *

4 OS Stored overflow

5 OV Overflow

6 CC 0 Condition code

7 CC 1 Condition code

8 BR Binary result

9 ... 15 Unassigned –

* Bit cannot be evaluated in the user program with the L STWinstruction since it is not updated at program runtime.

Registers Registers

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

12 13

Examples of Addressing

Addressing Examples Description

Direct Addressing

L +27 Load 16-bit integer constant“27” into ACCU1

L L#–1 Load 32-bit integer constant“–1” into ACCU1

L 2#1010101010101010 Load binary constant intoACCU1

L DW#16#A0F0_BCFD Load hexadecimal constant intoACCU1

L ’END’ Load ASCII character intoACCU1

L T#500 ms Load time value into ACCU1

L C#100 Load count value into ACCU1

L B#(100,12) Load 2-byte constant

L B#(100,12,50,8) Load 4-byte constant

L P#10.0 Load area-internal pointer intoACCU1

L P#E20.6 Load area-crossing pointer intoACCU1

L –2.5 Load real number into ACCU1

L D#1995–01–20 Load date

L TOD#13:20:33.125 Load time of day

Addressing Examples Description

Direct Addressing

A I 0.0 ANDing of input bit 0.0

L IB 1 Load input byte 1 into ACCU1

L IW 0 Load input word 0 intoACCU1

L ID 0 Load input double word 0 intoACCU1

Indirect Addressing of Timers/Counters

SP T [LW 8] Start timer; the timer number isin local word 8

CU C [LW 10] Start counter; the counter num-ber is in local data word 10

Area-Internal Memory-Indirect Addressing

A I [LD 12]Example: L P#22.2

T LD 12A I [LD 12]

AND operation: The address ofthe input is in local data doubleword 12 as pointer

A I [DBD 1] AND operation: The address ofthe input is in data doubleword 1 of the DB as pointer

A Q [DID 12] AND operation: The address ofthe output is in data doubleword 12 of the instance DB aspointer

A Q [MD 12] AND operation: The address ofthe output is in memory markerdouble word 12 of the instanceDB as pointer

Examples of Addressing Examples of Addressing

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

14 15

Addressing Examples Description

Area-Internal Register-Indirect Addressing

A I [AR1,P#12.2] AND operation: The address ofthe input is calculated from the“pointer value in AR1+P#12.2”

Area-Crossing Register-Indirect Addressing

For area-crossing register-indirect addressing, bits 24 to 26 of theaddress must also contain an area identifier. The address is in theaddress register.

Area Coding Areaidentifier (binary) hex.

P 1000 0000 80 I/O areaI 1000 0001 81 Input areaQ 1000 0010 82 Output areaM 1000 0011 83 Bit memory areaDB 1000 0100 84 Data areaDI 1000 0101 85 Instance data areaL 1000 0110 86 Local data areaVL 1000 0111 87 Predecessor local data

(access to local data ofinvoking block seepage 15)

L B [AR1,P#8.0] Load byte into ACCU1: Theaddress is calculated from the“pointer value in AR1+ P#8.0”

A [AR1,P#32.3] AND operation: The address ofthe operand is calculated fromthe “pointer value in AR1+P#32.3”

Addressing Examples Description

Addressing Via Parameters

A Parameter Addressing via parameters

Examples of how to calculate the pointer

� Example for sum of bit addresses �7:

LAR1 P#8.2A I [AR1,P#10.2]

Result: Input 18.4 is addressed (by adding the byte and bitaddresses)

� Example for sum of bit addresses�7:

L MD 0 Random pointer, e.g. P#10.5LAR1A I [AR1,P#10.7]

Result: Input 21.4 is addressed (by adding the byte and bitaddresses with carry)

Examples of Addressing Examples of Addressing

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

16 17

Execution Times with IndirectAddressingYou must calculate the execution times when using indirect addres-sing. This chapter shows you how.

Two-Part Statement

A statement with indirectly addressed instructions consists of twoparts:

Part 1: Load the address of the instruction

Part 2: Execute the instruction

In other words, you must calculate the execution time of a state-ment with indirectly addressed instructions from these two parts.

Calculating the Execution Time

The total execution time is calculated as follows:

Time required for loading the address

+ execution time of the instruction

= Total execution time of the instruction

The execution times listed in the chapter entitled “List of Instruc-tions” apply to the execution times of the second part of an instruc-tion, i.e. for the actual execution of an instruction.

You must then add the time required for loading the address of theinstruction to this execution time (see Table on following page).

The execution time for loading the address of the instruction fromthe various areas is shown in the following table. You will also findthis table on the fold-out part of the cover. You do not have tochange the page when calculating the execution time.

Execution Time in �s

Address is in ... 312*/313 314/314* 315/316/315-2

Bit memory area MWordDouble word

1.73.5

0.72.3

0.82.1

Data block DB/DXWordDouble word

5.26.7

2.83.9

3.04.1

Local data area LWordDouble word

2.03.7

0.82.6

0.92.2

AR1/AR2 (area-internal) 3.0 1.9 1.7

AR1/AR2 (area-crossing) 4.9 3.9 3.2

Parameter (word) ... for:� Timers� Counters�� Block calls

4.0 2.5 2.1

Parameter (double word) ...for

Bits, bytes, wordsand double words

7.3 5.3 4.3

The pages that follow contain examples for calculating the instruc-tion run time for the various indirectly addressed instructions.

Execution Times with Indirect Addressing Execution Times with Indirect Addressing

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

18 19

Examples of Calculations (for the CPU 314)

You will find a few examples here for calculating the executiontimes for the various methods of indirect addressing. Executiontimes are calculated for the CPU 314.

Calculating the Execution T imes for Area-InternalMemory-Indirect Addressing

Example: A I [DBD 12]

Step 1: Load the contents of DBD 12 (time required is listedin the table on page 19)

Address is in ... Execution Time in �s

Bit memory area MWordDouble word

0.72.3

Data block DB/DIWordDouble word 3.9

2.8

Step 2: AND the input addressed in this way (you will findthe execution time in the tables in the chapter entitled“List of Instructions”)

Typical Execution Time in �s

Direct Addressing Indirect Addressing

0.2

:

2.0+

:Time forA I

Total execution time:4.9 �s

+ 2.1 �s= 7.0 �s

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

20 21

Execution Times with Indirect Addressing Execution Times with Indirect Addressing

Calculating the Execution T ime for Area-InternalRegister-Indirect Addressing

Example: A I [AR1, P#34.3]

Step 1: Load the contents of AR1, and increment it by theoffset 34.3 (the time required is listed in the table onpage 19)

Address is in ... Execution Time in �s

: :

AR1/AR2 (area-internal) 1.9

: :

Step 2: AND the input addressed in this way (you will findthe execution time in the tables in the chapter entitled“List of Instructions”)

Typical Execution Time in �s

Direct Addressing Indirect Addressing

0.2

:

2.0+

:Time forA I

Total execution time:1.9 �s

+ 2.0 �s= 3.9 �s

Calculating the Execution T ime for Area-CrossingMemory-Indirect Addressing

Example: A [AR1, P#23.1] ... with I 1.0 in AR1

Step 1: Load the contents of AR1, and increment them bythe offset 23.1 (the time required is in the table onpage 19)

Address is in ... Execution Time in �s

: :

AR1/AR2 (area-crossing) 3.9

: :

Step 2: AND the input addressed in this way (you will findthe execution time in the tables in the chapter entitled“List of Instructions”)

Typical Execution Timetypische Ausführungszeit in �s

Direct Addressing Indirect Addressing

0.2

:

2.0+

:Time forA I

Total execution time:3.9 �s

+ 2.0 �s= 5.9 �s

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

22 23

Execution Times with Indirect Addressing Execution Times with Indirect Addressing

Execution T ime for Addressing V ia Parameters

Example: A Parameter ... with I 0.5 in the block parameter list

Step 1: Load input I 0.5 addressed via the parameter (thetime required is in the table on page 19).

Address is in ... Execution Time in �s

: :

: :

Parameter (double word) 5.3

Step 2: AND the input addressed in this way (you will findthe execution time in the tables in the chapter entitled“List of Instructions”)

Typical Execution Time in �s

Direct Addressing Indirect Addressing

0.2

:

2.0+

:Time forA I

Total execution time:5.3 �s

+ 2.0 �s= 7.3 �s

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

24 25

Execution times with Indirect Addressing Execution times with Indirect Addressing

List of Instructions

This chapter contains the complete list of S7-300 instructions. Thedescriptions have been kept as concise as possible. You will find adetailed functional description in the various STEP 7 referencemanuals.Please note that, in the case of indirect addressing (examples see

page 14), you must add the time required for loading the address ofthe particular instruction to the execution times listed (see page 19).

Bit Logic Instructions

Examining the signal state of the addressed instruction and gatingthe result with the RLO according to the appropriate logic function.

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Addressing Indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

A I/QMLDBX/DIX

AND input/outputAND bit memoryAND local data bitAND data bit

1 2/21 2/2

22

0.71.52.25.2

0.20.60.82.7

0.30.60.92.8

2.5+2.7+3.0+4.2+

2.0+2.2+2.2+2.8+

1.6+1.7+1.8+2.5+

[AR1,m][AR2,m]Parameter

AND I/Q/M/L/DBX/DIX(addressed (area-crossing) viaAR1/AR2 or via parameter)

2 –––

–––

–––

+++

+++

+++

Status word for: A BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – Yes – Yes Yes

Instruction affects: – – – – – Yes Yes Yes 1

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

26 27

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Addressing Indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

AN I/QMLDBX/DIX

AND NOT input/outputAND NOT bit memoryAND NOT local data bitAND NOT data bit

2 0.40.70.93.6

1.41.92.55.5

0.50.70.93.0

0.50.81.03.1

2.9+3.1+3.4+4.6+

2.2+2.4+2.4+2.9+

1.9+2.1+2.2+2.8+

[AR1,m][AR2,m]Parameter

AND NOT I/Q/M/L/DBX/DIX(addressed (area-crossing) viaAR1/AR2 or via parameter)

2 –––

–––

–––

+++

+++

+++

Status word for: AN BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – Yes – Yes Yes

Instruction affects: – – – – – Yes Yes Yes 1

1 Plus time required for loading the address of the instruction(see page 19)

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

2928

In- Length Typical Execution Time in �sInstruc-tion

AddressIdentifier

Description inWords Direct Addressing Indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

O I/QMLDBX/DIX

OR input/outputOR bit memoryOR local data bitOR data bit

1 2/21 2/2

22

0.71.52.25.2

0.20.60.82.7

0.30.70.92.9

2.5+2.7+3.0+4.2+

2.0+2.2+2.2+2.8+

1.6+1.7+1.8+2.5+

[AR1,m][AR2,m]Parameter

OR I/Q/M/L/DBX/DIX (addres-sed (area-crossing) viaAR1/AR2 or via parameter)

2 –––

–––

–––

+++

+++

+++

ON I/QMLDBX/DIX

OR NOT input/outputOR NOT bit memoryOR NOT local data bitOR NOT data bit

12/212/2

22

1.41.92.55.5

0.50.70.93.0

0.50.81.03.1

2.9+3.1+3.4+4.6+

2.2+2.4+2.4+2.9+

1.9+2.0+2.2+2.8+

[AR1,m][AR2,m]Parameter

OR NOT I/Q/M/L/DBX/DIX(addressed (area-crossing) viaAR1/AR2 or via parameter)

2 –––

–––

–––

+++

+++

+++

Status word for: O, ON BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes Yes

Instruction affects: – – – – – 0 Yes Yes 1

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

3130

In- Length Typical Execution Time in �sInstruc-tion

AddressIdentifier

Description inWords Direct Addressing Indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

X I/QMLDBX/DIX

EXCLUSIVE OR input/outputEXCLUSIVE OR bit memoryEXCLUSIVE OR local data bitEXCLUSIVE OR data bit

2 0.71.52.25.2

0.30.60.82.8

0.30.70.92.9

2.5+2.7+3.0+4.2+

1.9+2.1+2.1+2.6+

1.6+1.7+1.9+2.5+

[AR1,m][AR2,m]Parameter

EXCLUSIVE ORI/Q/M/L/DBX/DIX (addressed(area-crossing) via AR1/AR2 orvia parameter)

2 –––

–––

–––

+++

+++

+++

Status word for: X BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes Yes

Instruction affects: – – – – – 0 Yes Yes 1

1 Plus time required for loading the address of the instruction(see page 19)

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

3332

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Addressing Indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

XN I/Q

M

L

DBX/DIX

EXCLUSIVE OR NOTinput/outputEXCLUSIVE OR NOTbit memoryEXCLUSIVE OR NOTlocal data bitEXCLUSIVE OR NOT data bit

2 1.4

1.9

2.5

5.5

0.5

0.7

0.9

3.0

0.5

0.8

1.0

3.1

2.9+

3.1+

3.4+

4.6+

2.2+

2.4+

2.4+

2.9+

1.9+

2.0+

2.2+

2.8

[AR1,m][AR2,m]Parameter

EXCLUSIVE OR NOTI/Q/M/L/DBX/DIX (addressed(area-crossing) via AR1/AR2 orvia parameter)

2 –––

–––

–––

+++

+++

+++

Status word for: XN BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes Yes

Instruction affects: – – – – – 0 Yes Yes 1

1 Plus time required for loading the address of the instruction(see page 19)

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

3534

Bit Logic Instructions with ParentheticalExpressions

Saving the BR, RLO and OR bits and a function identifier(A, AN, ...) to the nesting stack. Seven nesting levels are possibleper block.

In-struc-tion

AddressIdentifier

DescriptionLength

in

Words

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

A( AND left parenthesis 1 2.9 1.7 1.7

AN( AND NOT left parenthesis 1 2.9 1.7 1.7

O( OR left parenthesis 1 2.9 1.4 1.7

ON( OR NOT left parenthesis 1 2.9 1.4 1.7

X( EXCLUSIVE ORleft parenthesis

1 2.9 1.4 1.7

XN( EXCLUSIVE OR NOTleft parenthesis

1 2.9 1.4 1.7

Status word for: A(, AN(, O(, ON(, X(,XN(

BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: Yes – – – – Yes – Yes Yes

Instruction affects: – – – – – 0 1 – 0

) Right parenthesis, popping anentry off the nesting stack, gat-ing the RLO with the currentRLO in the processor

1 3.3 1.7 1.9

Status word for: ) BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes –

Instruction affects: Yes – – – – Yes 1 Yes 1

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

3736

ORing of AND Operations

The ORing of AND operations is implemented according to therule: AND before OR.

In-struc-tion

AddressIdentifier

DescriptionLength

in

Words

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

O ORing of AND operationsaccording to the rule:AND before OR

1 1.4 0.3 0.5

Status word for: O BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – Yes – Yes Yes

Instruction affects: – – – – – Yes 1 – Yes

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

3938

Logic Instructions with Timers andCounters

Examining the signal state of the addressed timer/counter andgating the result with the RLO according to the appropriatelogic function.

In- Length Typical Execution Time in �sInstruc-tion

AddressIdentifier

Description inWords Direct Addressing Indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

A TC

AND timerAND counter

1 2/2 2.41.7

0.80.6

0.90.6

3.3+3.0+

2.2+1.9+

2.1+1.8+

Timer para.Counter p.

AND timer/counter(addressed via parameter)

2 ––

––

––

++

++

++

AN TC

AND NOT timerAND NOT counter

12/2 3.02.4

1.00.8

1.10.9

3.7+3.3+

2.4+2.2+

2.3+2.1+

Timer para.Counter p.

AND NOT timer/counter(addressed via parameter)

2 ––

––

––

++

++

++

Status word for: A, AN BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – Yes – Yes Yes

Instruction affects: – – – – – Yes Yes Yes 1

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

4140

In- Lengthi

Typical Execution Time in �sstruc-tion

AddressIdentifier

Description

gin

Words Direct Addressing Indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

O TC

OR timerOR counter

1 2/2 2.41.7

0.80.6

0.90.6

3.3+3.0+

2.2+1.9+

2.1+1.8+

Timerpara.Counter p.

OR timer/counter(addressed via parameter)

2 ––

––

––

++

++

++

ON TC

OR NOT timerOR NOT counter

1 2/2 3.02.4

1.00.8

1.10.9

3.7+3.3+

2.4+2.2+

2.3+2.1+

Timerpara.Counter p.

OR NOT timer/counter(addressed via parameter)

2 ––

––

––

++

++

++

X TC

EXCLUSIVE OR timerEXCLUSIVE OR counter

2 2.41.7

0.80.6

0.90.6

3.3+3.0+

2.2+1.9+

2.1+1.8+

Timerpara.Counter p.

EXCLUSIVE OR timer/counter(addressed via parameter)

2 ––

––

––

++

++

++

XN TC

EXCLUSIVE OR NOT timerEXCLUSIVE OR NOT counter

2 3.02.4

1.01.0

1.10.9

3.7+3.3+

2.4+2.2+

2.3+2.1+

Timerpara.Counter p.

EXCLUSIVE OR NOTtimer/counter (addressed viaparameter)

2 ––

––

––

++

++

++

Status word for: O, ON, X, XN BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes Yes

Instruction affects: – – – – – 0 Yes Yes 1

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

4342

Word Logic Instructions with theContents of Accumulator 1

Gating the contents of ACCU1 and/or ACCU1-L with a word ordouble word according to the appropriate function. The word or

double word is either a constant in the instruction or in ACCU2.The result is in ACCU1 and/or ACCU1-L.

In-struc-tion

AddressIdentifier

DescriptionLength

in

Words

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

AW AND ACCU2-L 1 1.7 0.5 0.6

AW k16 AND 16-bit constant 2 2.3 0.7 0.9

OW OR ACCU2-L 1 1.7 0.5 0.6

OW k16 OR 16-bit constant 2 2.3 0.7 0.9

XOW EXCLUSIVE OR ACCU2-L 1 1.7 0.5 0.6

XOW k16 EXCLUSIVE OR 16-bitconstant

2 2.3 0.7 0.9

AD AND ACCU2 1 3.4 1.9 2.0

AD k32 AND 32-bit constant 3 4.1 2.1 2.3

OD OR ACCU2 1 3.4 1.9 2.0

OD k32 OR 32-bit constant 3 4.1 2.1 2.3

XOD EXCLUSIVE OR ACCU2 1 3.4 1.9 2.0

XOD k32 EXCLUSIVE OR 32-bitconstant

3 4.1 2.1 2.3

Status word for: AW, OW, XOW, AD,OD, XOD

BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – – –

Instruction affects: – Yes 0 0 – – – – –

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

4544

Evaluating Conditions Using AND, ORand EXCLUSIVE OR

Examining the specified conditions for their signal status, and gat-ing the result with the RLO according to the appropriate function.

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

A ==0 AND result=0(CC 1=0) and (CC 0=0)

1 1.5 0.5 0.6

A >0 AND result>0(CC 1=1) and (CC 0=0)

1 2.3 0.7 0.9

A <0 AND result<0(CC 1=0) and (CC 0=1)

1 2.3 0.7 0.9

A <>0 AND result�0((CC 1=0) and (CC 0=1) or(CC 1=1) and (CC 0=0))

1 1.5 0.5 0.6

A <=0 AND result<=0((CC 1=0) and (CC 0=1) or(CC 1=0) and (CC 0=0))

1 1.5 0.5 0.6

A >=0 AND result>=0((CC 1=1) and (CC 0=0) or(CC 1=0) and (CC 0=0))

1 1.5 0.5 0.6

Status word for: A condition BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: Yes Yes Yes Yes Yes Yes – Yes Yes

Instruction affects: – – – – – Yes Yes Yes 1

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

4746

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

A UO AND unordered(CC 1=1) and (CC 0=1)

1 1.5 0.5 0.6

A OS AND OS=1 1 0.7 0.2 0.3

A BR AND BR=1 1 0.7 0.2 0.3

A OV AND OV=1 1 0.7 0.2 0.3

Status word for: A condition BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: Yes Yes Yes Yes Yes Yes – Yes Yes

Instruction affects: – – – – – Yes Yes Yes 1

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

4948

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

AN ==0 AND NOT result=0(CC 1=0) and (CC 0=0)

1 1.5 0.5 0.6

AN >0 AND NOT result>0(CC 1=1) and (CC 0=0)

1 2.3 0.7 0.9

AN <0 AND NOT result<0(CC 1=0) and (CC 0=1)

1 2.3 0.7 0.9

AN <>0 AND NOT result�0((CC 1=0) and (CC 0=1) or(CC 1=1) and (CC 0=0))

1 2.3 0.7 0.9

AN <=0 AND NOT result<=0((CC 1=0) and (CC 0=1) or(CC 1=0) and (CC 0=0))

1 0.7 0.2 0.3

AN >=0 AND NOT result>=0((CC 1=1) and (CC 0=0) or(CC 1=0) and (CC 0=0))

1 0.7 0.2 0.3

AN UO AND NOT unordered(CC 1=1) and (CC 0=1)

1 2.3 0.7 0.9

AN OS AND NOT OS=1 1 1.5 0.5 0.6

AN OV AND NOT OV=1 1 1.5 0.5 0.6

AN BR AND NOT BR=1 1 1.5 0.5 06

Status word for: AN condition BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: Yes Yes Yes Yes Yes Yes – Yes Yes

Instruction affects: – – – – – Yes Yes Yes 1

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

5150

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

O ==0 OR result=0(CC 1=0) and (CC 0=0)

1 1.5 0.5 0.6

O >0 OR result>0(CC 1=1) and (CC 0=0)

1 2.3 0.7 0.9

O <0 OR result<0(CC 1=0) and (CC 0=1)

1 2.3 0.7 0.9

O <>0 OR result�0((CC 1=0) and (CC 0=1) or(CC 1=1) and (CC 0=0))

1 1.5 0.5 0.6

O <=0 OR result<=0((CC 1=0) and (CC 0=1) or(CC 1=0) and (CC 0=0))

1 1.5 0.5 0.6

O >=0 OR result>=0((CC 1=1) and (CC 0=0) or(CC 1=0) and (CC 0=0))

1 1.5 0.5 0.6

O UO OR unordered(CC 1=1) and (CC 0=1)

1 1.5 0.5 0.6

O OS OR OS=1 1 0.7 0.2 0.3

O OV OR OV=1 1 0.7 0.2 0.3

O BR OR BR=1 1 0.7 0.2 0.3

Status word for: O condition BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: Yes Yes Yes Yes Yes – – Yes Yes

Instruction affects: – – – – – 0 Yes Yes 1

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

5352

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

ON ==0 OR NOT result=0(CC 1=0) and (CC 0=0)

1 1.5 0.5 0.6

ON >0 OR NOT result>0(CC 1=1) and (CC 0=0)

1 2.3 0.7 0.9

ON <0 OR NOT result<0(CC 1=0) and (CC 0=1)

1 2.3 0.7 0.9

ON <>0 OR NOT result�0((CC 1=0) and (CC 0=1) or(CC 1=1) and (CC 0=0))

1 2.3 0.7 0.9

ON <=0 OR NOT result<=0((CC 1=0) and (CC 0=1) or(CC 1=0) and (CC 0=0))

1 0.7 0.2 0.3

ON >=0 OR NOT result>=0((CC 1=1) and (CC 0=0) or(CC 1=0) and (CC 0=0))

1 0.7 0.2 0.3

ON UO OR NOT unordered(CC 1=1) and (CC 0=1)

1 2.3 0.7 0.9

ON OS OR NOT OS=1 1 1.5 0.7 0.6

ON OV OR NOT OV=1 1 1.5 0.5 0.6

ON BR OR NOT BR=1 1 1.5 0.5 0.6

Status word for: ON condition BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: Yes Yes Yes Yes Yes – – Yes Yes

Instruction affects: – – – – – 0 Yes Yes 1

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

5554

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

X ==0 EXCLUSIVE OR result=0(CC 1=0) and (CC 0=0)

1 1.5 0.5 0.6

X >0 EXCLUSIVE OR result>0(CC 1=1) and (CC 0=0)

1 2.3 0.7 0.9

X <0 EXCLUSIVE OR result<0(CC 1=0) and (CC 0=1)

1 2.3 0.7 0.9

X <>0 EXCLUSIVE OR result�0((CC 1=0) and (CC 0=1) or(CC 1=1) and (CC 0=0))

1 1.5 0.5 0.6

X <=0 EXCLUSIVE OR result<=0((CC 1=0) and (CC 0=1) or(CC 1=0) and (CC 0=0))

1 1.5 0.5 0.6

X >=0 EXCLUSIVE OR result>=0((CC 1=1) and (CC 0=0) or(CC 1=0) and (CC 0=0))

1 1.5 0.5 0.6

X UO EXCLUSIVE OR unordered(CC 1=1) and (CC 0=1)

1 1.5 0.5 0.6

X OS EXCLUSIVE OR OS=1 1 0.7 0.2 0.3

X OV EXCLUSIVE OR OV=1 1 0.7 0.2 0.3

X BR EXCLUSIVE OR BR=1 1 0.7 0.2 0.3

Status word for: X condition BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: Yes Yes Yes Yes Yes – – Yes Yes

Instruction affects: – – – – – 0 Yes Yes 1

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

5756

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

XN ==0 EXCLUSIVE OR NOTresult=0(CC 1=0) and (CC 0=0)

1 1.5 0.5 0.6

XN >0 EXCLUSIVE OR NOTresult>0(CC 1=1) and (CC 0=0)

1 2.3 0.7 0.9

XN <0 EXCLUSIVE OR NOTresult<0(CC 1=0) and (CC 0=1)

1 2.3 0.7 0.9

XN <>0 EXCLUSIVE OR NOTresult�0((CC 1=0) and (CC 0=1) or(CC 1=1) and (CC 0=0))

1 2.3 0.7 0.9

XN <=0 EXCLUSIVE OR NOTresult<=0((CC 1=0) and (CC 0=1) or(CC 1=0) and (CC 0=0))

1 0.7 0.2 0.3

XN >=0 EXCLUSIVE OR NOTresult>=0((CC 1=1) and (CC 0=0) or(CC 1=0) and (CC 0=0))

1 0.7 0.2 0.3

XN UO EXCLUSIVE OR NOTunordered(CC 1=1) and (CC 0=1)

1 2.3 0.7 0.9

XN OS EXCLUSIVE OR NOT OS=1 1 1.5 0.5 0.6

Status word for: XN condition BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: Yes Yes Yes Yes Yes – – Yes Yes

Instruction affects: – – – – – 0 Yes Yes 1

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

5958

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

XN OV EXCLUSIVE OR NOT OV=1 1 1.5 0.5 0.6

XN BR EXCLUSIVE OR NOT BR=1 1 1.5 0.5 0.6

Status word for: XN condition BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: Yes Yes Yes Yes Yes – – Yes Yes

Instruction affects: – – – – – 0 Yes Yes 1

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

6160

Edge-Triggered Instructions

Detection of an edge change. The current signal state of the RLO iscompared with the signal state of the instruction or “edge bitmemory”. FP detects a change in the RLO from “0” to “1”; FNdetects a change in the RLO from “1” to “0”.

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Adressing Indirect Adressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

FP I/Q

ML

Detecting the positive edge inthe RLO. The bit addressed inthe instruction is the auxiliaryedge bit memory.

2 2.0

3.53.8

0.7

1.41.5

0.8

1.51.6

3.6+

3.9+4.1+

2.7+

2.9+2.9+

2.4+

2.7+2.7+L

DBX/DIX[AR1,m][AR2,m]Parameter

edge bit memory. 3.86.7–––

1.52.0–––

1.64.0–––

4.1+5.7+

+++

2.9+3.7+

+++

2.7+3.6+

+++

FN I/Q

MLDBX/DIX

Detecting the negtive edge inthe RLO. The bit addressed inthe intruction is the auxiliaryedge bit memory.

2 2.6

3.84.26.8

0.9

1.61.72.2

1.0

1.61.74.1

3.8+

4.1+4.3+5.8+

2.9+

3.1+3.1+4.0+

2.6+

2.8+2.8+3.7+

[AR1,m][AR2,m]Parameter

–––

–––

+++

+++

+++

Status word for: FP, FN BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes –

Instruction affects: – – – – – 0 Yes Yes 1

1 Plus time required for loading the address of the instruction(see page 19)

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

6362

Setting/Resetting Bit Addresses

Assigning the value “1” or “0” or the RLO o the addressed instruc-tion. The instructions can be dependent on the MCR.

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Adressing Indirect Adressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

S I/Q

M

L

DBX/DIX

Set input/output to “1”(MCR-dependent)

Set bit memory to “1”(MCR-dependent)

Set local data bit to “1”(MCR-dependent)

Set data bit to “1”(MCR-dependent)

1 2/2

12/2

2

2

0.71.41.93.93.04.96.27.3

0.31.40.83.01.23.13.34.5

0.30.50.82.31.32.93.74.3

3.3+4.4+3.7+4.4+3.8+3.9+5.5+6.6+

2.2+3.4+2.4+3.6+2.4+3.6+3.3+4.4+

2.2+2.9+2.5+3.0+2.5+2.5+3.5+4.1+

[AR1,m][AR2,m]Parameter

Set I/Q/L/DBX/DIX to “1”(MCR-dependent) (addressedvia AR1/AR2 (area-crossing) orvia parameter)

2 –––

–––

–––

+++

+++

+++

Status word for: S BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes –

Instruction affects: – – – – – 0 Yes – 0

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

6564

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Adressing Indirect Adressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

R I/Q

M

L

DBX/DIX

Reset input/output to “0”(MCR-dependent)

Reset bit memory to “0”(MCR-dependent)

Reset local data bit to“ 0”(MCR-dependent)

Reset data bit to “0”(MCR-dependent)

1 2/2

1 2/2

2

2

1.01.42.24.13.05.16.47.3

0.41.40.93.11.23.23.54.6

0.40.50.92.41.33.03.84.3

3.5+4.6+3.8+4.6+4.0+4.1+5.7+6.7+

2.4+3.5+2.5+3.7+2.5+3.7+3.4+4.5+

2.3+3.0+2.6+3.2+2.6+2.7+3.6+4.3+

[AR1,m][AR2,m]Parameter

Set I/Q/L/DBX/DIX to “1”(MCR-dependent) (addressedvia AR1/AR2 (area-crossing) orvia parameter)

2 –––

–––

–––

+++

+++

+++

Status word for: R BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes –

Instruction affects: – – – – – 0 Yes – 0

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

6766

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Adressing Indirect Adressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

= I/Q

M

L

DBX/DIX

Assign RLO to input/output(MCR-dependent)

Assign RLO to bit memory(MCR-dependent)

Assign RLO to local data bit(MCR-dependent)

Assign RLO to data bit(MCR-dependent)

1 2/2

1 2/2

2

2

0.71.42.23.92.74.66.47.5

0.21.40.93.01.03.13.35.3

0.30.50.92.31.12.63.84.4

3.3+4.4+3.7+4.4+3.8+3.6+5.7+6.7+

2.2+3.4+2.4+3.6+2.4+3.6+3.3+5.3+

2.2+2.9+2.5+3.0+2.5+2.3+3.6+4.3+

[AR1,m][AR2,m]Parameter

Assign RLO to I/Q/M/L/DBX/DIX (via AR1, AR2 (area-crossing) or via parameter)

2 – – – + + +

Status word for: = BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes –

Instruction affects: – – – – – 0 Yes – 0

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

6968

Instructions Directly Affecting the RLO

The following instructions have a direct effect on the RLO.

In-struc-tion

AddressIdentifier

DescriptionLenght

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

CLR Set RLO to ”0” 1 0.7 0.2 0.3

Status word for: CLR BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – – –

Instruction affects: – – – – – 0 0 0 0

SET Set RLO to ”1” 1 0.7 0.2 0.3

Status word for: SET BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – – –

Instruction affects: – – – – – 0 1 1 0

NOT Negate RLO 1 0.7 0.2 0.3

Status word for: NOT BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – Yes – Yes –

Instruction affects: – – – – – – 1 Yes –

SAVE Save RLO to the BR bit 1 0.7 0.2 0.3

Status word for: SAVE BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes –

Instruction affects: Yes – – – – – – – –

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

7170

Timer Instructions

Starting or resetting a timer (addressed directly or via a parameter).The time value must be in ACCU1-L.

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Adressing Indirect Adressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

SP T Start timer as pulse on edgechange from“0” to “1”

1 2/2 14.0 8.4 9.2 14.3+ 8.8+ 9.7+

Timer para.

p gchange from “0” to “1”

2 – – – + + +

SE T Start timer as exded pulse onedge change from“0” to “1”

1 2/2 14.0 8.4 9.2 14.3+ 8.8+ 9.7+

Timer para.

pedge change from “0” to “1”

2 – – – + + +

SD T Start timer as ON delay on edgechange from“0” to “1”

1 2/2 14.7 9.0 9.7 15.0+ 9.4+ 10.2+

Timer para

y gchange from “0” to “1”

2 – – – + + +

SS T Start timer as retive ON delayon edge change from“0” to “1”

1 2/2 14.7 9.0 9.7 15.0+ 9.4+ 10.2+

Timer para.

yon edge change from “0” to “1”

2 – – – + + +

SF T Start timer as OFF delay onedge change from“1” to “0”

1 2/2 15.0 9.2 10.0 15.4+ 9.6+ 10.5+

Timer para.

yedge change from “1” to “0”

2 – – – + + +

Status word for: SP, SE, SD, SS, SF BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes –

Instruction affects: – – – – – 0 – – 0

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

7372

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Adressing Indirect Adressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

FR T Enable timer for restarting onedge change from “0” to “1”(

1 2/2 3.9 2.0 2.1 4.3+ 2.5+ 2.7+

Timer para.

edge change from 0 to 1(reset edge bit memory forstarting timer)

2 – – – + + +

R T Reset timer 1 2/2 3.5 1.8 1.8 3.8+ 2.2+ 2.4+

Timer para. 2 – – – + + +

Status word for: FR, R BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes –

Instruction affects: – – – – – 0 – – 0

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

7574

Counter Instructions

The count value is in ACCU1-L or in the address transferred asparameter.

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Adressing Indirect Adressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

S C Presetting of counter on edgechange from“0” to “1”

1 2/2 9.8 6.0 6.6 10.2+ 6.4+ 7.1+

Counter p.

g gchange from “0” to “1”

2 – – – + + +

R C Reset counter to “0” 1 2/2 3.4 1.7 1.8 3.8+ 2.2+ 2.3+

Counter p. 2 – – – + + +

CU C Increment counter by 1 on edgechange from“0” to “1”

1 2/2 4.8 2.6 2.8 5.2+ 3.1+ 3.4+

Counter p.

y gchange from “0” to “1”

2 – – – + + +

CD C Decrement counter by 1 onedge change from“0” to “1”

1 2/2 5.1 2.8 3.0 5.3+ 3.2+ 3.5+

Counter p.

yedge change from “0” to “1”

2 – – – + + +

FR C Enable counter on edge changefrom “0” to “1” (reset edge bit

1 2/2 4.0 2.1 2.2 4.3+ 2.5+ 2.7

Counter p.

from 0 to 1 (reset edge bitmemory for up and downcounting)

2 – – – + + +

Status word for: S, R, CU, CD, FR BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – Yes –

Instruction affects: – – – – – 0 – – 0

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

7776

Load Instructions

Loading address identifiers into ACCU1. The conts of ACCU1 andACCU2 are saved first. The status word is not affected.

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Adressing Indirect Adressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

LIBQBPIB

Load ...Input byteOutput bytePeripheral input byte

1 2/21 2/21 2/2

1.71.7

< 30/< 21 3

0.60.6

< 25/<533/< 884

0.60.6

< 24

2.7+2.7+< 40/< 30 3

2.2+2.2+26+/

<58 3/<92 4

1.7+1.7+< 27

MBLB

Bit memory byteLocal data byte

1 2/22

1.92.9

0.71.0

0.81.1

2.8+3.2+

2.2+2.2+

1.8+2.0+

DBBDIB

Data byteInstance data byte... into ACCU1

22

5.06.8

2.82.8

2.82.8

4.3+4.3+

2.8+2.8+

2.6+2.6+

Parameter Load IB/QB/PIB/MB/LB/DBB/DIB into ACCU1 (addressedvia parameter)

222

–––

–––

–––

+++

+++

+++

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing 3 Integrated digital I/O for CPU 312* and 314* 4 Integrated analog I/O for CPU 314*

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

7978

In- Length Typical Execution Time in �sInstruc-tion

AddressIdentifier

Description inWords Direct Adressing Indirect Adressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

LIWQWPIW

Load ...Input wordOutput wordPeripheral input word

1 2/21 2/21 2/2

2.42.4

< 40

0.80.8

< 29/<533/<884

0.90.9

< 30

2.9+2.9+< 46/< 30 3

2.1+2.1+< 30/<583/<924

1.9+1.9+< 32

MWLW

Bit memory wordLocal data word

1 2/22

2.73.0

1.01.1

1.11.3

3.2+3.7+

2.4+2.8+

2.1+2.3+

DBWDIW

Data wordInstance data word... into ACCU1

22

5.75.7

3.33.3

3.33.3

5.2+5.2+

3.7+3.7+

3.2+3.2+

Parameter Load IW/QW/PIW/MW/LW/DBW/DIW into ACCU1(addressed via parameter)

222

–––

–––

–––

+++

+++

+++

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing 3 Integrated digital I/O for CPU 312* and 314* 4 Integrated analog I/O for CPU 314*

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

8180

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Addressing Indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

LIDQDPID

Load ...Input double wordOutput double wordPeripheral double input word

1 2/21 2/21 2/2

2.92.9

< 45

0.90.9

< 37/<1903

1.11.1

< 40

3.2+3.2+< 65

2.4+2.4+< 39/<2003

2.1+2.1+< 42

MDLD

Bit memory double wordLocal data double word

1 2/22

3.43.7

1.41.5

1.51.6

3.7+4.2+

2.7+3.1+

2.5+2.7+

DBDDID

Data double wordInstance data double word... into ACCU1-L

22

7.07.0

4.44.4

4.34.3

6.5+6.5+

4.7+4.7+

4.2+4.2+

Parameter Load ID/QD/PID/MD/LD/DBD/DID into ACCU1(addressed via parameter)

222

–––

–––

–––

+++

+++

+++

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing3 Integrated analog I/O for CPU 314*

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

8382

In- Length Typical Execution Time in �sInstruc-tion

AddressIdentifier

Description inWords Direct Addressing Indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

L

B[AR1,m]B[AR2,m]W[AR1,m]

Load (area-crossing addressing)...Byte

Word

2

2

–

–

–

–

–

–

40.1+40.1+45.6+

38.2+38.2+43.1+

29.0+29.0+33.2+W[AR1,m]

W[AR2,m]D[AR1,m]D[AR2,m]

Word

Double word

... into ACCU1

2

2

–

–

–

–

–

–

45.6+45.6+57.4+57.4+

43.1+43.1+54.3+54.3+

33.2+33.2+43.0+43.0+

Lk8k16L#k32

Load ...8-bit constant into ACCU1-LL16-bit constant into ACCU1-L32-bit constant into ACCU1

123

1.71.72.0

0.60.60.7

0.60.60.8

–––

–––

–––

Parameter Load constant into ACCU1(addressed via parameter)

2 – – – + + +

L 2#n Load 16-bit binary constant intoACCU1-L

2 1.7 0.6 – – –

Load 32-bit binary constant intoACCU1

3 2.0 0.7 – – –

16#p Load 16-bit hexadecimalconstant into ACCU1-L

2 1.7 0.6 – – –

Load 32-bit hexadecimalconstant into ACCU1

3 2.0 0.7 – – –

1 Plus time required for loading the address of the instruction(see page 19)

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

8584

In- Length

struc-tion

AddressIdentifier

Description inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

L ’xx’ Load 2 characters 2 1.2 0.6 0.7

’xxxx’ Load 4 characters 3 1.4 0.7 0.88

L D# date Load IEC date (BCD) 2 1.2 0.6 0.8

L S5T# timevalue

Load S5 time constant (16 bits) 2 1.2 0.6 0.8

L TOD# timevalue

Load 32-bit time constantIEC time of day

3 1.4 0.7 0.88

L T# timevalue

Load 16-bit timer constant 2 1.2 0.6 0.88value

Load 32-bit timer constant 3 1.4 0.7 0.88

L C# countvalue

Load 16-bit counter constant 2 1.2 0.6 0.88

L P# bitpointer

Load bit pointer 3 1.4 0.7 0.88

L L# integer Load 32 bit integer constant 3 1.4 0.7 0.88

L q Load real number 3 1.4 0.7 0.88

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

8786

Load Instructions for Timers andCounters

Loading a time value or count value into ACCU1. The contents ofACCU1 are first saved to ACCU2. The bits of the status word arenot affected.

In- Length Typical Execution Time in �sInstruc-tion

AddressIdentifier

Description inWords Direct Addressing indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

L T Load time value 1 2/2 3.1 1.6 1.7 5.2+ 0.8+ 2.1+

Timer para. Load time value (addressed viaparameter)

2 – – – + + +

L C Load count value 1 2/2 2.9 1.6 1.5 5.2+ 0.8+ 2.1+

Counterpara.

Load count value (addressed viaparameter)

2 – – – + + +

LD T Load time value in BCD 1 2/2 8.1 5.4 5.4 15.6+ 4.6+ 5.9+

Timer para. Load time value in BCD(addressed via parameter)

2 – – – + + +

LD C Load count value in BCD 1 2/2 7.4 5.0 4.9 14.2+ 4.2+ 5.4+

Counterpara.

Load count value (addressed viaparameter)

2 – – – + + +

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

8988

Transfer Instructions

Transferring the contents of ACCU1 to the addressed Inrand. Thestatus word is not affected. Remember that some transfer instruc-tions depend on the MCR.

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Addressing indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

T

IB

QB

PQB

Transfer contents ofACCU1-LL to ...input byte

(MCR-dependent)output byte

(MCR-dependent)peripheral output byte

(MCR-dependent)

1 2/2

1 2/2

1 3/2

0.72.60.72.6

< 30

< 32

0.21.30.21.3

< 24/<404/<475

< 25/<414/<485

0.31.40.31.4

< 24

< 25

2.0+2.5+2.0+2.5+

< 35.5/< 19.2 4

< 36.5/< 20 4

1.6+2.0+1.6+2.0+

< 25+/< 45 4/< 50 5

< 26+/< 46 4

< 51 5

1.2+1.6+1.2+1.6+< 27

< 28

MB

LB

bit memory byte(MCR-dependent)

local data byte(MCR-dependent)

1 2/2

2

0.92.71.53.1

0.31.40.61.6

0.41.50.61.8

2.2+2.7+2.5+3.3+

1.6+2.0+1.7+1.5+

1.3+1.7+1.5+2.0

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing3 Direct addressing with PQB 0 to 2554 Integrated digital I/O for CPU 312* and 314*5 Integrated analog I/O for CPU 314*

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

9190

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Addressing indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

T DBB

DIB

data byte(MCR-dependent)

instance data byte(MCR-dependent)

2

2

4.65.44.65.4

2.42.82.42.8

2.53.02.53.0

3.9+4.7+3.9+4.7+

2.5+2.9+2.5+2.9+

2.3+2.8+2.3+2.8+

Parameter Transfer contents ofACCU1-LL to IB/QB/PQB/MB/LB/DBB/DIB (addressedvia parameter)

222

–––

–––

–––

+++

+++

+++

IW

QW

PQW

Transfer contents ofACCU1-L to ...input word

(MCR-dependent)output word

(MCR-dependent)peripheral output word

(MCR-dependent)

1 2/2

1 2/2

1 3/2

1.42.71.42.7

< 34

< 36

0.51.40.51.4

< 27/<42 4/< 50 5

< 28/<44 4/< 52 5

0.51.50.51.5

< 27

< 28

2.3+2.8+2.3+2.8+< 40

< 42

1.8+2.2+1.8+2.2+

< 29+/< 46 4/< 53 5

< 30+/< 48 4/< 55 5

1.5+1.8+1.5+1.8+< 31

< 32

MW

LW

bit memory word(MCR-dependent)

local data word(MCR-dependent)

1 2/2

2

1.73.02.03.4

0.81.60.81.7

0.81.80.92.0

2.7+3.2+3.0+3.8+

2.0+2.4+2.1+1.9+

1.7+2.1+1.8+2.3+

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing3 Direct addressing with PQW 0 to 2544 Integrated digital I/O for CPU 314*5 Integrated analog I/O for CPU 314*

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

9392

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Addressing indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

T DBW

DIW

data word(MCR-dependent)

instance data word(MCR-dependent)

2

2

5.26.15.26.1

3.03.43.03.4

3.03.53.03.5

4.7+5.6+4.7+5.6+

3.3+3.7+3.3+3.7+

2.9+3.4+2.9+3.4+

Parameter Transfer contents of ACCU1-Lto IW/QW/PQW/MW/LW/DBW/DIW (addressed viaparameter)

222

–––

–––

–––

+++

+++

+++

ID

QD

PQD

Transfer contents ofACCU1 to ...input double word

(MCR-dependent)output double word

(MCR-dependent)peripheral output double word

(MCR-dependent)

1 2/2

1 2/2

2

2.03.02.03.0

< 38< 39

0.71.70.71.7

< 31< 32

0.81.80.81.8

< 31< 32

2.7+3.2+2.7+3.2+< 42< 43

2.0+2.4+2.0+2.4+

< 32+< 35+

1.7+2.1+1.7+2.1+< 34< 35

MD

LD

bit memory double word(MCR-dependent)

local data double word(MCR-dependent)

1 2/2

2

2.73.73.04.1

1.22.01.22.2

1.32.31.42.6

3.3+3.8+5.3+6.2+

2.4+2.8+2.6+2.4+

2.2+2.6+3.0+3.5+

DBD

DID

data double word(MCR-dependent)

instance data double word(MCR-dependent)

2

2

6.77.66.77.6

4.14.54.14.5

4.14.64.14.6

6.2+7.1+6.2+7.1+

4.5+4.8+4.5+4.8+

4.0+4.5+4.0+4.5+

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

9594

In- Length Typical Execution Time in �sstruc-tion

AddressIdentifier

Description inWords Direct Addressing indirect Addressing 1

312*/313

314/314*

315/316/315-2

312*/313

314/314*

315/316/315-2

T Parameter Transfer contents of ACCU1 toID/QD/PQD/MD/LD/DBD/DID (addressed via parameter)

222

–––

–––

–––

+++

+++

+++

B[AR1,m] B[AR2,m]

W[AR1,m]W[AR2,m]D[AR1,m]D[AR2,m]

Transfer contents of ACCU1 tothe following with area-crossing addressingbyte

word

double word

2

2

2

–

–

–

–

–

–

–

–

–

37.3/20.8 2

37.3/20.8 2

40.240.245.945.9

38.7

38.7

43.043.045.245.2

29

29

32323535

1 Plus time required for loading the address of the instruction(see page 19)

2 With direct instruction addressing

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

9796

Load and Transfer Instructions forAddress Registers

Loading a double word from a memory area or register into AR1 orAR2.

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

LAR1–AR2DBDDIDmLDMD

Load contents from ...ACCU1Address register 2Data double wordInstance data double word32-bit constant as pointerLocal data double wordBit memory double word... into AR1

1122322

0.70.76.36.31.43.43.0

0.20.24.04.00.41.41.2

0.30.33.83.80.51.51.4

LAR2–DBDDIDmLDMD

Load contents from ...ACCU1Data double wordInstance data double word32-bit constant as pointerLocal data double wordBit memory double word... into AR2

122322

0.76.36.31.43.43.0

0.24.04.00.41.41.2

0.33.83.80.51.51.4

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

9998

Transferring a double word from AR1 or AR2 to a memory area orregister. The status word is not affected.

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

CAR1–AR2DBDDIDLDMD

Transfer contents of AR1 to ...ACCU1Address register 2Data double wordInstance data double wordLocal data double wordBit memory double word

112222

1.70.76.96.93.73.4

0.40.23.93.91.41.2

0.70.34.34.31.61.5

CAR2–DBDDIDLDMD

Transfer contents of AR2 to ...ACCU1Data double wordInstance data double wordLocal data double wordBit memory double word

12222

1.76.96.93.73.4

0.43.93.91.41.2

0.74.34.31.61.5

CAR – Exchange the contents of AR1and AR2

1 1.4 0.7 0.5

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

101100

Load and Transfer Instructions for theStatus Word

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

L STW Load status word 1 into ACCU1 2.4 1.4 1.5

Status word for: L STW BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: Yes Yes Yes Yes Yes 0 0 Yes 0

Instruction affects: – – – – – – – – –

T STW Transfer ACCU1 (bits 0 to 8) tothe status word1

2.2 1.5 1.4

Status word for: T STW BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – – –

Instruction affects: Yes Yes Yes Yes Yes – – Yes –

1 For the structure of the status word see page 13

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

103102

Load Instructions for DB Number andDB Length

Loading the number/length of a data block into ACCU1. The oldcontents of ACCU1 are saved to ACCU2. The condition code bitsare not affected.

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

L DBNO Load number of data block 1 5.1 3.1 3.3

L DINO Load number of instance datablock

1 5.1 3.1 3.3

L DBLG Load length of data block intobyte

1 1.7 0.6 0.6

L DILG Load length of instance datablock into byte

1 1.7 0.6 0.6

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

105104

Integer Math (16 Bits)

Math instructions on two 16-bit words. The result is in ACCU1 andACCU1-L, resp.

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

+I – Add 2 integers (16 bits)(ACCU1-L)=(ACCU1-L)+(ACCU2-L)

1 2.4 1.5 1.5

–I – Subtract 1 integer from another(16 bits)(ACCU1-L)=(ACCU2-L)–(ACCU1-L)

1 2.6 1.8 1.6

*I – Multiply 1 integer by another(16 bits)(ACCU1)=(ACCU2-L)*(ACCU1-L)

1 3.6 2.1 2.4

/I – Divide 1 integer by another(16 bits)(ACCU1-L)=(ACCU2-L):(ACCU1-L)The remainder is in ACCU1-H

1 5.0 3.2 3.4

Status word for: +I, –I,* I, /I BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – – –

Instruction affects: – Yes Yes Yes Yes – – – –

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

107106

Integer Math (32 Bits)

Math instructions on two 32-bit words. The result is in ACCU1.

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

+D – Add 2 integers (32 bits)(ACCU1)=(ACCU2)+(ACCU1)

1 3.1 1.8 2.0

–D – Subtract 1 integer from another(32 bits)(ACCU1)=(ACCU2)–(ACCU1)

1 4.0 2.3 2.7

*D – Multiply 1 integer by another(32 bits)(ACCU1)=(ACCU2)*(ACCU1)

1 13.5 8.2 9.9

/D – Divide 1 integer by another(32 bits)(ACCU1)=(ACCU2):(ACCU1)

1 14.8 6.5 10.8

MOD – Divide 1 integer by another(32 bits) and load the remainderinto ACCU1:(ACCU1)=remainder of[(ACCU2):(ACCU1)]

1 15.5 6.4 11.3

Status word for: +D, –D,*D, /D, MOD BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – – –

Instruction affects: – Yes Yes Yes Yes – – – –

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

109108

Floating-Point Math (32 Bits)

The result of the math instruction is in ACCU1. The execution timeof the instruction depends on the value to be calculated.

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

+R – Add 2 real numbers (32 bits)(ACCU1)=(ACCU2)+(ACCU1)

1 < 60 < 50 < 35

–R – Subtract 1 real number fromanother (32 bits)(ACCU1)=(ACCU2)–(ACCU1)

1 < 60 < 50 < 35

*R – Multiply 1 real number byanother (32 bits)(ACCU1)=(ACCU2)*(ACCU1)

1 < 60 < 50 < 35

/R – Divide 1 real number byanother (32 bits)(ACCU1)=(ACCU2):(ACCU1)

1 < 60 < 50 < 40

Status word for: +R, –R, *R, /R BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – – –

Instruction affects: – Yes Yes Yes Yes – – – –

NEGR – Negate the real number inACCU1

1 0.7 1.0 0.3

ABS – Form the absolute value of thereal number in ACCU1

1 0.7 0.4 0.3

Status word for: NEGR, ABS BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – – –

Instruction affects: – – – – – – – – –

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

111110

Square Root and Square Instructions(32 Bits)

The result of the instruction is in ACCU1. The instructions can beinterrupted.

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312* 313/314/314* 315/316/315-2

SQRT – Calculate the square root of areal number in ACCCUM1

1 – < 1000 < 1000

SQR – Form the square of a real num-ber in ACCU1

1 – < 300 < 300

Status word for: SQRT, SQR BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – – –

Instruction affects: – Yes Yes Yes Yes – – – –

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

112 113

Logarithmic Function (32 Bits)

The result of the logarithmic function is in ACCU1. The instruc-tions can be interrupted.

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312* 313/314/314* 315/316/315-2

LN – Form the natural logarithm of areal number in ACCU1

1 – < 650 < 650

EXP – Calculate the exponential valueof a real number in ACCU1 tothe base e (= 2.71828)

1 – < 1500 < 1500

Status word for: LN, EXP BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – – –

Instruction affects: – Yes Yes Yes Yes – – – –

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

114 115

Trigonometrical Functions (32 Bits)

The result of the instruction is in ACCU1. The instructions can beinterrupted.

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312* 313/314/314* 315/316/315-2

SIN – Calculate the sine of a realnumber

1 – < 900 < 900

ASIN – Calculate the arcsine of a realnumber

1 – < 2500 < 2500

COS – Calculate the cosine of a realnumber

1 – < 900 < 900

ACOS – Calculate the arccosine of a realnumber

1 – < 2500 < 2500

TAN – Calculate the tangent of a realnumber

1 – < 900 < 900

ATAN – Calculate the arctangent of areal number

1 – < 900 < 900

Status word for: SIN, ASIN, COS, ACOS, TAN, ATAN

BR CC 1 CC 0 OV OS OR STA RLO FC

Instruction depends on: – – – – – – – – –

Instruction affects: – Yes Yes Yes Yes – – – –

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

116 117

Adding Constants

Adding integer constants and storing the result in ACCU1. Thecondition code bits are not affected.

In-struc-tion

AddressIdentifier

DescriptionLength

inWords

Typical Execution Time in �s

312*/313 314/314* 315/316/315-2

+ i8 Add an 8-bit integer constant 1 0.7 0.2 0.3

+ i16 Add a 16-bit integer constant 2 0.7 0.2 0.3

+ i32 Add a 32-bit integer constant 3 1.5 0.4 0.6

List of Instructions List of Instructions

EWA 4NEB 710 6070-02b EWA 4NEB 710 6070-02bS7-300 Instruction List S7-300 Instruction List

119118

Adding Using Address Registers