pfcIE_jjgarcia

-

Upload

jonathan-arango -

Category

Documents

-

view

8 -

download

0

Transcript of pfcIE_jjgarcia

-

INGENIERA ELECTRNICA

PROYECTO FIN DE CARRERA

Sistema de Autenticacin Biomtrica de Huella Dactilar asistido por Interfaz de Voz para el Control de Accesos

AUTOR:D. JUAN JOS GARCA GARRIGS

DIRECTORES:D. CARLOS FERRER ZAERA

D. JESS SORET MEDEL

Tribunal:

Presidente: Vocal 1:

Vocal 2: Vocal 3:

CALIFICACIN: ................................. FECHA:

-

Indice

Resumen. V

Nota del Autor. VII

1. Introduccin. 1

1.1. Objetivos. . 1

1.2. Justificacin. 3

1.3. Metodologa. ... 5

2. Estudios Preliminares. 7

2.1. Introduccin a los Sistemas de Autenticacin Biomtrica de Huella Dactilar y Reconocimiento de Voz. 7

2.1.1. Autenticacin Biomtrica de Huella Dactilar. 7

2.1.2 Reconocimiento de Voz. . 12

2.2. Opciones de Integracin. Tecnologas de Autenticacin Biomtrica de Huella Dactilar y Reconocimiento de Voz. . 14

2.3. Seleccin de los Sistemas de Autenticacin Biomtrica de Huella Dactilar y Reconocimiento de Voz. . 17

3. Arquitectura. 25

3.1. Diseo Hardware del Dispositivo Controlador de Acceso. . 25

3.1.1. Microcontrolador del Sistema (mC) / Procesador de Voz. .. 27

3.1.2. Memoria de Programa y Datos del Sistema. 28

3.1.3. Mdulo de Autenticacin por Huella Dactilar. Comunicacin Interna y Externa. . 30

3.1.4. Compatibilidad entre Componentes Digitales. Niveles Lgicos. .. 37

3.1.5. Entrada y Salida de Audio. .. 41

3.1.6. Seales de Control de Puerta de Acceso. . 43

3.1.7. Alimentacin y Consumo de Corriente del Dispositivo. . 45

-

II

3.2. Infraestructura de la Red de Terminales de Control de Acceso Biomtrico. . 47

3.2.1. Capa Fsica de la Red. Protocolo RS-485. .. 47

3.2.2. Estructura y Caractersticas de la Red tCAB. . 48

4. Funcionamiento y Desarrollo Software. 57

4.1. Funcionamiento del Controlador de Acceso Biomtrico. 57

4.1.1. Funcionamiento Normal del Controlador de Acceso. .. 61

4.1.2. Configuracin del Controlador de Acceso. .. 66

4.2. Programa del Controlador de Acceso Biomtrico (Firmware). .. 78

4.2.1. Estructura y Archivos del Firmware. 78

4.2.2. Descripcin del Programa Principal. Flujogramas. .. 83

4.2.3. Protocolos de Comunicacin: Protocolo de Comandos del Mdulo de Autenticacin Biomtrica y Protocolo deEnlace de Red tCAB. . 102

4.2.4. Mapa de Memoria y Programacin del Dispositivo. . 123

4.3. Aplicacin de Gestin de la Red tCAB. ... 126

4.3.1. Dilogo de Autenticacin del Administrador por Huella Dactilar. 128

4.3.2. Panel Principal. .. 129

4.3.3. Dilogos Asociados a Operaciones sobre los Terminales. 137

4.3.4. Dilogos Asociados a Operaciones sobre los Usuarios. 140

4.3.5. Otras Ventanas de Dilogo. ... 144

5. Pruebas de Prototipos y Conclusiones. 147

5.1. Pruebas de los Prototipos del Controlador de Acceso. . 147

5.2. Pruebas de la Red tCAB. .. 153

5.3. Conclusiones. 154

Apndices

A. Bibliografa. 157

B. Diagrama de Bloques [Arquitectura]. 159

-

III

C. Interfaz de Usuario por Voz [VUI]. 161

C.1. Mensajes de Voz del Dispositivo tCAB. . 161

C.2. Vocabularios del Dispositivo tCAB. 165

-

VResumenEn este Proyecto de Ingeniera realizado para la empresa FermaxElectrnica S.A.E., se presenta el desarrollo de un sistema electrnicodigital para el control de accesos basado en la tecnologa de autenticacinbiomtrica de huella dactilar. Este sistema pretende facilitar el acceso ainmuebles de los usuarios, que, en lugar de las clsicas llaves u otros objetoscon la misma funcin, slo tendrn que desplazar su dedo sobre un lector dehuella dactilar para poder abrir la puerta, despus de su autenticacin comousuario autorizado. De este modo, tambin se incrementar la seguridad delacceso en muchos aspectos, al ser la huella dactilar mucho ms difcil deduplicar que otros objetos llave.

En una primera fase del proyecto, se dise un dispositivo controlador deacceso en el que se dispone de los modos de autenticacin de identificaciny verificacin del usuario mediante su huella dactilar, la cual ser capturadapor un lector de huella trmico por desplazamiento. En todo momento estedispositivo ejercer el control de la puerta de acceso, y en caso deautenticacin positiva de un usuario le permitir acceder al inmuebleabriendo la puerta. En la memoria del dispositivo habr capacidad para,aproximadamente, 1000 usuarios, los cuales registrarn sus huellas parapoder ser autenticados posteriormente. Esta operacin, al igual que la deborrar, o dar de baja al usuario, adems de otras opciones de configuracindel controlador de acceso, se podrn realizar gracias a un men de opcionesentre las que se encuentran las mencionadas, y que solamente ser accesiblepara la persona registrada como administrador del sistema. En consecuencia,el dispositivo podr funcionar de forma totalmente autnoma sin dependerde otro sistema externo para realizar dichas operaciones.

La interfaz de usuario del dispositivo, adems del lector de huella, estcompuesta por una Interfaz de Voz, consistente en la capacidad deldispositivo para reconocer comandos de voz a travs de un micrfono; y, unaltavoz que permitir al usuario escuchar mensajes de informacin eindicaciones de uso. Dicha interfaz de voz, desarrollada en castellano eingls, estar disponible, sobretodo, para navegar por el men deconfiguracin del dispositivo, aunque tambin ser til en el modo deverificacin de usuario por huella dactilar, donde se requiere al usuario queintroduzca su nmero de identificacin personal (PIN) pronunciando losnmeros que lo forman.

En la segunda fase del proyecto, se desarroll una red para controlar variaspuertas de acceso compuesta por estos dispositivos, ahora como terminalesde control de acceso biomtrico (tCAB), y que ser gestionada desde unaaplicacin sobre PC, mediante un protocolo de comunicaciones especfico.

-

VII

Nota del Autor

Debido a razones de Confidencialidad de la empresa Fermax ElectrnicaS.A.E., donde fue desarrollado este proyecto, en la memoria que se presentase han realizado los siguientes cambios u omisiones:

(i). Los Nombres Comerciales de algunos componentes deldispositivo diseado se han sustituido por nombres ficticios.

(ii). Se han omitido las referencias bibliogrficas correspondientes alos Datasheets de los componentes afectados por el punto (i).

(iii). No se han incluido en esta memoria, ni el Cdigo Fuente delSoftware desarrollado (Firmware del Dispositivo y Aplicacin deGestin de Red); ni, tampoco, el Esquema Elctrico(Esquemtico) correspondiente al diseo del dispositivo.

-

1 Captulo 1Introduccin

1.1. Objetivos.

En esta memoria se describe y detalla el proyecto de ingeniera en el que sedesarrolla e implementa una red de dispositivos para el control de acceso a inmuebles oestancias gestionada mediante una aplicacin sobre PC. Donde, cada dispositivocontrola independientemente el acceso mediante autenticacin biomtrica de huelladactilar y cuya interfaz de usuario, adems del lector de huella, consiste en elreconocimiento de comandos de voz independientes del locutor.

Para la realizacin del proyecto se propuso la consecucin de los siguientesobjetivos, enmarcados en tres fases:

En una primera fase de desarrollo se plantea el diseo y construccin delprototipo controlador de acceso. ste debe incorporar las siguientes funcionalidades:

Autenticacin biomtrica de usuario mediante lector de huella dactilar.

Control de la puerta de acceso: actuador (rel) abre-puertas, botn de salida,y sensor de deteccin de puerta abierta.

Interaccin con el usuario mediante mensajes de voz pre-grabados yreconocimiento de comandos de voz independientes de locutor que constituyanla interfaz de usuario del dispositivo.

Adems, cuando el dispositivo controlador no pertenezca a una red decontroladores de acceso, se pretende que funcione de forma totalmente autnoma,

-

2 Introduccin

sin necesidad de depender de un sistema central para su gestin. Por tanto, eldispositivo controlador debe disponer de un men de configuracin, que sea de fcilnavegacin y que proporcione al dispositivo la suficiente flexibilidad deconfiguracin para poder funcionar de forma independiente. Este men seraccesible slo para el administrador y sus opciones permitirn: aadir y borrarusuarios, cambiar el administrador y configurar los diferentes parmetros delsistema, como son los tiempos de control de puerta y la seleccin de modos defuncionamiento. La navegacin por este men de configuracin se realizar pormedio de la interfaz de voz que, gracias al reconocimiento de comandos de vozpermitir seleccionar las diferentes opciones del men y cuyos mensajes pre-grabados servirn de gua para el administrador.

Como segunda fase del proyecto se propone desarrollar la red de controladoresde acceso. sta ser de tipo centralizado, estar basada en el bus RS-485 y tendrcomo host central a un PC, donde se ejecutar la aplicacin de gestin de la red decontroladores. Para realizar dicha red y permitir la gestin de la misma, debedisearse un protocolo de comunicaciones especfico para este sistema eimplementarlo en el firmware del dispositivo controlador.

Conjuntamente, para completar el desarrollo del sistema de control de acceso, seplanea la realizacin de dicha aplicacin de gestin de la red de controladores. Parasu funcionamiento ser necesario un lector de huella, para PC, con el que recoger lashuellas dactilares de los usuarios, y en la que habr de implementarsefundamentalmente, una base de datos con todos los usuarios en cada dispositivo dela red y sus caractersticas (nmero de identificacin, nombre, patrones de huella ycontroladores en los que est autorizado); adems de las siguientes acciones:

Aadir y borrar usuarios en la base de datos de la aplicacin.

Autorizar y desautorizar el acceso de los mismos en cada controlador.

Configurar los diferentes parmetros de cada dispositivo controlador de lared.

La aplicacin, y por tanto la red de controladores de acceso, ser gestionadapor un grupo limitado de administradores del sistema de los que se almacenarntambin sus caractersticas incluyendo sus patrones de huella respectivos. Elacceso a la misma estar restringido a los administradores del sistema quedebern autenticarse antes de comenzar cada sesin de trabajo.

Por ltimo, en la tercera fase, se producir puesta en marcha del sistema decontrol de accesos, despus de haber construido los prototipos y descargado sufirmware. Este sistema consistir en una red integrada por al menos dos prototiposcontroladores, y estar gestionada por la aplicacin PC desarrollada. Conjuntamente,se verificar el funcionamiento, primero del prototipo y despus de la red,realizando los cambios en el hardware del sistema que sean necesarios, as como la

-

Introduccin 3

depuracin del programa del prototipo controlador de acceso y de la aplicacin degestin de la red.

1.2. Justificacin.

El presente proyecto se enmarca dentro de las actividades del Departamento deNuevas Tecnologas, cuyo director es el Dr. Carlos Ferrer Zaera, perteneciente a laempresa Fermax Electrnica S.A.E.; y supervisado por el Dr. Jess Soret Medel delDepartamento de Ingeniera Electrnica (ETSE) de la Universidad de Valencia. En elDpto. de Nuevas Tecnologas de Fermax nace el proyecto como una iniciativa paradesarrollar un nuevo sistema de control de accesos basado en tecnologa biomtrica dehuella dactilar, dentro de la lnea de producto ya existente y cuya responsabilidad recaedentro de este departamento.

Estado del Arte en Sistemas de Control de Accesos

Gracias al auge y madurez que ha alcanzado la tecnologa de reconocimiento dehuella dactilar, actualmente en el mercado estn empezado a aparecer dispositivos queaplican esta tecnologa biomtrica para autenticar usuarios en el acceso a inmuebles,viviendas u otras estancias. Estos sistemas presentan una mejora de seguridad ycomodidad frente a clsicos sistemas de control de accesos, como llaves y tarjetasmagnticas o dispositivos emisores de infrarrojos y radiofrecuencia, puesto que elusuario no se necesita ningn objeto llave o dispositivo externo que deba portar paraautenticarse y que, adems, pueda extraviar y ser utilizada por otras personas; digamosque el usuario lleva incorporado desde su nacimiento su propia llave, lo cual es labase de la autenticacin en todos los sistemas biomtricos y que evita los problemasmencionados anteriormente.

Respecto a otros sistemas que utilizan una interfaz de teclado numrico y una clavede usuario para su autenticacin, esta tecnologa al utilizar la identificacin de la huelladactilar del usuario no es imprescindible emplear una clave que deba ser memorizadapor el usuario por lo que es mucho ms cmodo para cualquier persona. Tambinincrementa la seguridad del acceso en cuanto a que la clave, usualmente de 4 dgitos ynica barrera para restringir el acceso, podra ser desvelada mediante muy diversosmtodos; mientras que el patrn de huella o la huella en si, requerira de medios muchoms sofisticados para ser reproducida y as violar la seguridad del acceso; adems,siempre se podra reforzar la seguridad con una clave de usuario lo que elevara an msel nivel de seguridad.

En este terreno existen ya algunos sistemas de autenticacin de huella dactilaraunque con caractersticas bastante limitadas. Por ejemplo, existen dispositivos decontrol de acceso que utilizan algn elemento externo y portable para su autenticacin,como tarjetas o llaveros magnticos en los que almacenan el patrn de huella delusuario. stos dispositivos realizan slo una verificacin de la huella introducida en el

-

4 Introduccin

lector con la huella del usuario almacenada en el elemento magntico. Tambin haydispositivos con una memoria interna donde almacenan los patrones de huella de losusuarios, y que realizan una verificacin de la huella del usuario capturada por el lectorcon la huella indicada mediante una clave de usuario o pin para autenticar su acceso. Enambos casos, estos sistemas utilizan slo la verificacin de la huella del usuario con unahuella almacenada, por lo que siempre se necesita algn mtodo extra depre-identificacin del usuario para poder realizar la autenticacin. La mayora de estossistemas actuales no realizan una identificacin de usuario, es decir que no realizan unabsqueda o verificacin 1:N en una base de datos de patrones de huella, debido a queello requiere de un mayor procesado y conlleva unos altos tiempos de respuesta que noson operativos.

Motivacin.

Dado el estado de los sistemas de control de accesos en el mercado actual, lamotivacin era desarrollar y construir un dispositivo de control de acceso utilizando unatecnologa de reconocimiento de huella dactilar que mejorase las prestaciones de lossistemas de control de accesos existentes en general, y de este modo facilitar el accesode cualquier persona a diferentes inmuebles, as como aumentar la seguridad en elacceso utilizando dicha autenticacin biomtrica.

Se pretenda disear un dispositivo verstil, dirigido tanto al acceso a edificiosvecinales, un solo acceso con muchos usuarios; como al acceso a estancias interiores deinmuebles o a diferentes zonas de un recinto industrial, que correspondera al caso deuna red de varios accesos, con capacidad tambin para muchos usuarios por acceso.Para ello, en la situacin de un solo acceso, el dispositivo debera poder funcionarautnomamente sin necesidad de instalar una red con un nodo central para gestionarla, yadems disponer de una base de datos grande para los patrones de huella de losusuarios, unido a una autenticacin de usuario que se pudiera realizar mediante elproceso de identificacin de huella dactilar en tiempos razonablemente pequeos yoperativos garantizando, adems, una elevada seguridad y fiabilidad en dicho proceso.ste no era el caso de los sistemas ya existentes que deban pertenecer necesariamente auna red o cuyo nmero de usuarios era muy limitado.

Para construir la red, en el caso de varios accesos, se pens en desarrollar unaaplicacin ejecutada sobre PC que gestionara la red, basada en RS-485, como host onodo central; pudiendo as escalar la red a las necesidades del entorno y dando aloperador o administrador del sistema una herramienta para su gestin, amigable y defcil uso. Esta escalabilidad del sistema completo, desde el caso de un dispositivoautnomo para el control de un acceso con una instalacin mnima, hasta la instalacinde una red de controladores para muchos accesos; dara una mayor salida al mercado delproducto, incrementando as su rentabilidad.

Dado el funcionamiento autnomo que el sistema deba poseer, se necesitaba unainterfaz de usuario con el dispositivo controlador adecuada, que permitiese realizar lasoperaciones fundamentales de alta y baja de usuarios, introducir claves auxiliares deacceso, y configurar diversos parmetros del sistema. Era necesario plantearse, por

-

Introduccin 5

tanto, cmo se iba a implementar el medio de interaccin con el usuario que, junto conel lector de huella, conformase dicha interfaz de usuario. Se pens en utilizar unainterfaz de comandos de voz, que sera posible implementar gracias a la tecnologa dereconocimiento de voz para sistemas embedded o embarcados que existe actualmente.Teniendo en cuenta la motivacin principal, para el desarrollo de este sistema de C.AA.,de mejorar la accesibilidad a inmuebles, adems de garantizar un control de accesoseguro, a cualquier persona; este tipo de interfaz de usuario presenta una gran facilidadde uso, en especial para usuarios invidentes, puesto que se establecen dilogosconsistentes en mensajes, que guan e indican al usuario en el manejo del dispositivo, ycomandos de voz para introducir datos, navegar por el men de configuracin, etc.

La interfaz de voz, a parte de suponer un ejemplo de empleo de esta nueva forma deinteraccin hombre-mquina, presentaba una ventaja adicional para su eleccin ennuestro dispositivo, como es la de construir un dispositivo ms compacto y modularpara su integracin en placas de calle de Fermax, debido a la simplificacin que resultade sustituir un teclado numrico ms pantalla LCD por dicha interfaz de voz.

1.3. Metodologa.

Para desarrollar este proyecto y conseguir los objetivos mencionadosanteriormente, se han realizado las siguientes tareas siguiendo la metodologa clsica dela ingeniera:

Estudio, valoracin y eleccin de los componentes principales del dispositivocontrolador, como son los elementos de proceso (micro-procesador/es), memoria einterfaz de usuario (lector de huella, micrfono, etc.) que permitan la gestin delsistema, as como la implementacin del reconocimiento de huella dactilar y decomandos de voz independiente del locutor. Y a su vez, definicin de laarquitectura, tanto del dispositivo controlador como de la red de control de accesos.

Inicio y desarrollo de modelos preliminares para la estructura del firmware deldispositivo controlador, y pruebas de stos sobre las plataformas hardware deevaluacin de los elementos proceso proporcionadas por los fabricantes.

Diseo hardware de la arquitectura de la placa madre del dispositivo controlador.

Diseo del firmware del sistema incluyendo el protocolo de comunicacionesnecesario para su funcionamiento en la red de dispositivos controladores gestionadadesde un PC.

Diseo CAD de la placa de circuito impreso (PCB) y construccin del prototipodel dispositivo controlador.

-

6 Introduccin

Ensayos de verificacin del prototipo trabajando en modo autnomo y en modode red, pruebas del protocolo de comunicaciones con el PC. Depuracin delfirmware del sistema y del protocolo de comunicaciones.

Desarrollo e implementacin de la aplicacin PC para la gestin de la red dedispositivos controladores de acceso.

Puesta en marcha de la red gestionada por la aplicacin desde el PC; pruebas yajustes finales del sistema completo.

-

7 Captulo 2Estudios Preliminares

En este captulo se explicarn las razones para la eleccin de los componentes oelementos principales y necesarios para el diseo e implementacin de nuestro sistemade control de acceso, descrito en el captulo anterior. En ste se emplean dos tipos detecnologas, como son la de autenticacin biomtrica de huella dactilar, elementofundamental de nuestro dispositivo de control de acceso; y la de reconocimiento de voz,que servir para implementar la interfaz de usuario mediante comandos de voz. Aqu sedetallarn tambin las caractersticas y parmetros tcnicos de ambas tecnologas, ascomo del microcontrolador del sistema y necesidades de memoria, lo que vertebrar laarquitectura del dispositivo controlador de acceso.

2.1. Introduccin a los Sistemas de Autenticacin Biomtrica deHuella Dactilar y Reconocimiento de Voz.

2.1.1 Autenticacin Biomtrica de Huella Dactilar [1] [2] [3].

Dentro del campo multidisciplinar del Reconocimiento de Formas destacan lasaplicaciones biomtricas que consisten en la medida, el procesamiento y anlisisestadstico de datos identificativos biolgicos de los seres humanos.

Un Sistema Biomtrico es esencialmente un sistema de reconocimiento de formasque reconoce a una persona mediante la autenticidad de caractersticas fisiolgicas y/ode comportamiento que posee. Un tema importante en el diseo de sistemas biomtricoses determinar cmo va a ser reconocida cada persona. Dependiendo del contexto de laaplicacin, o de las circunstancias de empleo, un sistema biomtrico puede tener dosmodos de operacin, como sistema de verificacin o de identificacin:

-

8 Estudios Preliminares

Un Sistema de Verificacin autentica la identidad de la persona comparandola caracterstica biomtrica capturada, con su propio patrn (o patrones)previamente almacenados en el sistema. ste realiza la comparacin uno auno (1:1) para determinar si la identidad declarada por la persona,normalmente mediante un nmero de identificacin personal o PIN, es cierta.El sistema de verificacin aceptar o rechazar esta afirmacin de identidadpara la que (Soy quien digo que soy?).

Un Sistema de Identificacin reconoce a una persona a travs de labsqueda en la base de datos de patrones de una coincidencia con el patrncapturado. ste realiza comparaciones uno a muchos (1:N) para establecer laidentidad del sujeto (o el resultado de la bsqueda es negativo si el sujeto noest registrado en la base de datos), en este caso, sin necesidad de que lapersona tenga que declarar su identidad previamente (Quin soy?).

El trmino Autenticacin es frecuentemente usado en el campo de estudio de

sistemas biomtricos, a menudo como sinnimo de verificacin; en realidad, enlenguaje de las Tecnologas de la Informacin, autenticar a un usuario significa dejar alsistema averiguar la identidad del usuario independientemente del modo (verificacin oidentificacin).

Todo lo dicho se aplica a cualquier sistema de autenticacin biomtrica por lo que esvlido, tambin, para un sistema biomtrico basado en la autenticacin por huelladactilar; el cual, es un caso particular de estos sistemas en el que las caractersticas ypatrones biomtricos se extraen de la huella dactilar de las personas, en lugar de otrascaractersticas biomtricas como son el rostro humano, en reconocimiento facial, el iriso retina, en reconocimiento ocular, o la forma de escribir en un teclado, como ejemplode reconocimiento de la dinmica de un determinado comportamiento humano.

En los diagramas de la figura 2.1 se muestran los procesos de los modos de

verificacin e identificacin de usuarios, as como, el proceso de registro de las huellasde un usuario en la base de datos del sistema, que siempre ser necesario para elfuncionamiento de un sistema basado en cualquiera de los dos modos de autenticacin.Aqu tambin se explican, brevemente, las tareas intermedias llevas a cabo en el interiordel sistema para implementar ambos modos de autenticacin.

Entendiendo que la huella dactilar, a causa de pliegues formados sobre la piel, estdibujada por una serie de lneas de cresta y de valle, la Representacin de la huellaconsiste en la eleccin o extraccin de unas determinadas caractersticas de este dibujode lneas, a partir de la imagen capturada por el lector y posteriormente digitalizada enescala de grises; para formar el patrn de huella con el que trabajar el sistema (procesorealizado en bloque Feature Extractor, ver fig. 2.1). Estas caractersticas deben serinvariantes en la huella del individuo, as como, localizables por el sistema para serextradas de la imagen de la huella con relativa facilidad. En lo que juega un papelcrucial la calidad de la imagen tomada por el lector, conjuntamente al pre-procesadoposterior de esta imagen.

-

Estudios Preliminares 9

Figura 2.1: Procesos de un Sistema de Autenticacin Biomtrica por HuellaDactilar. Los algoritmos de reconocimiento de huella dactilar implementan lastareas mostradas en gris: Feature Extractor, extraccin de caractersticas de lahuella dactilar para formar el patrn de huella; Matcher, comparacin estadsticadel patrn de huella capturada con el o los patrones de huella almacenados en labase de datos del sistema (DB); y, Quality Checker, valoracin de la calidad de lahuella dactilar capturada en el lector de huella.

Normalmente, los algoritmos de reconocimiento de huella basan la extraccin decaractersticas de la huella segn la posicin y orientacin relativa de unos puntosespeciales de sta llamados Minutiae o Minucias, tales como, terminacin ybifurcaciones de lneas de cresta (ver Fig. 2.2[a]), y Puntos Singulares con forma dedelta y de bucle (ver Fig. 2.2[b]); los cuales forman una Constelacin de puntos cuyas

-

10 Estudios Preliminares

coordenadas (posicin y orientacin) se almacenan en el patrn de huella (ver Fig. 2.3).Para mejorar los resultados de estos algoritmos basados en minucias (minutiae-basedapproach), y superar las dificultades que supone slo emplear la informacin local de lahuella proporcionada por dichos puntos, en el patrn de huella se incorporan tambincaractersticas globales de la huella como la forma exterior de la huella, orientacin delas lneas y frecuencia de aparicin de determinados puntos caractersticos; y seimplementan tcnicas de correlacin de estas caractersticas (correlation-basedapproach).

Figura 2.2[a]: Ejemplos de Minucias (Minutiae): Punto de Terminacin(izqda.), y, Punto de Bifurcacin (drcha.), de lneas de cresta.

Figura 2.2[b]: Ejemplos de Puntos Singulares de la huella: a) Bucle a izquierdas;b) Bucle a derechas; c) ncleo de la huella o espiral; d) arco; e) arco en tienda decampaa; los cuadrados denotan tipos de puntos singulares de Bucle, y lostringulos los de tipo Delta.

-

Estudios Preliminares 11

Figura 2.3: Ejemplo de Imagen de Huella Dactilar en la que se indican lasMinucias, y que forman la Constelacin del patrn de huella extrado de laimagen de huella capturada (izqda.). Comparacin de Constelaciones entre dosimgenes de huella dactilar (drcha.).

Debido a que el proceso de comparacin de patrones de huellas, en el bloque delsistema denominado Matcher, supone que nunca va a haber una coincidencia exactaentre patrones de huella como es natural, los algoritmos de comparacin de las huellasimplementados en el Matcher son de carcter estadstico para lo que se define unparmetro de puntuacin de la coincidencia, o Matching Score (parmetro probabilsticoen el rango [0..1]); entonces, si ste supera cierto umbral definido el sistema tomar ladecisin de aceptar la coincidencia entre patrones de huella resultando en unaautenticacin positiva del individuo.

Precisamente, por tratarse de un proceso de comparacin estocstico, como no puedeser de otra manera, nunca habr certeza en la coincidencia de huellas, es decir,Matching Score igual a 1. Esto significa, entonces, que el sistema cometer errores deautenticacin. En consecuencia, se definen unos parmetros, tambin de carcterprobabilstico, para especificar estos errores y por ello, tambin, la bondad delreconocimiento de huella ejecutado por un sistema en concreto. Los ms utilizadosprincipalmente en sistemas comerciales son: FAR (False Acceptance Rate), Tasa deFalsas Aceptaciones correspondiente a la probabilidad de autenticar o reconocerpositivamente la huella de un usuario que realmente no existe en la base de datos delsistema; y, FRR (False Rejection Rate), Tasa de Falsos Rechazos correspondiente a lasituacin inversa, en que no se autentica positivamente a un usuario cuyas huellas sestn registradas en el sistema.

A la vista de estas definiciones se puede comprender que el Nivel de Seguridad deun sistema de autenticacin positiva (aceptacin de un usuario que existe en la base dedatos y rechazo del que no existe) vendr determinado por el FAR. Entonces lo queinteresa en principio es disminuir el FAR (aumentar el nivel seguridad) lo ms posible;sin embargo, hay que tener en cuenta que, en consecuencia, se elevar el FRR al estar

-

12 Estudios Preliminares

inversamente relacionados, con lo que, si se aumenta demasiado el FAR, un elevadoFRR dificultar el uso del sistema al rechazar en exceso a usuarios autorizados.

2.1.2 Reconocimiento de Voz [1] [2] [4].

El Reconocimiento de Voz (Speech Recognition) consiste esencialmente en elproceso de interpretacin de una palabra(s) pronunciada por una persona, pertenecientea un conjunto determinado de palabras, despus de capturar la seal acstica quecorresponde a la pronunciacin de esta(s) palabra(s) a travs de un micrfono. Laspalabras interpretadas o reconocidas son los resultados finales del proceso dereconocimiento de voz, que pueden servir para iniciar diversas acciones en un sistema, apartir de la palabra reconocida como comando de voz; y, tambin, para introducir datose informacin que corresponda justamente a la palabra reconocida, por ejemplo, laintroduccin de nmeros en un sistema empleando las palabras del 0 al 9.

Los sistemas de reconocimiento de voz pueden ser caracterizados por muchosparmetros, algunos de los ms importantes son:

Modo del Habla: desde Palabras Aisladas (Isolated-Words) al HablaContinua (Continuous Speech).

Clasificacin del sistema en funcin del tipo de Locutor:

Dependiente de Locutor (Speaker-Dependent): los usuarios delsistema o locutores necesitan registrar su voz en el sistema para que laspalabras que pronuncie sean reconocidas.

Independiente de Locutor (Speaker-Independent): los usuarios delsistema o locutores puede ser cualquier persona que

Tamao del Vocabulario o Conjunto de Palabras Reconocidas: desdepequeos vocabularios (20.000 palabras).

Modelo Acstico o de Lenguaje: desde modelos provenientes del campode reconocimiento geomtrico de formas como por ejemplo, RedesNeuronales o Clasificadores basados en Mixturas de Gaussianas; a modelosbasados en el reconocimiento de formas sintctico como, Modelos deEstados Finitos (FSM) o Gramticas Sensibles al Contexto. Un modelo queno pertenece exclusivamente a ninguna de las disciplinas anteriores peromuy utilizado en sistemas de reconocimiento de voz son los ModelosOcultos de Markov (HMM). Estos modelos suelen ser de carcterestadstico y se pueden aplicar de forma general a diversas tareas dereconocimiento de formas, pero aplicados al reconocimiento de voz esdonde la mayora de ellos ha dado los mejores resultados hasta ahora.

-

Estudios Preliminares 13

Relacin Seal-Ruido (SNR): Alto (>30 dB) o Bajo (

-

14 Estudios Preliminares

Una vez el sistema ha sido entrenado para comprobar la eficacia del reconocedorde voz existen muchas tcnicas, de las cuales la esencia es realizar un test con un grupode personas con voces lo ms representativas posible (voces de hombres y mujeres, deedades diferentes) para que utilicen el sistema pronunciando el conjunto de palabras ofrases que el sistema est preparado para reconocer. Una vez finalizado el test seobtendr lo que se denomina habitualmente, Matriz de Confusiones, donde serepresentan las tasas de acierto y error de la siguiente manera, las filas de la matrizrepresentarn las palabras pronunciadas y las columnas las reconocidas por el sistema,de este modo, en cada posicin de la fila de una palabra pronunciada, se escribirn losporcentajes de la interpretacin dada por el sistema a esta palabra, por ejemplo, delconjunto de palabras {A, B ,C}, si se ha pronunciado B, entonces, se ha reconocido B(Acierto) un 90% de las veces pronunciada, y A o C (Errores) el resto de veces.

2.2. Opciones de Integracin. Tecnologas de AutenticacinBiomtrica de Huella Dactilar y Reconocimiento de Voz.

Se realiz una prospeccin del mercado para localizar y seleccionar loscomponentes necesarios para implementar tanto la tecnologa de autenticacinbiomtrica de huella dactilar como la de reconocimiento de voz en nuestro dispositivo.

Autenticacin Biomtrica de Huella Dactilar [5].

Respecto a esta primera tecnologa, existen en el mercado gran cantidad defabricantes que ofrecen sus dispositivos de autenticacin de huella dactilar comosoluciones cerradas y difcilmente embarcables en otro sistema, lo cual no nos interesapuesto que, buscamos componentes o mdulos que se puedan integrar en nuestrodispositivo como parte de l. Otros fabricantes disponen de soluciones abiertas conposibilidades de integracin de las partes fundamentales para implementar dichatecnologa, como son el sensor o lector de huella, y los elementos de proceso y memoriaque puedan llevar a cabo el anlisis o autenticacin de la huella del usuario mediante laejecucin de sus algoritmos de reconocimiento de huella dactilar.

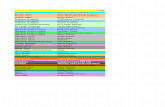

En primer lugar analizamos los diversos tipos de lectores de huella, mostrados en latabla 2.1, compatibles con la mayora de sistemas de autenticacin de huella ofertadospor los fabricantes. Debido a que en muchos casos nuestro dispositivo controladorestar expuesto a condiciones ambientales de exteriores, el lector de huella trmico deAtmel posee mejores caractersticas de robustez para soportar dichas condiciones.Adems, la forma de capturar la imagen de la huella dactilar de este tipo de lector, quese realiza como se explic en el punto anterior, trmicamente por las diferencias detemperatura entre valles y crestas de la huella; hace ms difcil la simulacin ofalsificacin de la huella en un intento de violar la seguridad del acceso.

-

Estudios Preliminares 15

Fabricante TipoAuthentec CapacitivoInfineon CapacitivoAtmel TrmicoBMF PresinTST ptico

Tabla 2.1: Fabricantes y tipos de lectores de huella dactilar.

Conjuntamente a la eleccin del lector, se evalan las diferentes soluciones paraembarcar esta tecnologa en nuestro sistema. Se diferencian fundamentalmente dosopciones, como ejemplo de la primera opcin tenemos a fabricantes como TexasInstruments que plantean la utilizacin de algoritmos y libreras software de terceraspartes para implementar las funciones de reconocimiento de huella. Entre otros destacanAuthentec con su tecnologa patentada TruePrint, IdentALink y, Neurodynamics conel software DEIXIS; dirigidos a plataformas DSP de las familias C5000 y C6000.Como parte de las herramientas de desarrollo software Texas Instruments disponeadems del entorno de desarrollo integrado (IDE) Code Composer Studio, y para eldesarrollo hardware, las terceras partes ofrecen placas o kits de evaluacin con su propiatecnologa, incluyendo diversos lectores de huella. La segunda opcin consiste en lautilizacin de un mdulo OEM (Original Equipment Manufacturer) en el que estnintegrados el procesador, elementos de memoria y la electrnica necesaria en una placade circuito impreso (PCB), que, habiendo programado el firmware que facilita elfabricante, realiza las funciones de autenticacin de huella dactilar de forma autnoma.El mdulo posee dos interfaces con el exterior, uno para conectar el lector de huella,compatible con varios tipos de lectores; y otro de comunicacin serie que, junto alprotocolo de comunicaciones implementado en su firmware, permite enviar comandosal mdulo para poder as configurar sus diferentes parmetros, y realizar en l lasoperaciones propias de su funcionamiento como sistema de autenticacin de huelladactilar. De entre los fabricantes de este tipo de mdulos y especializados en estatecnologa, merecen ser resaltados los mdulos BioFinger de Optimal, con sus seriesOFM1000, OFM2000 y OFM3000 que incorporan procesadores DSP ARM yBlackfin de Analog Devices; y los mdulos Biokey2002 de Idencom, y MV1200de Byoscript, ambos con procesadores DSP de la familia C5000 y C6000 de TexasInstruments. Todos ellos incluyen su propio firmware de autenticacin de huella dactilaradems de, ofrecer la posibilidad de elegir entre varios tipos de lectores de huellacompatibles con cada mdulo. Para testear las funciones de autenticacin del mdulo,estos fabricantes disponen tambin de placas de evaluacin y aplicaciones PC quepermiten gestionar el mdulo teniendo al PC como host externo, via el protocolo decomunicacin serie RS-232/485.

Reconocimiento de Voz [6].

Actualmente existe en el mercado bastante software para incorporar funcionalidadesde reconocimiento de voz en aplicaciones para PC, sin embargo, es ms difcil encontrareste tipo de software dirigido a sistemas embebidos (embedded systems). Dentro de los

-

16 Estudios Preliminares

fabricantes o desarrolladores de software de soluciones ASR (Automatic SpeechRecognition) para sistemas embebidos, Scansoft y Sand destacan por su altaespecializacin y madurez de su tecnologa, por lo que fueron los considerados paraaadir las capacidades de reconocimiento de voz o ASR a nuestro sistema.

Scansoft proporciona como parte del conjunto de soluciones de reconocimiento devoz, Speechworks, las libreras y motores ASR para sistemas embebidos:VoCon3200 Embedded Development System v2.0, y VoConSF v3.1; incluyendoadems herramientas de desarrollo software especficas. El paquete softwareVoCon3200, disponible en varios idiomas, posee un nivel bastante elevado decaractersticas de reconocimiento de voz, como son el reconocimiento independiente delocutor (speaker-independent) de comandos de voz para un amplio vocabulario; y,gracias a la posibilidad de crear gramticas, la capacidad de reconocimiento continuodel habla, es decir, de frases predeterminadas. Aunque este SDK (SoftwareDevelopment Kit) sean bastante modulares y escalables, principalmente va dirigido aplataformas hardware que dispongan de sistema operativo, en concreto a aplicacionesPC con sistema operativo Windows 2000/XP, y aplicaciones embebidas sobredispositivos portables PDA que incorporen WinCE 4.2 o superior. Una solucin mslimitada y ajustada a nuestras necesidades de reconocimiento de voz, es la deVoConSF v3.1, que proporciona libreras y un motor de ASR de pequea huella(small-footprint) adecuado para desarrollar aplicaciones sobre procesadores DSP de 16bits, como son los de la familia de Texas Instruments, TM320C54x, y el de AnalogDevices, Blackfin535. Incorpora, tambin para varios idiomas, las capacidades dereconocimiento de comandos independientes de locutor, con un vocabulario msreducido, y de reconocimiento continuo de dgitos (Continuous Digit Dialing). Lasolucin para la implementacin ASR de VoConSF est dirigida a una arquitectura desistema basada en un esquema de comunicacin serie entre procesadores Host-DSP,donde no es necesario que exista en la plataforma un sistema operativo sobre el que seejecute este software. El motor de reconocimiento de voz y las libreras necesarias pararealizar las tareas de reconocimiento de voz se implementarn en el DSP, mientras queun microcontrolador jugar el papel de Host, que, mediante un protocolo de mensajes,controlar las funciones de reconocimiento de voz en el DSP, adems de ejecutar en lel programa principal de sistema especfico de nuestra aplicacin.

Sand es un fabricante totalmente dedicado a la produccin de tecnologa dereconocimiento de voz y, de reproduccin y grabacin de audio, especializado ensistemas embebidos. Este fabricante dispone de varias lneas de chips con diferentesprestaciones, y con un coste por chip bastante econmico. Ofrecen soluciones segn lasnecesidades de la aplicacin a la que vayan dirigidos, incorporando capacidades dereconocimiento de comandos de voz, independientes de locutor (SI: SpeakerIndependent) y dependientes de locutor (SD: Speaker Dependent), de autenticacin deusuario por voz o verificacin de locutor (SV: Speaker Verification); as como,funciones de sntesis de mensajes de voz y msica. La lnea de chips que ms se adaptaa nuestros objetivos de diseo, para incorporar la interfaz de voz a nuestro sistema, sonlas de las series de procesadores RESCUE-3x y RESCUE-4x. En particular nos interesael procesador de la segunda serie, RESCUE-4128, el ms avanzado de todos, y que setrata de un procesador de seal mixto (DSP-like) con un ncleo microcontrolador depropsito general de 8 bits, dispone tambin de 24 lneas configurables E/S, e interfaz

-

Estudios Preliminares 17

para memoria de programa y datos externa no multiplexado, es decir, con lneas delectura/escritura y direccionamiento independientes. Construido como un SoC (System-on-Chip), en l se integran bloques hardware de procesamiento analgico y digitalespecficos para realizar las tareas de reconocimiento de voz, as como, de reproducciny grabacin de audio comprimido. Estas tareas se implementan gracias al conjunto delibreras Sand Speech 7, desarrolladas para operar estos bloques de hardwareespecfico y que incorporan todas las capacidades de reconocimiento de vozenumeradas anteriormente. Con relacin a la caracterstica de reconocimiento de vozindependiente de locutor, Sand provee al desarrollador de la herramienta software paraPC, QuickT2SI (Quick Text to Speaker Independent), fundamental para construir elconjunto de palabras o vocabulario de reconocimiento que permitir reconocer hasta unmximo de 20 palabras por conjunto activo, es decir que el sistema podr discernir entre20 comandos de voz simultneamente, pudindose utilizar varios conjuntos de palabrasactivados en diferentes momentos, segn las necesidades de la aplicacin y laslimitaciones de memoria existentes. Esta aplicacin es capaz de crear los vocabulariossin necesidad de utilizar muestras de entrenamiento de las palabras deseadas, como eshabitual en este tipo de tecnologa; en su lugar, emplea modelos fonticos estadsticosbasados en algoritmos de redes neuronales y modelos ocultos de Markov (HMM). Estopermite, simplemente a partir de introducir las palabras deseadas en formato de texto,producir el cdigo objeto, que ser enlazado posteriormente con el resto del programade sistema, necesario para que el RESCUE-4128 pueda responder a los comandos devoz.

2.3. Seleccin de los Sistemas de Autenticacin Biomtrica deHuella Dactilar y Reconocimiento de Voz.

Una vez descritas las caractersticas ms relevantes de los sistemas que seplantearon como opciones para incorporar las funciones de autenticacin biomtrica dehuella dactilar y de reconocimiento de voz en nuestro sistema, justificaremos en esteapartado nuestra eleccin particular. sta estuvo guiada principalmente por lasnecesidades de diseo y desarrollo del dispositivo controlador, al mismo tiempo que,por la valoracin de la calidad y coste de las soluciones propuestas anteriormente.

Despus de analizar las diferentes opciones se eligi la siguiente combinacin desoluciones con las que integrar ambas tecnologas como subsistemas de nuestraarquitectura, y de las que se presentan aqu sus principales propiedades:

Subsistema de Autenticacin por Huella Dactilar:

Mdulo Optimal BioFinger OFM3010-FC. Sensor trmico de desplazamiento compatible Atmel FingerChip.

-

18 Estudios Preliminares

Caractersticas hardware relevantes: Tensin de Alimentacin, VDD: 3.3V 0.3V, regulada internamente. Consumo de Corriente Tpico, ISupply: 50mA(idle); 120mA(identifying).

Rango de Temperatura de Operacin: 0C 70C. CPU: DSP Blackfin a 400 MHz.

Memoria Flash Interna : 1MB.

UART: Comunicacin Serie Asncrona con Host externo*, Puertos deTransmisin y Recepcin: H_RXD, H_TXD.* Puerto serie utilizado para controlar el funcionamiento del mdulo gracias alprotocolo de comandos implementado en su firmware.

8 Puertos Digitales E/S de Propsito General* (GPIO0-GPIO7).* Configurables para controlar los principales eventos del proceso de autenticacindirectamente, sin necesidad de utilizar el puerto serie y el protocolo de comandos.

2 Filas de Conectores de 15 pines through-hole en cada lado del mdulopara su montaje.

Especificaciones de autenticacin por huella dactilar: Tasa de Falsas Aceptaciones: FAR (False Acceptance Rate) < 0.001%.

Tasa de Falsos Rechazos: FRR (False Rejection Rate) < 0.01%.

Tiempo de Registro de Huella de Usuario: 850 ms.

Tiempo de Verificacin de Huella de Usuario: 850 ms.

Tiempo de Identificacin Promedio (1:1000)*: 990 ms;* Obtenido para una base de datos de 1000 patrones de huella. Este tiempo depende dela posicin de la huella a identificar en la base de datos y el tipo de lector de huellaempleado, por tanto este parmetro est promediado sobre estos factores. Tiempo deIdentificacin Promedio (1:1000) para el Lector Atmel FingerChip: 1101 ms.

Tamao de Patrn de Huella (Template): 256-384 Bytes.

Capacidad para Patrones de Huella: 1910 en 1MB.

Proteccin de los datos de huella dactilar mediante el algoritmo decifrado por bloques AES (Advanced Encryption Standard) de 256 bits.

N 1 en el mayor concurso internacional de evaluacin para tecnologasde autenticacin por huella dactilar, FVC2004.

Kit de evaluacin BioFingerEVK: Placa madre para acoplar el mdulo y,Aplicacin PC, BioFingerUI_V32, para configurar y testar su funcionamientova puerto serie.

Motor de reconocimiento de huella dactilar, BioFinger Engine OFR200SDK, para desarrollar aplicaciones sobre PC y proporcionado como librera deenlace dinmico (DLL: Dinamic Link Library).

-

Estudios Preliminares 19

Lector de huella ptico USB de Digent, incluyendo el controlador paraWindows de este dispositivo.

Subsistema de Reconocimiento de Voz. Microcontrolador (mC) de Sistema:

Speech Recognition Processor Sand RESCUE-4128*.* Procesador de Voz. Actuar, tambin, como mC de sistema del dispositivo controlador deacceso.

Caractersticas hardware relevantes: Tensin de Alimentacin, VDD: 3.3V (Mn: 2.4V; Mx: 3.6V).

Consumo de Corriente Tpico, ISupply: 12mA a 3V.

Rango de Temperatura de Operacin: -40C 85C. Ncleo Microcontrolador de 8-bits a 14.32 MHz*.

* Arquitectura y Conjunto de Instrucciones similar al mC 8051. Utiliza PLL internopara generar la frecuencia de funcionamiento a partir de un cristal de bajo coste de3.58MHz.

Memoria ROM programable por mscara: 128 KB.

Memoria RAM: 4.8 KB (256 Bytes para aplicacin de usuario).

Bus de Memoria Externo no multiplexado: Direcciones (A0-A19) de 20bits y Datos (D0-D7) de 8 bits. Permite direccionar memorias de hasta1MB entre dos espacios de memoria, de programa (como mximo128KB) y de datos.

5 Timers o Temporizadores Internos: 3 de Propsito General, Watchdogy Timer para realizar Multitarea.

24 Puertos E/S (P0.0-P0.7, P1.0-P1.7, P2.0-P2.7), configurables porprograma como salidas o entradas, con pull-up interno.

Programacin de 8 tipos de interrupciones, incluyendo 2 interrupcionesactivadas por flanco para demandas de eventos externos, y 4interrupciones activadas por final de cuenta de temporizadores internos(Timers Overflow).

Preamplificador y control automtico de ganancia, ms conversor ADC16-bits para entrada de micrfono, y conversor para salida de audioDAC 10-bits.

Empaquetamiento tipo LQFP de 100 pines (100LQFP).

Capacidades de reconocimiento de voz del firmware Sand Speech 7: Reconocimiento de Comandos de Voz Independientes (SI: Speaker

Independent)* y Dependientes (SD: Speaker Dependent)* de Locutor.

-

20 Estudios Preliminares

* SI: Conjunto activo, o reconocimiento simultneo, de 20 palabras. SD: Conjuntoactivo de 100 palabras. El nmero de conjuntos activos de ambas capacidades estlimitado nicamente por el tamao de memoria utilizado (interna o externa).

Escucha Continua de Voz (CL: Continuous Listening), para detectar yreconocer comandos o palabras de disparo (Trigger Words).

Verificacin Biomtrica de Usuario por Voz (SV: Speaker Verification)*.* Utiliza una palabra por usuario, el nmero de patrones de palabra almacenadosdependern del tamao de la memoria utilizada (10 palabras en memoria interna).

Sntesis de Audio de 3.7 a 7.8 Kbps, para generar mensajes de voz,efectos de sonido y msica MIDI.

Herramientas de desarrollo Hw/Sw: QuickT2SI: Aplicacin PC para componer el vocabulario de

reconocimiento de voz independiente de locutor (SI), sin necesidad demuestras de entrenamiento, slo a partir de texto*. * Genera el cdigo objeto del vocabulario para ser enlazado (linked) posteriormente conel programa principal de sistema.

QuickSynthesis 4: Aplicacin PC para sintetizar y comprimir mensajesde voz pregrabados (formato WAV y frecuencia de muestreo 22050Hz) *.* Genera el cdigo objeto de los mensajes de voz para ser enlazado (linked)posteriormente con el programa principal de sistema.

Entorno de Desarrollo Integrado para la familia RESCUE-4x de Sand,Project-SE IDE de Phyton, el paquete completo incluye: EnsambladorMCA-SE, Compilador C MCC-SE, Depurador (Debugger)/SimuladorPDS-SE, y Emulador en circuito PICE-SE.

Paquete de Evaluacin y Prototipado Hardware: Placa de Evaluacin delRESCUE-4128, con memorias RAM y ROM externas, micrfono, salidade audio mini-jack amplificada y conector DB-9 para comunicacin serieRS-232. Opcin de utilizar el emulador PICE-SE conectado a la placa deevaluacin, lo que permite una depuracin de cdigo cmoda y rpida,gracias a la descarga del programa desarrollado con Project-SE en lamemoria Flash del emulador, mediante conexin USB.

Los algoritmos y procesadores de voz de Sand han sido utilizados en eldiseo de productos, que incorporan tecnologas de reconocimiento de voz yaudio, de compaas lderes del mercado como son JVC, Sony, y Mitsubishientre otras.

Justificacin de la Eleccin.

Partiendo de las opciones para integrar primero la autenticacin biomtrica porhuella dactilar, que es el objetivo primordial del diseo del controlador de acceso, sedecidi seleccionar el mdulo de Optimal BioFinger OFM3010-FC con lector dehuella trmico de desplazamiento, del que se describieron sus cualidades fundamentales.

-

Estudios Preliminares 21

Frente a los otros mdulos OEM propuestos, y despus de probar el funcionamiento devarios de ellos, en placas de demostracin de fabricantes como Digent e Idencom; el deOptimal presentaba las mejores prestaciones de autenticacin por huella dactilaratendiendo a tasas de error, tiempos de respuesta y capacidad para patrones de huella,avaladas por el concurso internacional Fingerprint Verification Competition(FVC2004). Asimismo, pensando en la aplicacin PC para gestionar la red decontroladores, la solucin de Optimal incorporaba libreras para PC de su motor dereconocimiento de huella dactilar, ms un lector de huella ptico USB; de este modo, sepodran aadir y borrar huellas de usuario remotamente desde la aplicacin PC,actuando como host central de la red, a los terminales de control de acceso.

Respecto a la otra opcin planteada anteriormente, de utilizar un DSP de TexasInstruments en conjuncin con las libreras de reconocimiento de huella dactilarproporcionadas por sus terceras partes, resultaba menos interesante que la solucin deOptimal puesto que, supona un incremento sustancial del tiempo de desarrollo delhardware necesario para integrar esta tecnologa, no garantizndose una mejora de lasprestaciones de los algoritmos de reconocimiento de huella disponibles, y resultando enuna estimacin del coste parecido al del mdulo Optimal, despus de incluir el precio delos elementos fundamentales, la plataforma DSP, las licencias o royalties de lascompaas que suministran las libreras, y las herramientas de desarrollo software deTexas Instruments.

Debamos integrar tambin la tecnologa de reconocimiento de voz en nuestro

dispositivo, por tanto, aunque la solucin del mdulo Optimal fuera ms compacta quela propuesta del DSP de Texas Instruments con las libreras de autenticacin de huelladactilar, antes de tomar una decisin y descartarla, se analiz la posibilidad de utilizarlas libreras de reconocimiento de voz de Scansoft sobre la misma plataforma DSP, encontraposicin a la combinacin del procesador de voz RESCUE-4128 de Sand con elmdulo de Optimal.

La principal ventaja de la primera combinacin es que se podran implementarambas tecnologas en el mismo procesador, utilizando el software de reconocimiento devoz de Scansoft, VoConSF, el cual posee muy buenas prestaciones para sistemasembebidos, y que se ajusta a las necesidades de la interfaz de voz planeada para nuestrosistema. Sin embargo, una de las desventajas respecto a la opcin de Sand, fue que losmodelos acsticos para construir los vocabularios, en un determinado idioma, debanencargarse a Scansoft, lo que encareca la solucin tanto en coste, como en tiempo dedesarrollo. Por otra parte, Scansoft no dispona de la implementacin de estas librerassobre el DSP requerido, siendo necesario encargar, tambin, la adaptacin a estaplataforma. Adems, los costes de estas libreras se aadiran, junto al coste por DSP,directamente al precio por unidad final y no slo a los costes de desarrollo, puesto queScansoft impona royalties por diseo implementado. Lo que estaba en clara desventajacon la propuesta de Sand, en la que el precio por unidad del RESCUE-4128 era muchoms bajo que el de un DSP, y en el que ya se inclua el coste de las libreras.

Todo ello, y considerando que la arquitectura fundamental para las doscombinaciones resultaba en una configuracin de igual complejidad, dada por un DSPms un microcontrolador de sistema; la solucin de implementar las libreras de ambas

-

22 Estudios Preliminares

tecnologas en un DSP fue descartada frente a la propuesta del mdulo OptimalOFM3010-FC, que realizara las funciones de autenticacin por huella dactilar, y queestara controlado por el procesador de voz Sand RESCUE-4128, que aparte de realizarlas tareas de reconocimiento de voz necesarias para implementar nuestra interfaz deusuario por comandos de voz, actuara como microcontrolador de todo el sistema.Como ltima consideracin, comentar a favor del software VoConSF de Scansoft que,en principio, la eficiencia y prestaciones de reconocimiento de voz parecen ser mejoresque las del chip de Sand, sin embargo, para nuestros objetivos de diseo de la interfazde usuario por voz, ste posee unas cualidades de reconocimiento de vozsuficientemente adecuadas. Esto ltimo viene reafirmado por unas pruebas de campopara la evaluacin de la eficiencia de reconocimiento de voz del RESCUE-4128,realizadas para Fermax por el instituto de investigacin ITACA, perteneciente a laUniversidad Politcnica de Valencia. El test independiente realizado por el ITACA sellev a cabo para analizar la eficiencia en el reconocimiento de comandos de vozindependientes de locutor (SI: Speaker Independent), en concreto, se realiz un nmerosignificativo de pruebas, para distintos individuos, sobre los nmeros del 0 al 9 y unpequeo conjunto de palabras, en ambientes con diferentes niveles de ruido ambiental.Los resultados de ejecucin del test ofrecieron un nivel de aciertos o aceptacin de estoscomandos superior al 95%.

Configuracin Bsica de la Arquitectura del Dispositivo Controlador.

Una vez descritos los subsistemas fundamentales de nuestro dispositivo controladory justificada su eleccin, a modo de primera aproximacin a la arquitectura del sistema,y con motivo de explicar la eleccin, primordial por otra parte, de una memoria externapara el RESCUE-4128; exponemos aqu la configuracin bsica de nuestro sistema,previo a detallar su arquitectura y otras elecciones de diseo en el captulo siguiente.

As pues, la configuracin de los subsistemas en nuestro dispositivo quedar comose muestra en la figura 2.5. El mdulo OFM3010-FC de autenticacin por huelladactilar, conectado directamente al lector de huella trmico, se montar sobre la placamadre de nuestro dispositivo y dispondr de un puerto de comunicacin serie asncronaque le permitir recibir rdenes, gracias a su protocolo de comandos especfico, tantodel microcontrolador del sistema como del PC, como host externo. El microcontroladordel sistema ser el procesador RESCUE-4128, que tambin como subsistema dereconocimiento de voz independiente de locutor, y reproductor de mensajespregrabados, implementar la interfaz de usuario por voz del dispositivo. Como otrastareas esenciales, el procesador RESCUE-4128 realizar el control de puerta, por mediode las lneas externas dedicadas a tal efecto y, para las seales de: activacin del relabre-puerta, atencin de las solicitudes del botn de salida y del sensor de deteccin depuerta abierta; adems de, gestionar el funcionamiento del mdulo de autenticacin y lacomunicacin con el host externo del sistema, cuando ste pertenezca a una red dedispositivos controladores.

-

Estudios Preliminares 23

Figura 2.5: Configuracin bsica del dispositivo controlador de acceso.

Como se vio en las especificaciones listadas anteriormente el microcontroladorRESCUE-4128 dispone de memoria interna de programa, aunque sta es sloprogramable por mscara, bajo demanda al fabricante, y adems, no tiene capacidadpara los datos del vocabulario de comandos de voz u otros que podamos necesitar. Portanto, era necesario utilizar su bus de memoria externo para incluir en nuestro diseouna memoria externa de programa y datos. La eleccin del tipo de memoria, que debaser, por supuesto, no voltil y compatible con el bus externo no multiplexado, con lneasde direccionamiento y datos independientes, del microcontrolador; estuvofundamentada en la decisin de que fuese una memoria reprogramable en sistema, deesta forma, se podran realizar depuraciones o actualizaciones del firmware del sistemade forma rpida y cmoda, una vez construido el dispositivo, con su memoria instalada,y mediante algn programa de descarga desde PC.

Se eligi una memoria Flash PSD de STMicroelectronics, que cumpla nuestrosrequisitos de programacin en sistema o ISP (In-System Programming), gracias a supuerto serie de test y descarga, JTAG. Adems se vio que esta memoria dispona de dosbancos de memoria Flash (Flash Primaria: 256KB; Flash Secundaria: 32KB), lo que leproporcionaba una gran versatilidad y holgura suficiente para implementar el programade sistema, y poder alojar tambin las constantes y datos relacionados con losvocabularios de reconocimiento y mensajes de voz. Como otra caracterstica muydeseable, la memoria PSD tena una SRAM de 32KB adicional para nuestras variablesde programa, compensando as la limitacin de memoria RAM interna del

-

24 Estudios Preliminares

microcontrolador elegido. A continuacin se detallan las propiedades principales de lamemoria PSD particular seleccionada, incluido las herramientas necesarias para suconfiguracin y programacin:

Memoria de Programa y Datos para el Microcontrolador del Sistema [7]:

Memoria Flash PSD de STMicroelectronics : PSD854F2V-90J*.* Interfaz de bus de memoria configurable para diversos tipos de microcontroladores de 8bits, incluye el tipo de bus no multiplexado y es compatible con las seales de control dememoria externa del RESCUE-4128.

Caractersticas hardware relevantes: Tensin de Alimentacin, VCC: 3.3V 0.3V. Consumo de Corriente Tpico, ISupply: 10mA, slo en ciclos Write/Erase*.

* Para ciclos de lectura y stand-by el consumo es aproximadamente de 50A. Rango de Temperatura de Operacin: -40C 85C. Tiempo de Acceso a Lectura*: 90 ns.

* Menor de 135 ns, que es el tiempo de acceso a memoria externa mximo permitidopor el RESCUE-4128.

Dos bancos de Memoria Flash: Primaria de 256 KB (8 sectores 32KB),Secundaria de 32KB (4 sectores 8KB); y una SRAM de 32KB.

Los bancos de memoria Flash soportan hasta 100,000 ciclos deEscritura/Borrado (Write/Erase Cycles), y tienen garanta de 15 aos deretencin de datos.

Puerto Serie JTAG que permite la programacin ISP de todo el chip.

Empaquetamiento tipo PLCC de 52 pines (PLCC52).

Herramientas de desarrollo para la programacin de la memoria: PSDsoft Express 8.40: Aplicacin PC para realizar la programacin de la

memoria va JTAG. Para poder adaptar su interfaz del bus de memoriapara un determinado microcontrolador, esta herramienta permiteconfigurar los diversos puertos de la memoria gracias a la lgicaprogramable interna de la PSD, adems de generar ejemplos de cdigo Cde los drivers que debe emplear el programa de sistema para acceder a lamemoria. Se puede elegir el mtodo de programacin Flash, Data Pollingo Data Toggle.

FlashLINK de STMicroelectronics: Cable para PC DB-25 (PuertoParalelo) y programador JTAG para memorias PSD.

RLINK-ST de Raisonance: Cable USB ms programador JTAG paramemorias PSD.

-

25

Captulo 3Arquitectura

El objetivo de este captulo es describir el diseo de la arquitectura deldispositivo controlador de acceso, as como, de la infraestructura de la red formada porvarios de estos dispositivos, como terminales de control de acceso biomtrico (tCABs).

Partiendo de la configuracin bsica presentada en el apartado 2.3 del captuloanterior, pasamos a detallar la arquitectura completa de nuestro sistema de control deacceso. Como se estableci en los objetivos del proyecto, sta comprende el diseo de laarquitectura del dispositivo, perteneciente al desarrollo hardware establecido para laprimera fase del proyecto; y de la estructura de la red de controladores de acceso, quecorresponde a la parte de desarrollo hardware de la segunda fase.

3.1. Diseo Hardware del Dispositivo Controlador de Acceso.

Para empezar el diseo del esquema elctrico del dispositivo, se analizaron enprofundidad los recursos disponibles del microcontrolador elegido, para as poderseleccionar los componentes adecuados y disear el resto de la circuitera de la placabase. Para ello, aparte de la documentacin tcnica correspondiente al microcontrolador,nos servimos de las herramientas de desarrollo proporcionadas por el fabricante. Entrestas, disponamos de una placa de evaluacin conectada a un emulador para elmicrocontrolador, que en combinacin con el entorno de desarrollo software, nospermita descargar programas de prueba en el emulador para as, empleando losdiversos recursos implementados en la placa de evaluacin, ir familiarizndose tantocon las capacidades de la tecnologa de reconocimiento de voz, como con otrasfunciones de entrada/salida, comunicaciones serie, interrupciones, etc.

-

26 Arquitectura

En realidad, y gracias a estas herramientas de desarrollo, el diseo hardware deldispositivo se realiz paralelamente a la definicin del firmware de nuestro sistema, locual nos conceda la posibilidad de ir adaptando el firmware al diseo de la arquitecturade nuestro dispositivo y viceversa. Esta sinergia entre el desarrollo hardware y software,ms que inevitable, es provechosa para la optimizacin de ambos tipos de diseo, y seprodujo a lo largo de todo el desarrollo del sistema. Aunque, para estructurar y explicarcon mayor claridad el desarrollo de este proyecto, separemos la descripcin de laarquitectura de la definicin del software del sistema (Cap. 4).

Segn el funcionamiento y las capacidades que queremos que nuestro dispositivoposea, debemos disear las diferentes partes de la arquitectura que les den soporte.Seguidamente, se listan todas las partes estructurales, especificando su funcin, en lasque hemos dividido el diseo del esquema elctrico del controlador de acceso, paraluego explicar aspectos particulares y las diversas elecciones de diseo realizadas encada una de ellas. Tambin se presentar el esquema de interconexin de estas partes,representado en el diagrama de bloques del dispositivo, y al que nos referiremosfrecuentemente para explicar nuestro diseo.

Partes Estructurales de la Arquitectura del Controlador de Acceso:

Microcontrolador del Sistema (mC) / Procesador de Voz: estecomponente es el elemento principal de proceso, ejecutando el programa ofirmware del controlador de acceso. Como se explic anteriormente, al tratarsede un SoC de aplicacin especfica, dispone de un ncleo mC de propsitogeneral y puertos de E/S para implementar el control del sistema; adems de,bloques hardware dedicados exclusivamente a realizar las tareas de procesado devoz que se determinen en su firmware: reconocimiento de comandos de voz yreproduccin de mensajes pre-grabados.

Memoria de Programa y Datos: memoria PSD externa con puerto JTAGpara programacin en sistema ISP.

Mdulo de Autenticacin de Huella Dactilar. Comunicacin con HostInterno (C) y Externo (PC): el mdulo, junto al lector de huella, realizar lasoperaciones de autenticacin biomtrica, siempre comandado por elmicrocontrolador, como host interno, en su funcionamiento autnomo habitual;recibiendo, tambin, rdenes del host externo cuando pertenezca a una red decontroladores de acceso, para su gestin remota desde el PC.

Entrada y Salida de Audio: circuitos de acondicionamiento de la seal deaudio de entrada al procesador de voz, proveniente del micrfono; y, de la salidade audio del procesador de voz, dirigida a un altavoz. Imprescindibles paraconstruir la interfaz de voz del usuario, que le permitir interaccionar con eldispositivo mediante comandos y mensajes de voz.

Seales de Control de Puerta de Acceso: para actuar y controlar la aperturade la puerta de acceso dedicamos tres lneas del microcontrolador que realicen

-

Arquitectura 27

las siguientes tareas: activacin del rel abre-puerta, deteccin de pulsacin delbotn de salida y de disparo del sensor de puerta abierta. Alimentacin del Dispositivo: acondicionamiento y regulacin de la tensinde alimentacin externa utilizada, 12V DC, para obtener las tensiones de trabajode las redes elctricas y componentes del dispositivo.

Diagrama de Bloques de la Arquitectura del Controlador de Acceso:

[Apndice B].

3.1.1. Microcontrolador del Sistema (mC) / Procesador de Voz.

El circuito integrado del procesador de voz y microcontrolador del sistema trabaja auna tensin de 3.3V, con 7 pines de alimentacin, VDD, y 8 pines de tierra, GND, paradistribuir uniformemente el consumo de corriente en el interior chip.

Como se vio en las caractersticas expuestas en el captulo 2, el microcontroladornecesita un cristal oscilador externo de 3.58 MHz. Internamente, el chip posee un PLLque cuadruplica su frecuencia, para as conseguir la de trabajo del procesador de voz,14.32 MHz, cuando ejecute las funciones de reconocimiento de voz y reproduccin deaudio.

El pin de Reset o Reinicio del microcontrolador es activo por cero y est conectadoa la red de 3.3V a travs del pequeo circuito mostrado abajo (extrado del esquemaelctrico completo); de este modo, el sistema se resetear al apagarlo. La resistenciaelevada limitar el consumo innecesario por este pin, y el condensador mantendr elnivel de tensin para, en caso de fluctuaciones de la tensin de alimentacin, noprovocar un reseteo accidental del microcontrolador. Por otra parte, el diodo permitirsu rpida descarga cuando realmente se produzca la desconexin.

Figura 3.1: Detalle del circuito para el pin de Reset o Reinicio del mC.

-

28 Arquitectura

El resto de recursos del microcontrolador (ver fig. 3.2), que intervienen directamenteen el diseo electrnico del dispositivo controlador, se comentarn a la hora de describirlas otras partes de su arquitectura, enunciadas en el apartado anterior.

Pero antes, hay que destacar una caracterstica importante, y que afecta a lacomunicacin del microcontrolador con el mdulo. Este chip no dispone de una UARTespecfica para establecer la comunicacin serie con el mdulo, por tanto ser necesariodedicar 2 de los 24 puertos de propsito general para las lneas de recepcin, RXD, ytransmisin, TXD; e implementar mediante software la comunicacin serie delmicrocontrolador.

Figura 3.2: Diagrama de Bloques de la arquitectura interna y recursos delmC/Procesador de Voz.

3.1.2. Memoria de Programa y Datos del Sistema.

Recordemos que la interfaz para el bus de memoria externa que posee elmicrocontrolador es del tipo de bus no-multiplexado, debido a no compartir ninguna delas 20 lneas de direcciones (palabra de direccin de 20 bits, [A0-A19]), con ninguna delas 8 lneas de la palabra de datos de 8 bits ([D0-D7]). Adems, sta dispone de lneasde control de memoria externa, con sus correspondientes seales, activas por cero, deseleccin de memoria de programa ( PSEN ), de escritura ( WR ) y de lectura ( RD ); quepermitirn direccionar dos espacios de memoria independientes, de hasta 1 MB cadauno. Estos son, el espacio de memoria de programa, slo de lectura (Read-Only), y elespacio de memoria de datos, de lectura y escritura (Read/Write).

Como la memoria PSD est pensada para ser compatible con gran nmero demicrocontroladores de 8 bits, hay que adaptar su interfaz del bus de memoria al denuestro microcontrolador. Esto se puede hacer gracias al programa de configuracin ydescarga PSDsoft Express, que permite seleccionar las caractersticas concretas de lainterfaz de memoria del microcontrolador, pudiendo asignar sus lneas de

-

Arquitectura 29

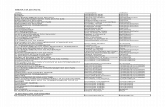

direccionamiento, datos y control a los puertos de la PSD (ver Tabla 3.1), as como,realizar la distribucin de los sectores de memoria, para ajustarse al mapa de memoriade nuestro microcontrolador. Posteriormente, los datos de configuracin de la memoriase descargarn, junto con el programa de sistema, en sus registros internos,implementndose la adaptacin de todo el chip de memoria por medio de lgicaprogramable: una PLD para los circuitos de decodificacin internos, y macroclulaspara los puertos de E/S (I/O Macrocells).

Lnea Bus Memo mC Puerto PSD[A0-A15](Direcciones) [ADIO0-ADIO15]

[A16, A17](Direcciones) [PB6, PB7][D0-D7](Datos) [PA0-PA7]

WR (Control) CNTL0

RD (Control) CNTL1

PSEN (Control) CNTL2

Tabla 3.1: Asignacin de Lneas del Bus de Memoria del mC a los puertos PSD.

En el apartado 4.2 correspondiente al desarrollo de nuestro firmware, y por estar msvinculado a ste, se describir el mapeado de los espacios de memoria de programa ydatos realizado en la PSD. Aunque, conviene comentar aqu que se eligi mapear elespacio de memoria de programa en el banco Flash primario de la PSD por ser el demayor tamao, 256 KB. Puesto que, en l se alojara el programa de sistema, as comolas constantes de programa, incluyendo las correspondientes a los vocabularios dereconocimiento de comandos de voz y mensajes de voz pre-grabados. Por lo tanto, delas 20 lneas de direccionamiento disponibles (hasta 1 MB), slo necesitamos 18(A0-A17) para direccionar los 256 KB (218 bits) de la memoria Flash primaria destinadaal espacio de memoria de programa, como se observa en el diagrama de bloques (ap. B).

Una de las razones principales de la eleccin de este tipo de memoria PSD fue lacapacidad de ISP o programacin en sistema, como ya se vio al final del captulo 2. Porconsiguiente, esta memoria dispone de una interfaz serie JTAG para realizar laprogramacin ISP, e implementado con las seales que se especifican en la tabla 3.2.

Seal JTAG(Puerto PSD) DescripcinTMS(PC0) Mode SelectTCK(PC1) Clock

TSTAT(PC3) Status

RR (PC4) Error FlagTDI(PC5) Serial Data InTDO(PC6) Serial Data Out

Tabla 3.2: Seales de los puertos JTAG de la memoria PSD.

-

30 Arquitectura

Las seales de entrada TMS, de seleccin de modo, y TCK, de temporizacin; juntoa las de entrada y salida de datos, TDI y TDO, respectivamente; corresponden al JTAGestndar definido por la norma IEEE 1149.1. Las seales de salida, TSTAT y RR ,sirven para comprobar el estado de la memoria durante su programacin, y son unaextensin aadida por el fabricante para incrementar la velocidad de descarga delprograma y los datos de configuracin a la PSD. El Pin-Out del conector para laprogramacin JTAG-ISP se muestra en la figura 3.3, como se puede ver aparte de lospines para seales opcionales no utilizadas, y las tomas de alimentacin, VCC, y detierra, GND, que son varias por motivos de reduccin EMI; tenemos un pin de Reset.ste es necesario para reiniciar la configuracin interna, borrar registros internos ysituar la PSD en el modo de operacin normal despus de la programacin. Por tanto,como se indica en el diagrama de bloques de la arquitectura, tenemos ah otra fuentepara la seal de Reset que hemos de conectar, tambin, al pin RESET delmicrocontrolador.

Figura 3.3: Detalle del conector JTAG-ISP utilizado, del tipo Molex Macho, ycompatible con los cables de programacin RLINK-ST (para USB) y FlashLINK(para Puerto Paralelo).

3.1.3. Mdulo de Autenticacin por Huella Dactilar. Comunicacin Internay Externa.

El mdulo de autenticacin por huella dactilar estar montado sobre la placa basemediante 2 tiras de 15 pines cada una, y estar alimentado a la tensin 3.3V de sutecnologa CMOS. Dispone de un lector de huella de tipo trmico por desplazamiento,conectado a ste por medio de un cable Flex. El lector de huella ser parteimprescindible de la interfaz de usuario del dispositivo, realizando la captura de laimagen trmica de la huella de usuario, para luego transferirla al mdulo, por medio delbus de datos contenido en el cable Flex.

-

Arquitectura 31

Para su funcionamiento, el mdulo siempre necesita de un host que le ordene lastareas de autenticacin por huella dactilar que debe realizar. Por ello, el mduloincorpora una UART (Universal Asynchronous Receiver Transmitter) que permitir lacomunicacin serie asncrona y bidireccional, a travs de sus puertos de recepcinMOD_RX, y transmisin MOD_TX.

En nuestro sistema queremos que tanto el microcontrolador, como host interno, y el

PC, como host externo, puedan adquirir el control del mdulo, y as, acceder a losdiferentes servicios que, va comunicacin serie, el mdulo de autenticacin puedaproporcionar. Por tanto, la configuracin para la intercomunicacin, en nuestrodispositivo, de estos tres elementos de proceso, se ciment en el establecimiento delmdulo como elemento o nodo central.

Para dar soporte a la comunicacin interna y externa con el mdulo, se dise elesquema de interconexin de los buses de comunicacin serie asncrona respectivos,como aparece representado en el diagrama de bloques (ap. B). Un poco ms adelante sedescribir en detalle su esquema elctrico, as como, la funcin de las lneas aadidaspara el control de la comunicacin, pero antes se expondr la estructura bsica deintercomunicacin (ver fig. 3.4).

Figura 3.4: Diagrama de interconexin de los buses de comunicacin serieasncrona con el Mdulo de Autenticacin, desde el Microcontrolador, como HostInterno; y desde el PC, que actuar como Host Externo por medio de las lneas derecepcin y transmisin externa, EXT_RX y EXT_TX.

El dispositivo controlador de acceso debe estar capacitado para establecer

comunicacin externa con el PC cuando pertenezca a una red de terminales de controlde acceso. La capa fsica de esta red estar basada en el protocolo serie RS-485, y el PCser el gestor o maestro de cada uno de ellos, comunicndose a travs del bus RS-485.Por ello, en el diseo de nuestro dispositivo se incorpor un transceptor o transceiver(ver diagrama de bloques, ap. B) para convertir las seales de este bus, provenientes delPC, a los niveles lgicos internos CMOS. Las caractersticas del transceiver, as comolas propiedades de la red se explicarn en el siguiente apartado cuando se describa la

-

32 Arquitectura

infraestructura de red. Por ahora, slo nos interesa saber que la comunicacin con el PCocurrir por medio de las lneas de recepcin y transmisin externa de datos, EXT_RXy EXT_TX, conectadas, respectivamente, a los puertos R (recepcin de datos del busRS-485) y D (transmisin de datos al bus RS-485) del transceiver CMOS(3.3V)/RS485.

Vemos en el diagrama de la figura 3.4, que el mdulo recibir datos por medio de

dos lneas: mC_TX, de transmisin de datos desde el host interno (mC); y, EXT_RX derecepcin externa de datos provenientes del host externo (PC). Pero, como ste slodispone de un puerto serie, ser obligatorio multiplexar estas lneas, que transmitirndatos al mdulo, para poder conectarlas a su puerto de recepcin de datos, MOD_RX.Vemos, tambin, que se podrn conectar directamente, al puerto MOD_TX, las lneas,mC_RX y EXT_TX, para la transmisin de datos desde el mdulo.

De esta forma, el microcontrolador se comunicara directamente con el mdulo,utilizando el protocolo de comandos definido en ste, para mandar la ejecucin de lasdiferentes acciones del proceso de autenticacin de usuario por huella dactilar,requeridas para el funcionamiento normal del dispositivo controlador de acceso.

Igualmente, se pens que el PC tambin deba tener comunicacin directa con elmdulo, actuando as como su host externo, puesto que, cuando nuestro dispositivopertenezca a la red de controladores de acceso, el PC gestor de la red, contendr lospatrones de huella de todos los usuarios siendo necesario realizar transferenciashabituales de estos patrones a la base de datos del mdulo, y as poder autorizar elacceso de los usuarios en cada terminal por medio de la autenticacin de huella dactilar.

Con esta configuracin, centrada en la comunicacin directa con el mdulo, nodispondremos de comunicacin directa entre el PC y el microcontrolador. sta, sinembargo, se podr establecer de forma indirecta utilizando el mdulo como retransmisorde la informacin dirigida al microcontrolador desde el PC, y viceversa.

Frente al bajo volumen de datos que se tena previsto intercambiasen elmicrocontrolador y el PC, principalmente para cambiar ciertos parmetros defuncionamiento del dispositivo, no compensaba la complicacin del esquema deinterconexin y del protocolo de comunicacin que supondra incorporar un nuevo bus,para establecer comunicacin directa entre el microcontrolador y el PC.

En consecuencia, se optimiz el esquema de intercomunicacin de nuestro sistema,

atendiendo a sus necesidades funcionales y, sin comprometer nunca la supervisin ycontrol que el microcontrolador deba ejercer en todo momento del proceso decomunicacin, implementado gracias a las lneas de control dedicadas a tal efecto, comose explica a continuacin.

El esquema de interconexin (fig. 3.5) se estructur por medio de puertas lgicasNAND, utilizando, en nuestro diseo, el mismo tipo de circuito integrado, 74HC00 dePhilips, compuesto por cuatro puertas NAND de tecnologa CMOS de alta velocidad(HC).

-

Arquitectura 33

Gracias al empleo de esta lgica, se realiz la multiplexacin de las lneas, mC_TXy EXT_RX, de transmisin de datos al puerto de recepcin, MOD_RX, del mdulo; ascomo, la incorporacin de las lneas CCOM e ICOM, del microcontrolador, yENA_TX, del mdulo, dedicadas al control y coordinacin de las comunicacionesexterna e interna del dispositivo.