Performed by:Elkin Aleksey and Savi Esacov Instructor: Idan Shmuel המעבדה למערכות...

-

Upload

randall-montgomery -

Category

Documents

-

view

229 -

download

0

description

Transcript of Performed by:Elkin Aleksey and Savi Esacov Instructor: Idan Shmuel המעבדה למערכות...

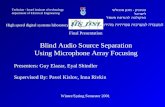

Performed by:Elkin Aleksey and Savi Esacov

Instructor: Idan Shmuel

High speed digital systems laboratoryהמעבדה למערכות ספרתיות מהירות

הטכניון - מכון טכנולוגי לישראל

הפקולטה להנדסת חשמל

Technion - Israel institute of technologydepartment of Electrical Engineering

דו”ח סיכום פרויקט חלק אSubject:

Encryption infrastructure on-key

2013/14חורף 1

AbstractHigh speed digital systems laboratoryהמעבדה למערכות ספרתיות מהירות

2

Separation of encryption mechanism and the control system will increase the system flexibility

• Allow to change the encryption mechanism according to the needs• Allow to make verification separate for each component• Allow to work on control system and encryption mechanism in same time

In this project we build a infrastructure for encryption system.It allow to connect between PC,FPGA and SD card. Project don’t include encryption core that may be embedded later

System descriptionHigh speed digital systems laboratoryהמעבדה למערכות ספרתיות מהירות

3

The system built from • Hardware

– DE2 Board– DLP– SD card

• Software– Quartus II 12.1– Qsys– Eclipse – Software control system– Matlab - GUI

SpecificationHigh speed digital systems laboratoryהמעבדה למערכות ספרתיות מהירות

• Hardware• DE2 board

• Cyclone II EP2C35F672C6 with EPCS16 16-Mbit serial configuration device • SD memory card slot• 18 toggle switches• 18 red LEDs• 9 green LEDs• Eight 7-segment displays• Built-in USB-Blaster for FPGA configuration• 50 MHz clock

• DLP• Interface between internal FIFO of FPGA and PC(via USB).• Data speed: 1 MB per second• SD card

• Using for data store• FAT16 file system• 1 GB Memory

4

SpecificationHigh speed digital systems laboratoryהמעבדה למערכות ספרתיות מהירות

• Software• Quartus II 12.1• Altera Quartus is a programmable logic device design software from Altera. Its

features include:• An implementation of VHDL for hardware description.• Visual edition of logic circuits.

• Qsys• The Qsys system integration tool saves significant time and effort in the FPGA

design process by automatically generating interconnect logic to connect intellectual property (IP) functions and subsystems

• Eclipse• integrated development environment (IDE) that contains a base workspace and

an extensible plug-in system for customizing the environment• Matlab – GUI

• multi-paradigm numerical computing environment used for GUI

4

System Block DiagramHigh speed digital systems laboratoryהמעבדה למערכות ספרתיות מהירות

5PC

DLP SD card

GUISending data to

encrypt Or decryption

request

NIOS IIsoftware controller

AVALON BUS

Controllerhardware

EncryptionEncryptionDecryptionDecryption(optional)(optional)

FPGA Block DiagramHigh speed digital systems laboratoryהמעבדה למערכות ספרתיות מהירות

6

FIFO IN8 bits (char)× 8192 Nios II/e

USB protocol(1 MB/s) STOP and WAIT

protocol(40 kB/s)

STOP and WAIT protocol(40 kB/s)

SD CardCTRL NIOS-SD CARD

SOFTWARE

FIFO OUT8 bits (char)× 8192

CTRL FIFO-NIOSHARDWARE

CTRL FIFO-NIOSHARDWARE

DLP

PC

DE2 BOARD

CTRL PC(DLB)-FIFOHARDWARE