平成31年度版 なごやっ子漢字検定プリント平成31年度版 なごやっ子漢字検定プリント 平成29年度版の 「カチッとコース」「スカッとコース」に、

最近のプリント基板で生じがちな...

Transcript of 最近のプリント基板で生じがちな...

The World Leader in High Performance Signal Processing Solutions

アナログ・デバイセズ株式会社

石井 聡

2014年12月13日

最近のプリント基板で生じがちな

トラブル対策に必要な知識

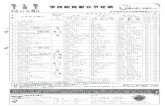

アジェンダ

1. 回路実現でトラブルを生じさせない「基本中の基本」

2. 最近注意すべきトラブル「基板上(層間)で生じる容量」

3. マイコン回路とAD変換でのトラブルで知っておくべき基礎技術

4. デジアナ混在基板で生じやすいトラブル 「結合」

5. 特性インピーダンスを理解して信号反射のトラブルを回避する

6. 信号反射によるトラブルのしくみと終端抵抗の重要性を理解する

7. 信号反射がアナログ信号伝送に与えるトラブルのしくみ

8. より高度な差動信号伝送における信号反射のようすと終端抵抗

の必要性を理解する

2

デジタルICの入力レベル(スレッショルド)を確実にする(異電源のケースが増えている)

4

VCC

3.3V

信号の振幅

GND

VOL

VOH

VCC 5V

VIL

VIH

Lと認識

する範囲

Hと認識

する範囲

通常の5VCMOS TTL互換5VCMOS

(74HCT)

Lと認識

する範囲

Hと認識

する範囲

これだけ

マージン

がある

3.3V CMOS

接続

ICのスレッショルドの例(高 ⇒ 低へのI/F)

7

5Vトレラント入力

TC7WZ04FU vccまででは無い

スレッショルドは電源依存(問題ないが)

5V⇒3.3VのI/Fができる

チャタリングが生じないようにする(ヒステリシス入力の活用)ダラダラ信号にも有効

8

0V

0V

5V

5V

3Vで切替

入力

出力

時間

時間

74HC14ヒステリシス特性

ICによって電圧は異なる

スイッチでチャタリングが発生しているようす(100us/Div)

CRとヒステリシス入力IC

(74HC14)でチャタリングを防止したようす(マイコンでソ

フトでもできる) CRでフィルタ

入力がダラダラ変化する信号にも有効

ヒステリシス入力

バイパス・コンデンサ(デカップリング)の必要性

電源とICまでのパターンが理想的であればいいが・・・

9

+端子

‐端子

アンプ アンプ

抵抗ゼロのパターン

出力抵抗ゼロの電源 電源電圧の変動を抑える

(高周波をコンデンサが分担する)

電圧変動が減尐

(高周波をコンデンサが分担する) 電源電圧が変動する

(高周波成分がやっかい)

電源電圧は

変動しない

複数の並列コンデンサで高い周波数まで対応できる

1 × 330µF T520、1 × 1.0µF 1608、2 × 0.1µF 1608、6 × 0.01µF 1608

2個づつ (1 × 330µF T520、1 × 1.0µF 1608、2 × 0.1µF 1608、6 × 0.01µF 1608)

※T520はKemet社の高分子タンタル・コンデンサ

コンデンサありなしでのプリント基板インピーダンス

10

Cなし

C1重

C2重

基板上で予期しない容量が生じる

13 P板.comサイトより転載

L1 -L2間は0.2mmしかな

い!(もっと狭い場合もある!)

𝐶 = 𝜀𝑟𝜀0𝑆

𝑑

L1に1cm SQなら (L2がベタで)

S = 1cmSQ, d = 0.2mm, εr = 4.7とすると

20.8pF!

アナログ回路では周波数特性が劣化する

1/√2(-3dB ) は8MHz

-45°

-3dBの周波数は1/(2πCR) 以降は周波数が2倍で1/2(-6dB )で低下

15

出力の電圧の大きさ(低減度)

出力の位相(波形の遅れ)

マイコン内蔵AD変換器の入力構造

RENESAS RX62N/RX621グループ ユーザーズマニュアル ハードウェア編

より抜粋

最大6.0pF

最大6.5kΩ

18

容量を高速で 充電する必要あり

12ビットADC AD7476A

Analog Devices AD7476A/7A/8A Datasheet より抜粋

より分解能の高い16/18/24ビット などがあるが難易度が高い

非線形性誤差に相当

絶対精度誤差に相当

19

AD7476Aには駆動アンプが必要

Analog Devices AD7476A/7A/8A Datasheet より抜粋

AD7476Aに推奨される駆動用アンプ

21

この時間でコンデンサに充電する必要あり (「デジタル回路では立ち上がりが鈍る」の話と同じ)

サンプリングによる「折り返し」の問題

サンプリング周波数

fs = 8kHz

ナイキスト

周波数範囲

ナイキスト周波数

fs/2 = 4kHz

本来の信号周波数

f = 6kHz

AD変換結果の周波数

f = 2kHz

周波数

振幅

対策はローパス・フィルタで 折り返し(エイリアシング) になる成分を除去する

(なお、DACでも同様に生じる)

23

24

AD7476AでのAD変換回路例

ここに信号源を入れる(0Vか5Vギリ

ギリは好ましくない。またLPFは図示していない)

電源 6V~10V

マイコン I2C

ADA4528-1を入力容量のドライバに用いている AD4528-1は+5Vで動作し、 オフセット電圧が2.5uV max 入力換算ノイズが5.6nV/√Hz

入出力レールtoレール(ギリギリまで動く) という超高性能OPアンプ(なのでここで用いた)

マイコンとの間の

信号の暴れを軽減

24

周辺からの目に見えない影響(静電容量による結合)

27

部品面

半田面

もしくは

内層

ここに

電圧が

加わると

容量で

結合する

(コンデンサ)

ここに電圧が

発生する

容量で

結合する

交流電圧

が加わった

金属体など

グラウンド

静電容量による結合をレイアウトで低減

部品面

半田面

もしくは

内層

ここには結合

しない

グラウンド

パターンを

挟む

ここに

電圧が

加わると

グラウンドに

落した内層

ここに電流

が流れていく

ここに電流が流れていく

28

周辺からの目に見えない影響(電磁誘導による結合)

29

電圧が

加わり

ここに電流が流れると

ここに電圧が発生する

磁束が

発生

ここに電流が発生する

ここに電流が流れると

磁束が

発生

対策は面積を狭くする、離す、 電流量を減らす

どんな結合が考えられるか?(こたえ)

【電磁誘導による結合】

【容量による結合】

このふたつで想定外のところで(浮遊成分として)結合が生じ、回路の性能劣化の原因になる

電磁誘導

容量

31

まずは「基本中の基本」をおさえておこう!

基板上で生じる容量により高速な回路でトラブルが生じる

後半の特性インピーダンスの考え方もポイント

AD変換は連続量が離散量(数値)に変換される特異点がある

サンプリングのときに容量を十分に充電すること

デジアナ混在基板では「結合」に注意する

アナログ側が影響を受けるほう

対策の基本は「分離」する

32

前半のまとめ

1V/Div

2V/Div

本来あるべきHレベル

信号

遷移点

伝達往復時間で先端(レシーバIC)の未整合による反射が観測

されている (このときドライバIC側で再反射している)

ドライバIC側で再反射したものが再度、伝達往復時間で、先端(レシーバIC)の未整合の再々反射が観測されている

高速信号伝送のトラブルの例(拡大図)

35

特性インピーダンス(伝送線路)を理解する必要性

特性インピーダンスの考えが活用されていないのでトラブルが生じていた

回路設計・仕様がどんどんハイスピード化している 高周波回路は当然ながら同軸ケーブルなど伝送線路をもちいる

高速デジタル回路も・・・

シリアルATA, IEEE-1394, USB 2.0

CPUバスラインなどなど

プリント基板上やリード線内の電圧や電流のうごきを伝送線路(特性インピーダンス)として考える必要あり

100MHz

500MHz

3GHz

36

ハイスピード信号伝送回路(伝送線路)の例

同軸ケーブル

高速デジタル信号のプリント基板 (最近は「インピーダンス・コントロール 基板」というものを使うことも多い)

イーサネット・ケーブル 高周波回路(マイクロ・ ストリップ・ライン)

37

USB 2.0の回路例 (480Mbps)

ターミネータ ターミネータ

ハイスピード信号伝送(より高度な差動信号伝送)

シリアルATA, IEEE1394, USB 2.0, LVDSなどは差動信号伝送

ここでも「ターミネータ」という言葉があるが、これが特性インピー

ダンスと深く関係している

38

でも 特性インピーダンス

っていったい ナニモノ?

0 2 4 6 8 10-15

-10

-5

0

5

10

15

電圧

[V

]

同軸ケーブル上の位置 [m]

f=50MHz。波長 は4mになる。 位相速度が2×108m/sのため、波長は6mでは無い

0.2m@1nsだけ進んでいる 位相速度2×108m/sで負荷

側に進んでいる。電流も同じ

特性インピーダンスは・・・ 波として移動していく電圧と電流 との相互関係 中に抵抗があるわけではない

デジタル信号も波として移動

負荷抵抗

周波数50MHz 1nsごとに表示している 位相速度というものがあり、光速ではない ここでは2×108m/s(一般に使われる同軸ケー ブルでの位相速度)

電圧や電流は伝送線路内を波として移動していく

39

信号が伝わるのはロープ上を波が伝わるのと同じ

40

イメージ実験をしてみましょう ①

② ロープをひと振りして波が伝わるようす(パルス・デジタル信号)を確認します

① ロープを繰り返し振り、波が伝わるようす(連続波)を確認します

③ ①および②から電気信号の伝わるようすを思い描いてみてください

0 2 4 6 8 10-15

-10

-5

0

5

10

15

電圧

[V

]

同軸ケーブル上の位置 [m]

0 2 4 6 8 10-0.4

-0.2

0

0.2

0.4

電流

[A

]

同軸ケーブル上の位置 [m]

実効値 10V

実効値 0.2A

全ての位置で「電圧/電流=50Ω」 の関係が成立している

位相速度2×108m/s

位相速度2×108m/s

波として移動していく電圧と電流との相互関係が特性インピーダンス 内部に50Ωの抵抗成分があるわけではない

この図は周波数50MHz 横軸は位置[m]です!

10V, 0.2Aが伝わっていくのが特性インピーダンス50Ω

41

42

P板.com インピーダンス・コントロール基板の設計パラメータ

目的のパターン幅とギャップを対象配線に適用(以下で計算) http://www.mantaro.com/resources/impedance_calculator.htm

http://www.skottanselektronik.com/

http://www.polarinstruments.com/jp/

特性インピーダンスラインにアパーチャ(Dコード)を設定

別途指示書に特性インピーダンスの指定値を記載

指示例 L8のアパーチャD302のパターンを差動100Ωでインピーダンス制御

*Zdiff L8,100ohm,on D302,L/S=0.15/0.15mm

※L/Sとは、パターン幅(L)と間隔(S)を指す

メーカ・材質に

よって異なる!

プリント基板の

絶縁体(誘電体)

ベタパターン

信号伝送 パターン

W

H

特性インピーダンスはWと

Hと誘電率で決まる

負荷抵抗が特性インピーダンスと異なると電圧と電流が反射する

信号源

進む波 進む波

反射して 戻る波

(たとえば10V)

(たとえば0.2A)

(たとえば10V×0.41)

(たとえば0.2A×0.41)

デジタル信号も波として移動

デジタル信号も波として反射

45

たとえばRL=120Ω

信号の反射をロープ上を波が伝わるので実験してみる

46

イメージ実験をしてみましょう ②

② ロープをひと振りして波が伝わるようす(パルス・デジタル信号)と反射してくるようすを確認します

① ロープを繰り返し振り、波が伝わるようす(連続波)と反射してくるようすを確認します

③ ①および②から電気信号の反射するようすを思い描いてみてください

反射する比率「反射係数」

信号源

進む波 進む波

反射して 戻る波

進む波と反射する波の 比率は電流、電圧ともども

(たとえば10V)

(たとえば0.2A)

(たとえばRL=120Ωなら0.41)

(たとえば10V×0.41)

(たとえば0.2A×0.41)

デジタル信号は波として移動

デジタル信号は波として反射 これが

「反射係数」

「ミスマッチ」状態 47

反射して 戻る波

本来は負荷端(遠端)で終端する

48

進む波 進む波

反射 なし

信号源

負荷端 反射してこない Γ = 0

整合終端 同軸ケーブルで説明しているが基板のパターンも同じ

信号源 近端

負荷 遠端

進む波

反射して 戻る波

進む波

反射して 戻る波

またまた反射して 進む波

またまた反射して 進む波

反射して戻る波 終端時(本来の)信号源波形

負荷端 (遠端波形)

最後は

に落ち着く

信号源のインピーダンスも異なっていると、反射して戻ってきた信号が

またそこでも再反射してしまう(多重反射)

49

デジタル信号での多重反射

基本は近端と遠端を終端

信号源50Ω、負荷50Ω

デジタル回路での多重反射のようす

5Vを送って5Vを受けるCMOSデジタルではどう対策する?

ひとつが「近端終端(信号源に50Ω)」という技

「近端終端」で近端に戻ってきたとき再反射が無い

シミュレーションで終端と反射を見てみる

50

伝搬時間5ns。同軸ケーブルで

1m相当

0 2 4 6 8 10-2

-1

0

1

2

同軸ケーブル上の位置 [m]

電圧

[V

]

ピーク値1V

0 2 4 6 8 10-2

-1

0

1

2

電圧

[V

]

0 2 4 6 8 10-2

-1

0

1

2

電圧

[V

]

正弦波(アナログ信号)の伝送の場合

10m = 2.5波長

0.2m@1nsだけ進んでいる

進む波

戻る波

0.2m@1nsだけ 戻っている

合成した波は振幅が変化している

この図は電圧を例にして表記している 進む波は、ピーク値1V

(ピークからピークは2V、実効値0.7V)

「ミスマッチ」 状態

52

ミスマッチで生じる定在波とその大きさ

0 2 4 6 8 10-20

-10

0

10

20

同軸ケーブル上の位置 [m]

電圧

[V

]

周波数50MHz、位相速度は高速の66%、

反射係数0.33、進行波波高10V

移動しない山ができる

移動しない谷ができる

53

1/8波長 0.5m

1/8波長 0.5m

信号源

1/8波長 0.5m

電圧 0.6V 電流 28mA 位相 0°

V/I = 21Ω

電圧 1.1V 電流 22mA 位相 -44.8°

V/I = 50Ω

電圧 1.1V 電流 22mA 位相 +44.8°

V/I = 50Ω

電圧 1.4V 電流 12mA 位相 0°

V/I = 120Ω

35.5 - j 35.2 (90pF) 35.5 + j 35.2 (112nH)

周波数50MHzで考えている。位相は電流の位相。リアクタンスは周波数で変化するので注意。 nは10-9

ここではピークからピークの大きさで示してある

これは連続した正弦波で考えている

ピーク値1V

マッチングしていないと途中の見かけ上のインピーダンスが変化する

54

LVDSで高速(かつ低EMI)差動伝送

(3.5mA)

(3.5mA)

+3.3V)

3.5k W 3.5k W

+1.2V

(3.5mA)

(3.5mA)

ADC出力LVDSドライバ

(+3.3V)

3.5k W 3.5k W

+1.2V

V+

V+ V–

V–

グラウンドへの

リターン電流が無い

差動伝送線路(差動特性

インピーダンス100Ω)

振幅レベルが かなり小さい!

EMI対策にも良好

アナログ・デバイセズのAN-586がLVDSについて説明 56

クロック用IC

AD9514

(LVDS出力)

この間を100Ω

で差動終端すべき

出力側

終端抵抗

差動

出力端

この端子間を

差動プローブで

計測

57

AD9514のLVDS 200Mbps 信号で終端状態のデモ

ゼロV

ゼロV

1.2V

-信号ライン(CH2)

等しい振幅量(350mV)

の逆相信号

500mV/Div

58

CLKドライバ AD9514のLVDS 200Mbps 信号で終端状態のデモ (シングル・エンドで観測)

+信号ライン(CH1)

1GHz差動プローブP6247

(テクトロニクス)を使って計測

撮影上の理由でグラウンド(基準)端子は未接続

59

適切にプロービングする(できるだけ短く接続)

この端子間を

差動プローブで

計測

1UIに

相当

終端抵抗

なし

AD9514

LVDS出力

同軸ケーブル1m

この端子間を

差動プローブで

計測

60

適切に終端されていない場合の信号反射

プリント基板上の振る舞いのデモのため

1m、2本の同軸、60Mbpsの条件で等価的な実験をする

1UIに

相当

100Ω抵抗

差動終端

AD9514

LVDS出力

同軸ケーブル1m

この端子間を

差動プローブで

計測

61

適切に終端された場合の信号波形(60Mbps)

プリント基板上だとして、1/10にスケーリングしてみると

10cmストリップ・ライン、600Mbps(繰返し300MHz)の条件と同じ

信号はパターン上を「波」として移動(伝搬)する

このイメージを理解することが大切

電圧と電流の「波」の比率が特性インピーダンス

中に抵抗体があるわけではない

特性インピーダンスに合わせた「終端」が必要

終端が不適切だと信号が反射する

差動伝送でも考え方は同じ

回路のうごきの「基本」をイメージで抑えておくだけで、トラブルを未然に回避できる

62

全体(後半)のまとめ