Magistrale szeregowe

description

Transcript of Magistrale szeregowe

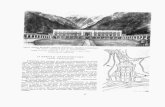

Magistrale szeregowe

Magistrale 2/22

panel operatorski

inne systemy urządzeniakontr-pomiar.

timeryRTC

dekodery adresów

ukł.obsługiPAO

kontrolery przerwań

pamięci zewn.

procesor

pamięćprogramu(ROM)

pamięćdanych(RAM)

urz.opera- torskie

urz.komuni-kacyjne

urz.obiek- towe

magistrala systemowa

magistrale komunikacyjne

Magistrale komunikacyjne - I2C 3/22

I2C - “międzyscalakowa” synchroniczna magistrala szeregowa Philips’a (I2C = IIC = Inter-Integrated Circuit)

Zastosowania: komunikacja w rozproszonych systemach automatyki i pomiarów; sterowanie urządzeniami peryferyjnymi; nowoczesny sprzęt powszechnego użytku.

Budowa:

SCL - linia zegara o fMAX=100kHz (pierwotnie), 400kHz (standard 1.0

z 1992r.) 1MHz-3,4MHz (rozszerzenie 2.0 standardu z 1998r.);

SDA - linia danych;

wspólna masa;

linie SCL i SDA są sterowane przez wyjścia typu OC (OD)

- konieczna jest polaryzacja opornikami do Vcc;

do jednej magistrali może być dołączonych do 32 urządzeń.

Magistrale komunikacyjne - I2C 4/22

Charakterystyczne bity:

SCL

SDA

SCL

SDA

SCL

SDA

SCL

SDA

“S”bit startu

“D”bit danych

“A”bit potwierdzenia

“E”bit stopu

Transmisja polega na transmisji bajtów:

SCL

SDA D7 D6 D5 D4 D3 D2 D1 D0 A

Magistrale komunikacyjne - I2C 5/22

Transmisja jest realizowana między urządzeniem nadrzędnym (master), dostarczającym sygnału SCL i podrzędnym (slave), obsługującym tylko SDA.

Możliwe typy urządzeń dołączonych do jednej gałęzi I2C:

SCLSDA

Vcc

masternad/odb

slavenad/odb

slaveodb

masternad/odb

slavenad/odb

slavenad/odb

Magistrale komunikacyjne - I2C 6/22

Przy transmisji master slave bit “A” generuje slave gdy został poprawnie

zaadresowany i odebrał daną. Transmisję rozpoczyna master bitem “S”.

Transmisję kończy master bitem “E” lub nowym bitem “S”.

SCLmaster

SDAmaster S D7 D6 D5 D4 D3 D2 D1 D0 E S D7 D6 D5

SDAslave

A

Magistrale komunikacyjne - I2C 7/22

Przy transmisji slave master bit “A” generuje master gdy odebrał daną i ma

zamiar odbierać następne dane od slave. Nie podanie przez master bitu “A”

zmusza slave do przerwania nadawania. Transmisję kończy master bitem “E” lub

nowym bitem “S”.

SCLmaster

SDAslave D0 D7 D6 D5 D4 D3 D2 D1 D0

SDAmaster A

jest potwierdzenie od master S D7 D6 D5brak potwierdzenia od master

Magistrale komunikacyjne - I2C 8/22

Adresowanie urządzeń

Podstawowe mechanizmy adresowania pozwalają zaadresować do 128 urządzeń

na jednej magistrali. Każde z urządzeń musi mieć nadany sprzętowo 7-bitowy

adres. Urządzenia mogą mieć różny charakter: master albo slave i realizować

transmisję jako: nadajniki, odbiorniki lub nadajniki-odbiorniki. Aby slave mógł

uczestniczyć w transmisji, musi najpierw zostać zaadresowany przez aktywnego

mastera. Master wysyła adres wywoływanego slave-a razem z bitem R/W

określającym kierunek transmisji następnych bajtów.

Magistrale komunikacyjne - I2C 9/22

Typowe protokoły transmisji:1. master slave z pojedynczym rejestrem wewnętrznym

2. slave z pojedynczym rejestrem wewnętrznym master

S slave adres 0 A bajt danych A X

slave

master master

slave

R/W master

S slave adres 1 A bajt danych 1 X

slave

master masterR/W

slave

Magistrale komunikacyjne - I2C 10/22

3. master slave o wielu rejestrach wewnętrznych

S slave adres 0 A adres wewn. slave A bajt danych A X

slave

master x N master

slave +slave

R/W

4. slave o wielu rejestrach wewnętrznych master

S slave adres 1 A bajt danych A bajt danych 1 X

slave

master

N

mastermaster

+slave

R/W

x (N-1)+

slave

Magistrale komunikacyjne - I2C 11/22

Przykładowa gałąź magistrali I2C:

100n10k

VCC

VCCVCCVCC

SCL

SDA

VCCPCF8583RTC+240BCMOSRAM

32768

OSCI

OSCO

1 2 3

A0

5 6 7

SDA

TEST

SCL

PCF8570256BCMOSRAM

A0

A1

A2

4k7

4k7

1 2 3

5 6 7

PCF8570256BCMOSRAM 1 2 3

5 6 7

PCF8582256BEEPROM 1 2 3

5 6 7

SDA

TEST

SCL

SDA

RC

SCL

SDA

_INT

SCL

A0

A1

A2

A0

A1

A2

ADR=1010000 ADR=1010101 ADR=1010001 ADR=1010011

Magistrale komunikacyjne - D2BUS 12/22

D2BUS (D2BUS = DDBUS = Digital Data Bus)

Cechy D2BUS:

szybkość do 100kb/s;

zasięg do 150m;

możliwość zaadresowania do 4096 urządzeń;

do 50 urządzeń w jednej gałęzi magistrali;

jako łącze występuje najczęściej skrętka;

możliwość przejęcia sterowania magistralą przez którekolwiek

z urządzeń mające funkcję D2BUS master;

usunięcie lub wyłączenie urządzenia nie wpływa na komunikację

pomiędzy pozostałymi urządzeniami;

magistrala służy do komunikacji pomiędzy urządzeniami,

wewnątrz których zastosowano I2C.

Magistrale komunikacyjne - D2BUS 13/22

Przykład ramki magistrali D2BUS:

S - bit startu, P - bit parzystości, A - bit potwierdzenia, E - bit stopu

Zastosowania D2BUS:

łączenie niewielkiej liczby urządzeń rozmieszczonych na niedużym obszarze (np. rozproszone lokalnie układy automatyki, sprzęt audio-wideo).

Magistrale komunikacyjne - D2BUS 14/22

Przykład wykorzystania D2BUS:

Magistrale komunikacyjne - CAN 15/22

CAN (Controller Area Network)

opracowanie firm Bosch i Intel

Cechy magistrali:

asynchroniczna, o dużej liczbie nadajników i odbiorników

(do 2032 w wersji 2.0A; do 500mln w wersji 2.0B);

usunięcie lub wyłączenie urządzenia nie wpływa na komunikację

pomiędzy pozostałymi urządzeniami;

szybkość do 1Mb/s przy 40m;

zasięg do 1000m przy 40kb/s;

nośnik: skrętka symetryczna;

bity są kodowane napięciami różnicowymi;

niewrażliwa na zakłócenia elektromagnetyczne.

Magistrale komunikacyjne - CAN 16/22

Gałąź CAN:

Standardowa ramka danych CAN:

Magistrale komunikacyjne - CAN 17/22

Zastosowania:

technika motoryzacyjna (wtrysk paliwa, ABS, poduszki powietrzne, systemy

oświetlenia, klimatyzacja, zabezpieczenia), technika lotnicza, roboty

przemysłowe, sterowniki przemysłowe (Siemens).

J1850 - odmiana amerykańska, niekompatybilna elektrycznie z CAN, stosowana m.in. przez Chrysler, General Motors, Ford

ABUS - podobny do CAN system Volkswagena

VAN - podobny do CAN system Peugeot i Renault

Magistrale komunikacyjne - SPI 18/22

SPI (Serial Peripherial Interface)

opracowanie Motoroli

Cechy magistrali:

transmisja synchroniczna, pełnodupleksowa;

szybkość typowo 1,5Mb/s, maksymalnie do 6..10Mb/s;

trzy linie transmisyjne + linia wyboru układu podrzędnego;

4 tryby transmisji, zależnie od polaryzacji i wykorzystania zboczy zegara;

podział na układy master i slave;

master jest odpowiedzialny za generację sygnałów zegarowego i wyboru;

możliwe jest dołączenie wielu master i slave do jednej magistrali;

brak mechanizmów adresowania.

Zastosowania SPI:

obsługa szeregowych pamięci konfiguracji, przetworników A/C i C/A, komunikacja wieloprocesorowa.

Magistrale komunikacyjne - SPI 19/22

Przykład magistrali SPI:

Przykład ramki komunikacji z pamięcią EEPROM:

Magistrale komunikacyjne - SMBUS 20/22

SMBUS (System Management Bus)

opracowanie Intela z lat 80-tych

Cechy SMBUS:

• koncepcyjnie zbliżony do I2C;

• magistrala składa się z linii SMBDAT i SMBCLK;

• kompatybilny z I2C przy częstotliwości taktowania do 100kHz;

• określony jest limit czasu wykonania operacji - 25ms;

• taktowanie może być z przedziału 10kHz-100kHz.

Magistrale komunikacyjne - Microwire 21/22

Microwire

opracowanie National Semiconductor

Cechy magistrali:

• koncepcyjnie zbliżona do SPI;

• transmisja synchroniczna, pełnodupleksowa, zgodna z trybem 0 SPI;

• maksymalna szybkość transmisji 650kb/s;

• magistrala składa się z linii: SI (wejście), SO (wyjście) i SC (zegar);

• brak sygnałów wyboru układu podrzędnego.

Zastosowania:

komunikacja z pamięciami EEPROM, przetwornikami A/C i C/A,

specyficzne układy wykorzystywane w torach radiowych,

sprzęcie telekomunikacyjnym i urządzeniach audio.

Magistrale komunikacyjne - 1-Wire 22/22

1-Wire

opracowanie Dallas Semiconductor/Maxim

Cechy magistrali:

• jednoprzewodowa magistrala - połączenie zasilania i linii transmisyjnej;

• transmisja synchroniczna, półdupleksowa;

• szybkość transmisji 16,3kb/s (tryb standard) i 115,2kb/s (tryb overdrive);

• ograniczony czas trwania bitu (60s);

• występują układy master i slave;

• układy mają unikalne identyfikatory - możliwość adresowania slave-ów.

Zastosowania:

rodzina układów iButton, mierniki temperatury, pamięci RAM , ROM, EPROM

i EEPROM, zegary RTC, przetworniki A/C, interfejsy do innych łączy

szeregowych (RSxxx, USB), monitory zasilania, potencjometry cyfrowe.