FIR コンパイラ ユーザーガイド - IntelアルテラFIR...

Transcript of FIR コンパイラ ユーザーガイド - IntelアルテラFIR...

101 Innovation DriveSan Jose, CA 95134www.altera.com

FIR コンパイラユーザーガイド

ソフトウェア・バージョン: 11.0ドキュメント・デート: 2011 年 5 月

Copyright © 2011 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all otherwords and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and othercountries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending ap-plications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty,but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use ofany information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version ofdevice specifications before relying on any published information and before placing orders for products or services.

UG-FIRCOMPILER 11.0

© 2011 年 5 月 Altera Corporation

目次

第 1 章 . FIR コンパイラについて機能 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1‒4リリース情報 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1‒5デバイス・ファミリのサポート . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1‒6MegaCore 検証 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1‒7パフォーマンスおよびリソース使用率 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1‒7インストールおよびライセンス . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1‒9OpenCore Plus 評価機能 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1‒9OpenCore Plus タイム・アウト動作 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1‒10

第 2 章 . 使用法 デザイン・フロー . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2‒1DSP Builder フロー . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2‒1MegaWizard Plug-In Manager フロー . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2‒2MegaCore ファンクションのパラメータ化 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2‒4MegaCore ファンクションの生成 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2‒7デザインのシミュレーション . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2‒10ModelSim でのシミュレーション . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2‒10MATLAB でのシミュレーション . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2‒10NativeLink を使用したサード・パーティ・シミュレーション・ツールのシミュレーション 2‒10

デザインのコンパイルおよびデバイスのプログラム . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2‒11

第 3 章 . パラメータの設定係数の指定 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3‒1FIR コンパイラを使用した係数生成機能 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3‒3ファイルから係数のロード . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3‒7

係数の解析 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3‒8入力および出力仕様の指定 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3‒10アーキテクチャ仕様の指定 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3‒11推定リソース . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3‒18フィルタ・デザインのヒント . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3‒18

第 4 章 . 機能の説明FIR コンパイラ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒1数のシステムと固定小数点精度 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒1係数の生成またはインポート . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒1係数のスケーリング . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒2シンメトリカル・アーキテクチャの選択 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒3対称的なシリアル . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒3係数リロードおよびリオーダリング . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒4

構造の種類 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒6マルチサイクル構造 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒6パラレル構造 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒6シリアル構造 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒7マルチビット・シリアル構造 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒7マルチ・チャネル構造 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒8

補間およびデシメーション . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒9補間およびデシメーション構造のための実装の詳細 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒10

FIR コンパイラ ユーザーガイド

2 目次

補間およびデシメーション・フィルタの可能性 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒11ハーフ・バンドのディシメーション・フィルタ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒12対称補間のフィルタ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒12

Pipelining . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒13シミュレーション出力 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒13Avalon Streaming インタフェース . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒13Avalon-ST データ転送のタイミング . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒15パケット・データ転送 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒16

信号 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒16タイミング図 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒18リセットおよびグローバル・ クロック・イネーブル動作 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒19シングル・レート・ フィルタのタイミング図 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒19補間フィルタのタイミング図 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒22デシメーション・フィルタのタイミング図 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒23係数リロードのタイミング図 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒24

参考資料 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4‒27

付録 A. FIR コンパイラでサポートされるデバイスの構造サポートされるデバイスの構造 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A‒1HardCopy シリーズ・デバイスのサポート . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A‒4HardCopy デザインのコンパイル . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A‒5

追加情報改訂履歴 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info‒1アルテラへのお問い合わせ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info‒2表記規則 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Info‒3

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

© 2011 年 5月 Altera Corporation

1. FIR コンパイラについて

本書では、Altera® FIR コンパイラについて説明します。 FIR コンパイラは、完全に統

合された有限インパルス応答(FIR)フィルタ開発環境を提供し、アルテラの FPGAデバイスに 適化されます。

アルテラの IP Toolbench インタフェースは FIR コンパイラと使用可能であり、完全な

パラレル、シリアル、または汎用ロジックを使用したマルチビット・シリアル演算、

およびマルチサイクルの固定 / 可変フィルタなどの、さまざまなフィルタ・アーキテ

クチャを実装できます。 FIR コンパイラには係数生成機能を内蔵しています。

従来より、設計者は DSP プロセッサの柔軟性と ASIC および ASSP (Application-Specific Standard Product) デジタル信号処理ソリューションの性能間でト

レードオフを図るよう強いられてきました。アルテラの DSP ソリューションは、

FPGA の柔軟性と卓越した性能により、これらを両立させることが可能です。

図 1–1 に、FIR コンパイラおよび他の DSP IP コアを含むアルテラの IP コアを使用し

た標準的な DSP システムを示します。

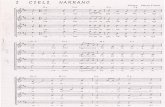

図1‒1. 標準的なモジュレータ・システム

FEC Reed Solomon

Encoder

Convolutional Encoder (Viterbi)

Constellation Mapper

Outer Encoding Layer

Output Data

Input Data

NCO Compiler DAC

FIR Compiler

N LPF

FIR Compiler

N LPF

Convolutional Interleaver

Inner Coding Layer

I

Q

FIR コンパイラ ユーザーガイド

1‒2 第 1 章 : FIR コンパイラについて

多くの複雑なシステムでは、不要な電圧を除去するか、スペクトル整形を提供する

か、または信号の検出か解析を実行するために信号フィルタリングを使用します。 これらの機能を提供する 2 つのタイプのフィルタは、有限インパルス応答(FIR)フィ

ルタと無限インパルス応答(IIR)フィルタです。標準的なフィルタ・アプリケー

ションには信号プリコンディショニング、バンド選択、およびロー・パス・フィル

タリングが含まれます。

IIR フィルタと対照的に、FIR フィルタはリニア位相および固有安定性を持っていま

す。この利点は、多数のシステムに設計されるために十分魅力的な FIR フィルタに

なります。しかし、与えられた周波数応答のために、FIR フィルタは、IIR フィルタ

よりも高い注文で、より多くの計算コストとなっています。

図 1–2 に示すように、FIR フィルタの構造は、加重されたタップド・ディレイ・ライ

ンです。

図1‒2. 基本的な FIR フィルタ

xin

yout

Z -1 Z -1 Z -1 Z -1

C0 C1 C2 C3

TappedDelay Line

CoefficientMultipliers

Adder Tree

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 1 章 : FIR コンパイラについて 1‒3

フィルタのデザイン・プロセスで、システムに指定された周波数応答に合致する係

数を決定します。 これらの係数によってフィルタの応答が決まります。係数の値を変

更することまたは係数を追加することにより、フィルタを通過する信号の周波数が

変更できます。

DSP プロセッサは乗算累積器(MAC)の数に制約があり、サイクル数がフィルタの

次数に直接関係するので、各出力値を計算するのに多くのクロック・サイクルを必

要とします。

専用ハードウェア・ソリューションは、クロック・サイクルあたり 1 出力を達成で

きます。 FPGA に実装された完全パラレル、パイプライン化された FIR フィルタは、

高速フィルタリング・アプリケーション用の FPGA は理想的にして、非常に高いデー

タ・レートで動作することができます。

表 1–1 に、12 ビットのデータ入力バスを持つ 120 タップ FIR フィルタの実装が異な

る場合のリソースの使用状況とパフォーマンスを比較します。

アルテラ FIR コンパイラは、以下の方法によってデザイン・サイクルを短縮します。

■ カスタム FIR フィルタをデザインするために係数を発生する必要がある。

■ ビット単位およびクロック・サイクル単位でシミュレーション可能な FIR フィル

タ・モデル(bit-true モデルとも呼ばれる)を Verilog HDL および VHDL 言語、

MATLAB 環境用に生成する。

■ 各種アーキテクチャの高速で面積効率の高い FIR フィルタを合成するために、

Quartus II ソフトウェアに必要なコードを自動生成する。

■ すべてのアーキテクチャ用の VHDL テストベンチを生成する。

表1‒1. FIR フィルタ実装の比較 ( 注 1)

デバイス 実装結果を計算するためのクロック・サイクル数

DSP プロセッサ 1 MAC 120

FPGA 1 シリアル・フィルタ 12

1 パラレル・フィルタ 1

表 1‒1の注:(1) フィルタを作成するために FIRコンパイラを使用する場合、1から 120までの MACおよび 120~1のクロック・サイクルを使用する FPGAに可変フィルタを実現することができます。

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

1‒4 第 1 章 : FIR コンパイラについて機能

図 1–3 は、従来の実装と FIR コンパイラを使用して、デザイン・サイクルを比較し

ます。

機能Altera® FIR コンパイラは有限インパルス応答 (FIR) フィルタ MegaCore ファンクショ

ンを実装して、以下のような機能もサポートしています。

■ ロジック、メモリ、DSP ブロック、およびパフォーマンス間の 適なトレードオ

フを有効にするために以下のハードウェア・アーキテクチャをサポートされてい

ます。

■ 汎用ロジックを使用した完全パラレル演算

■ 汎用ロジックを使用した完全シリアル演算

■ 汎用ロジックを使用したマルチビット・シリアル演算

■ マルチサイクル構造

■ このようなインターポレーション、デシメーション、対称性、デシメーション・

ハーフ・バンド、およびタイム・シェアリングなどの FIR コンパイラ・ハード

ウェアの 適化の結果として、 大効率設計を利用します。

■ Avalon® Streaming(Avalon-ST)インタフェースを使用する簡単なシステムの統合。

図1‒3. デザイン・サイクルの比較

Define & Design Architectural Blocks

Determine BehavioralCharacteristics of FIR Filter

Calculate Filter Coefficients(MATLAB)

Determine Hardware FilterArchitecture

Design Structural or SynthesizableFIR Filter

Simulate

Synthesize & Place & Route

Area/Speed Tradeoff

FIR FilterDesign6 Weeks

Define & Design Architectural Blocks

Simulate

Synthesize & Place & Route

FIR Filter Design1 Day

Specify Filter Characteristicsto FIR Compiler Megafunction(FIR Compiler Assists in Area/

Speed Tradeoff)

Traditional Flow FIR Compiler Flow

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 1 章 : FIR コンパイラについて 1‒5リリース情報

■ チップ上のリソース使用を的確に制御。

■ ロジック・セル、M512、 M4K、 M-RAM、 MLAB、 M9K、 または M144K をデータの

保存に使用

■ M512、M4K、M9K、 M20K、 MLAB またはロジック・セルを係数の保存に使用

■ リソース使用量推定機能を内蔵

■ ランタイムの係数リロード機能と、複数の係数セットをサポート。

■ 効率的なデザイン・スペース・エクスプロレーションを有効にするために、係数

の生成機能を内蔵。

■ 丸め処理および飽和処理を適用したユーザー選択可能な出力精度。

■ DSP Builder Ready。

リリース情報表 1–2 に、Altera® FIR コンパイラのリリースに関する情報を示します。

f このリリースの情報について詳しくは、「MegaCore IP Library Release Notes and Errata」を参照してください。

表1‒2. FIR コンパイラのリリース情報

項目 説明

バージョン 11.0

リリース月 2011 年 5 月

製品コード IP-FIR

プロダクト ID 0012

ベンダ ID 6AF7

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

1‒6 第 1 章 : FIR コンパイラについてデバイス・ファミリのサポート

アルテラは、Quartus® II ソフトウェアの現行バージョンが、各 MegaCore® ファンク

ションの前のバージョンをコンパイルできることを検証しています。MegaCore IP Library Release Notes and Errata では、この検証に例外がある場合に報告します。アル

テラは、1 リリースより前の MegaCore ファンクション・バージョンのコンパイルは

検証していません。

デバイス・ファミリのサポート表 1–3 に、アルテラの IP コアのデバイス・サポートのレベルを定義します。

表 1–4 に、FIR コンパイラによる各アルテラ・デバイス・ファミリへのサポートのレ

ベルを示します。

表1‒3. アルテラの IP コアのデバイス・サポート・レベル

FPGA デバイス・ファミリ HardCopy デバイス・ファミリ

暫定サポート —IP コアはこのデバイスファミリのための暫定タイミング・モデルと検証されます。 IP コアがデバイス・ファミリの機能要件はすべて満たしているが、タイミング要件については評価中しています。製造デザインでの使用は注意が必要なことを意味します。

HardCopy コンパニオン —IP コアは HardCopy コンパニオン・デバイスのための暫定タイミング・モデルと検証されます。IP コアが HardCopy デバイス・ファミリの機能要件はすべて満たしているが、タイミング要件については評価中しています。製造デザインでの使用は注意が必要なことを意味します。

終的なサポート —IP コアはこのデバイスファミリのための 終的なタイミング・モデルと検証されます。 IP コアがデバイス・ファミリの機能要求およびタイミング要求をすべて満たしており、製造デザインとして使用可能であることを意味します。

HardCopy コンパイル —IP コアは HardCopy デバイスファミリのための 終的なタイミング・モデルと検証されます。IP コアがデバイス・ファミリの機能要求およびタイミング要求をすべて満たしており、製造デザインとして使用可能であることを意味します。

表1‒4. サポートされるデバイス・ファミリ ( その1 )

デバイス・ファミリ サポートの種類 Arria™ GX 終的

Arria II GX 終的

Arria II GZ 終的

Cyclone® 終的

Cyclone II 終的

Cyclone III 終的

Cyclone III LS 終的

Cyclone IV GX 終的

HardCopy® II HardCopy コンパイル

HardCopy III HardCopy コンパイル

HardCopy IV E HardCopy コンパイル

HardCopy IV GX HardCopy コンパイル

Stratix® 終的

Stratix II 終的

Stratix II GX 終的

Stratix III 終的

Stratix IV GT 終的

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 1 章 : FIR コンパイラについて 1‒7MegaCore 検証

MegaCore 検証FIR コンパイラの更新バージョンをリリースする前に、アルテラは品質や正確性を検

証するための包括的な回帰テストを実施します。

すべての機能とアーキテクチャは、すべてのパラメータのオプションをスイープし、

シミュレーションがマスタ機能モデルと一致していることを検証することでテスト

されます。

パフォーマンスおよびリソース使用率ここでは、 Cyclone III および Stratix IV デバイスと FIR コンパイラ MegaCore ファンク

ションの標準的な期待パフォーマンスを示します。すべての図は 97 タップ、8 ビッ

トの入力データ、14 ビットの係数、および 1 GHz に設定したターゲット fMAX のはを

持つ FIR フィルタに提供されます。

1 Cyclone III デバイスはルックアップ・テーブル(LUT)とロジック・レジスタを使用

し、 Stratix IV デバイスはアダプティブ・ルックアップ・テーブル(ALUT)とロジッ

ク・レジスタを使用しています。

リソースとパフォーマンス・データは、 4–13 ページの「Avalon Streaming インタ

フェース」で説明されたように、常に High にドライブされたソースの ready 信号

(ast_source_ready)で生成されます。

表 1–5 に、Cyclone III デバイスのパフォーマンスを示します。

Stratix IV GX/E 終的

Stratix V 暫定サポート

Stratix GX 終的

その他のデバイス・ファミリ サポートなし

表1‒4. サポートされるデバイス・ファミリ ( その2 )

デバイス・ファミリ サポートの種類

表 1‒5. FIR コンパイラ・パフォーマンス̶Cyclone III デバイス ( その1 )

組み合わせ LUTs

ロジック レジスタ

メモリ (6) マルチプライヤ(9x9)

fmax(MHz)

スループット (MSPS)

等価の処理 (GMACs) (1)ビット M9K

マルチビット・シリアル、パイプライン・レベル 1 (2), (3) 899 1,331 55,148 31 — 310 62 6

4 によるマルチサイクル(1 サイクル)のデシメーション、パイプライン・レベル 1 (2), (3) 857 1,336 1,158 12 26 281 281 27

4 によるマルチサイクル(1 サイクル)のインターポレーション、パイプライン・レベル 1 (4) 1,528 2,657 66 1 50 290 290 28

マルチサイクル (1 サイクル)、パイプライン・レベル 2 (2), (4) 2,543 4,837 92 1 98 280 280 27

マルチサイクル (4 サイクル)、パイプライン・レベル 2 (2), (3) 1,182 1,715 578 9 26 283 71 7

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

1‒8 第 1 章 : FIR コンパイラについてパフォーマンスおよびリソース使用率

表 1–6 に、Stratix IV デバイスのパフォーマンスを示します。

パラレル(LE)、パイプライン・レベル 1 (2), (3) 3,416 3,715 208 3 — 288 288 28

パラレル(M9K)、パイプライン・レベル 1 (2), (5) 1,948 2,155 120,030 48 — 283 283 27

シリアル(M9K)、パイプライン・レベル 1 (2), (3) 327 462 14,167 8 — 323 36 3

表1‒5の注:(1) GMAC = 秒あたりギガ乗算の蓄積(1 ギガ = 10億)。(2) この FIRフィルタは、対称係数を利用しています。(3) EP3C10F256C6デバイスを使用します。(4) EP3C16F484C6デバイスを使用します。(5) EP3C40F780C6デバイスを使用します。(6) ターゲット fMAXをより低く設定することで、メモリ使用率を大幅に低減できる場合があります。

表1‒5. FIR コンパイラ・パフォーマンス̶Cyclone III デバイス ( その2 )

組み合わせ LUTs

ロジック レジスタ

メモリ (6) マルチプライヤ(9x9)

fmax(MHz)

スループット (MSPS)

等価の処理 (GMACs) (1)ビット M9K

表 1‒6. FIR コンパイラ・パフォーマンス̶Stratix IV デバイス

組み合わせ ALUTs

ロジック レジスタ

メモリ マルチプライヤ

(18x18)fmax (MHz)

スループッ (MSPS)

等価の処理 (GMACS) (1)ビット (M9K) ALUTs

マルチビット・シリアル、パイプライン・レベル 1 (2), (3), (4) 766 1,166 55,276 42 16 — 503 101 10

4 によるマルチサイクル(1 サイクル)のデシメーション、パイプライン・レベル 1 (2), (3) 336 844 1,400 16 28 14 443 443 43

4 によるマルチサイクル(1 サイクル)のインターポレーション、パイプライン・レベル 2 (3) 200 1,274 64 — 8 24 372 372 36

マルチサイクル (1 サイクル)、パイプライン・レベル 2 (2), (3) 741 1,936 148 1 8 48 443 443 43

マルチサイクル (1 サイクル)、パイプライン・レベル 2 (2), (3) 717 1,398 796 6 36 14 323 81 8

パラレル(LE)、パイプライン・レベル 1 (2), (3) 2,153 2,672 157 1 8 — 421 421 41

パラレル(M9K)、パイプライン・レベル 1 (3) 821 1,730 119,872 45 8 — 457 457 44

シリアル(M9K)、パイプライン・レベル 1 (2), (3) 245 415 14,231 11 8 — 523 58 6

表1‒6の注:(1) GMAC = 秒あたりギガ乗算の蓄積(1 ギガ = 10億)。(2) この FIRフィルタは、対称係数を利用しています。(3) EP4SGX70DF29C2Xデバイスを使用します。(4) データ幅は 16ビットで、4つのシリアルユニットがあります。

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 1 章 : FIR コンパイラについて 1‒9インストールおよびライセンス

インストールおよびライセンスFIR コンパイラ MegaCore ファンクションは、MegaCore® IP ライブラリの一部であり、

Quartus® II ソフトウェアとともに配布されます。また、Altera® ウェブサイト

(www.altera.co.jp)からダウンロードすることもできます。

f システム要件とインストール手順については、「アルテラ・ソフトウェアのインストールおよびライセンス」のマニュアルを参照してください。

図 1–4 に、FIR コンパイラをインストールした後のディレクトリ構造を示します。こ

こで、、<path>が Quartus II ソフトウェアのインストール・ディレクトリです。

Windows でのデフォルトのインストール・ディレクトリは、 c:\altera\<version> です。

Linux では、 /opt/altera<version> です。

OpenCore Plus 評価機能アルテラの無償 OpenCore Plus 評価機能により、以下の処理を実行できます。

■ 作成したシステム内のメガファンクション(アルテラ MegaCore ファンクションま

たは AMPPSM メガファンクション)の動作をシミュレーションする。

■ デザインの機能を検証したり、サイズやスピードを迅速かつ簡単に評価したりす

る。

■ メガファンクションを含むデザインに対し、時間制限つきのデバイス・プログラ

ミング・ファイルを生成する。

■ デバイスをプログラムし、デザインを実機上で検証する。

図1‒4. ディレクトリ構造

miscContains the coef_seq program which calculates and re-orders coefficients for reloading.

libContains encrypted lower-level design files.

ipContains the Altera MegaCore IP Library and third-party IP cores.

<path>Installation directory.

alteraContains the Altera MegaCore IP Library.

commonContains shared components.fir_compilerContains the FIR Compiler MegaCore function files.

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

1‒10 第 1 章 : FIR コンパイラについてインストールおよびライセンス

機能および性能が十分満足できて、FIR コンパイラを製品に組み込む場合にのみ、ラ

イセンスを購入していただく必要があります。

ライセンス購入後は、アルテラ・ウェブサイト(www.altera.com/licensing)からライ

センス・ファイルを要求して、コンピュータにインストールできます。ライセンス・

ファイルを要求すると、アルテラから電子メールで license.dat ファイルが送信され

ます。インターネットをご利用いただけないお客様は、アルテラの販売代理店にお

問い合わせください。

f OpenCore Plus ハードウェア評価について詳しくは、「AN320: OpenCore 評価機能によるメガファンクションの評価」を参照してください。

OpenCore Plus タイム・アウト動作OpenCore Plus ハードウェア評価機能は、以下の動作モードでメガファンクションの

実機評価をサポートします。

■ Untethered(アンテザード)— デザインは限定時間のみ実行されます。

■ Tethered(テザード)— ボードとホスト・コンピュータ間に接続が必要です。デ

ザイン内のすべてのメガファンクションが Tethered モードをサポートしている場

合、デバイスはより長時間または無制限に動作できます。

OpenCore Plus 評価機能モードで動作中のメガファンクションのうちの 1 つでも評価

時間に達すると、デバイス内のすべてのメガファンクションが同時にタイム・アウ

トします。デザイン内に複数のメガファンクションがある場合、特定のメガファン

クションのタイム・アウト動作は、他のメガファンクションのタイム・アウト動作

によってマスクされることがあります。

MegaCore ファンクションの場合、アンテザード・タイム・アウトは 1 時間、テザー

ド・タイム・アウト値は無制限です。

データ出力信号はハードウェア評価が期限切れになると、0 に強制されます。

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

© 2011 年 5月 Altera Corporation

2. 使用法

デザイン・フローFIR コンパイラ MegaCore® ファンクションは、以下のデザイン・フローをサポートし

ています。

■ DSP Builder:FIRコンパイラMegaCoreファンクションのバリエーションを含む DSP Builder モデルを作成する場合、このフローを使用してください。

■ MegaWizard™ Plug-In Manager:ユーザーのデザインで、手動でインスタンス化で

きる FIR コンパイラ MegaCore ファンクションのバリエーションを作成する場合、

このフローを使用してください。

この章では、これらのフローのいずれかの FIR コンパイラ MegaCore ファンクション

を使用する方法について説明します。パラメータ化は、各フローに同じであり、 3 章

のパラメータの設定で説明されています。

これらのフローのいずれかのデザインをパラメータ化およびシミュレートした後、

Quartus II ソフトウェアで完成したデザインをコンパイルすることができます。

DSP Builder フローアルテラの DSP Builder 製品は、設計者がアルゴリズム開発の環境下で行った DSP デザインをハードウェアで実現するための支援を行い、デジタル信号処理 (DSP) のデ

ザイン・サイクルを短縮します。

DSP Builder は、MathWorks 社の MATLAB® および Simulink® システム・レベルのデザイ

ン・ツールのアルゴリズム開発、シミュレーション、および検証の機能と、アルテ

ラの Quartus II 開発ソフトウェアおよびサード・パーティの合成およびシミュレー

ション・ツールを組み合わせます。既存の Simulink ブロックをアルテラの DSP Builder ブロックおよび MegaCore ファンクションのバリエーション・ブロックと組み

合わせて、システム・レベル仕様を検証し、シミュレーションを実行することがで

きます。

DSP Builder の中で、FIR コンパイラの Simulink シンボルが、Altera DSP Builder Blocksetから MegaCore Functions ライブラリの Simulink ライブラリ・ブラウザに表示されま

す。

次の手順を実行して、MATLAB/ Simulink の環境で FIR コンパイラを使用することがで

きます。

1. 新規 Simulink モデルを作成します。

2. Simulink ライブラリ・ブラウザで、MegaCore Functions ライブラリから FIR Compilerブロックを選択し、ユーザーのモデルに追加し、ブロックに一意の名前

を付けます。

3. IP Toolbench を表示するには、モデル内の FIR Compilerブロックをダブル・ク

リックします。FIR コンパイラ MegaCore ファンクションのバリエーションをパラ

メータ化するには、Step 1: Parameterize をクリックします。FIR Compiler ブロックのパラメータをセットする方法の例について、 3 章のパラメータの設定を

参照してください。

FIR コンパイラ ユーザーガイド

2‒2 第 2章 : 使用法MegaWizard Plug-In Manager フロー

4. FIR コンパイラ MegaCore ファンクションのバリエーションを生成するには、IP Toolbench の Step 2: Generate をクリックします。生成されたファイルについ

て、2–7 ページの表 2–1 を参照してください。

5. FIR Compiler MegaCore ファンクションのバリエーションはモデル内の他のブ

ロックに接続します。

6. DSP Builder モデルの FIR コンパイラ MegaCore ファンクションのバリエーションを

シミュレートします。

f DSP Builder のフローについて詳しくは、「DSP Builder User Guide」の Using MegaCore Functions の章を参照してください。

1 DSP Builder のフローを使用している場合、デバイスの選択、シミュレーション、

Quartus II のコンパイルおよびデバイスのプログラミングは DSP Builder 環境内ですべ

て制御されます。

DSP Builder は、Avalon® Memory-Mapped (Avalon-MM) マスタまたはスレーブ、および

Avalon ストリーミング(Avalon-ST)ソースまたはシンク・インタフェースを使用し

て、SOPC Builder での統合をサポートします。

f これらのインタフェース・タイプについて詳しくは、 Avalon Interface Specifications を参

照してください。

MegaWizard Plug-In Manager フローMegaWizard Plug-In Manager フローでは、FIR コンパイラ MegaCore ファンクションを

カスタマイズし、手動で MegaCore ファンクションのバリエーションを Quartus II デザインに組み込むことができます。

MegaWizard Plug-in Manager を起動するには、以下のステップを実行します。

1. Quartus II ソフトウェアの File メニューから New Project Wizard を選択して、新規

のプロジェクトを作成します。

2. Tools メニューから MegaWizard Plug-in Manager を起動し、カスタム・メガファン

クション・バリエーションを作成するには、オプションを選択します(図 2–1)。

図2‒1. MegaWizard Plug-In Manager

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 2 章 : 使用法 2‒3MegaWizard Plug-In Manager フロー

3. Next をクリックして、Installed Plug-Ins タブでの DSP>Filters セクションから FIR Compiler <version> を選択します(図 2–2)。

4. デバイス・ファミリが New Project Wizard で指定したものと同じであることを確

認します。

5. デザインのトップ・レベル出力ファイル・タイプを選択します。ウィザードでは

VHDL と Verilog HDL をサポートしています。

6. MegaCore ファンクション・バリエーションのトップ・レベルの出力ファイル名を

指定し、 Next をクリックして、IP Toolbench を起動します( 2–4 ページの図 2–3)。

図2‒2. MegaCore ファンクションの選択

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

2‒4 第 2章 : 使用法MegaWizard Plug-In Manager フロー

MegaCore ファンクションのパラメータ化MegaCore ファンクション・バリエーションをパラメータ化するには、以下のステッ

プを実行します。

1. Parameterize - FIR Compiler ウィンドウを表示するには、IP Toolbench の Step 1: Parameterize をクリックします。 MegaCore ファンクション・バリエーションに必

要なパラメータを指定するには、このインタフェースを使用します。FIR コンパ

イラ MegaCore ファンクションのパラメータをセットする方法の例について、3 章

のパラメータの設定を参照してください。

図2‒3. IP Toolbench̶パラメータ化

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 2 章 : 使用法 2‒5MegaWizard Plug-In Manager フロー

2. Set Up Simulation - FIR Compiler のページを表示するには、IP Toolbench の Step 2: Setup Simulation をクリックします(図 2–4)。

3. Generate Simulation Model をオンにして、IP 機能シミュレーション・モデルを生

成します。

1 IP 機能シミュレーション・モデルは、QuartusII ソフトウェアで生成するサ

イクル精度の正確な VHDL または Verilog HDL モデルです。

c これらのシミュレーション・モデルは、シミュレーションの目的にのみ使

用し、合成やその他の目的には使用しないでください。これらのモデルを

合成に使用すると、動作しないデザインが作成されます。

4. Language リストから必要な言語を選択します。

5. Set Up Simulation ページの MATLAB M-File タブをクリックします(図 2–5)。

図2‒4. Set Up Simulation

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

2‒6 第 2章 : 使用法MegaWizard Plug-In Manager フロー

6. Generate MathWorks MATLAB M-File オプションをオンにします。

このオプションは、MATLAB 環境での FIR コンパイラ・デザインを分析するため

に使用できる関数が含まれている MATLAB m ファイルのスクリプトを生成しま

す。テストベンチも生成されます。

7. Finish をクリックします。

1 Quartus II Testbench タブは FIR コンパイラのバージョンで使用されないで、無視され

るべきであるオプションを含んでいます。

図2‒5. MATLAB M-File の作成

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 2 章 : 使用法 2‒7MegaWizard Plug-In Manager フロー

MegaCore ファンクションの生成MegaCore ファンクション・バリエーションを生成するには、以下のステップを実行

します。

1. Step 3: Generate をクリックし、MegaCore ファンクション・バリエーションとサ

ポートするファイルを生成します。ファイル生成フェーズを完了するには、数分

かかる場合があります。生成の進捗状況とステータスはレポート・ウィンドウに

表示されます。

図 2–6 に、生成レポートを示します。

表 2–1 に、プロジェクト・ディレクトリに IP Toolbench で生成されたファイルを

示します。 レポートで指定されるファイルの名前とタイプは、デザインを VHDLまたは Verilog HDL のいずれで作成したかによって異なります。

図2‒6. 生成レポート - FIR コンパイラ MegaCore ファンクション

表2‒1. 生成されるファイル ( その1 ) ( 注 1) , (2)

ファイル名 説明<entity name>.vhd Avalon-ST インタフェースの VHDL ラッパー・ファイル。

<variation name>.bsf MegaCore ファンクション・バリエーションの Quartus II ブロック・シンボル・ファイルです。Quartus II ブロック図エディタでこのファイルを使用できます。

<variation name>.cmp MegaCore ファンクション・バリエーション用の VHDL コンポーネント宣言ファイルです。このファイルの内容を、MegaCore ファンクションをインスタンスする VHDL アーキテクチャの 1 つに追加します。

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

2‒8 第 2章 : 使用法MegaWizard Plug-In Manager フロー

<variation name>.html MegaCore ファンクションは、ハイパーテキスト・マークアップ言語 (HTML) (Hypertext markup language) でレポートします。

<variation name>.qip Quartus II コンパイラの MegaCore ファンクション・バリエーションの処理に必要なすべてのアサインメントおよび他の情報が含まれる Quartus II IPファイルを生成されます。IP Toolbench から脱出すると、このファイルを現行の Quartus II プロジェクトに追加するように促されます。

<variation name>.vec Quartus II ベクタ・ファイル。 このファイルは、Quartus II ソフトウェアでカスタマイズされた FIR のカスタム MegaCore ファンクションをシミュレートするために使用するシミュレーション・テスト・ベクタを提供します。

<variation name>.vhd または .v カスタム MegaCore ファンクションの VHDL または Verilog HDL トップレベルの記述を定義する VHDL または Verilog HDL ファイルです。デザイン内部のこのファイルによって定義されたエンティティをインスタンスします。QuartusII ソフトウェアでのデザインのコンパイル時にこのファイルがインクルードされます。

<variation name>.vho または .vo IP 機能シミュレーション・モデルの記述を定義する VHDL または Verilog HDL の出力です。

<variation name>_bb.v MegaCore ファンクション・バリエーションの Verilog HDL ブラック・ボックス・ファイルです。サード・パーティ製 EDA ツールを使用してデザインを合成するときにこのファイルを使用します。

<variation name>_coef_in_mlab.txt

<variation name>_coef_int.txtMATLAB テストベンチに係数入力ファイルを提供するテキスト・ファイル。

<variation name>_coef_n_inv.hex

<variation name>_coef_n.hex

<variation name>_zero.hex

16 進(インテル・フォーマット)ファイル(.hex)のメモリ初期化ファイル。これらのファイルは、IP 機能シミュレーション・モデルのシミュレーションおよび Quartus II ソフトウェア用の合成が必要です。

<variation name>_constraints.tcl Quartus II 合成の制約の設定 Tcl ファイル。このファイルは、FIR フィルタのサイズとスピードを実現するには必要な制約を内蔵しています。

<variation name>_input.txt このテキスト・ファイルは、MATLAB モデルおよびシミュレーション・テストベンチのためのシミュレーション・データを提供します。

<variation name>_mlab.m この MATLAB M ファイルは、カスタマイズされた MegaCore ファンクション・バリエーションのために、MATLAB シミュレーション・モデルのカーネルを提供します。

<variation name>_model.m この MATLAB M ファイルは、カスタマイズされた MegaCore ファンクション・バリエーションのために、MATLAB シミュレーション・モデルを提供します。

<variation name>_msim.tcl この Tcl スクリプトは、カスタマイズされた FIR の MegaCore ファンクション・バリエーションのシミュレーション・モデルと一緒に VHDL テストベンチをシミュレートするために使用することができます。

<variation name>_nativelink.tcl NativeLink シミュレーション・テストベンチ設定を Quartus II プロジェクトに割り当てるために使用する Tcl スクリプトです。

<variation name>_param.txt このテキスト・ファイルは、カスタマイズされた FIR MegaCore ファンクション・バリエーションのためにすべての出力パラメータを記録します。

<variation name>_silent_param.txt このテキスト・ファイルは、カスタマイズされた FIR MegaCore ファンクション・バリエーションのためにすべての入力パラメータを記録します。

表2‒1. 生成されるファイル ( その2 ) ( 注 1) , (2)

ファイル名 説明

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 2 章 : 使用法 2‒9MegaWizard Plug-In Manager フロー

生成レポートには、MegaCore ファンクション・バリエーションに定義されたポー

トも表示されます(図 2–7)。 MegaCore ファンクション・バリエーションの外部

ポートでサポートされるすべての信号については、 4–16ページの表 4–3を参照し

てください。

2. 生成レポートを表示した後、Exit をクリックして IP Toolbench を閉じます。次に、

Quartus II IP Files プロンプトで Yes をクリックして、現在の Quartus II プロジェク

トにカスタム MegaCore ファンクションのバリエーションを説明する .qip ファイ

ルを追加します。

<variation name>_core.vhd

<variation name>_st.v

<variation name>_st_s.v

<variation name>_st_u.v

<variation name>_st_wr.v

生成された FIR フィルタ・ネットリスト。これらのファイルは、Quartus II合成に必要であり、現在の Quartus II プロジェクトを追加されます。

tb_<variation name>.vhd この VHDL ファイルは、カスタマイズされた FIR MegaCore ファンクション・バリエーションのためにテストベンチを提供します。

表2‒1の注: (1) <variation name> は、IP Toolbenchによって自動的に供給されるバリエーション名です。(2) <entity name> プリフィックスが自動的に追加されます。 各 MegaCoreインスタンスの VHDLコードは、Finishをクリックしたと

き動的に生成され、 <entity name> はインスタンスごとに異なります。 それは、 <variation name> に _ast.を追加して生成されます。

表2‒1. 生成されるファイル ( その3 ) ( 注 1) , (2)

ファイル名 説明

図2‒7. 生成レポートに表示されたポート・リスト

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

2‒10 第 2章 : 使用法MegaWizard Plug-In Manager フロー

デザインのシミュレーションVerilog HDL または VHDL にデザインをシミュレーションするには、IP Toolbench で生

成した IP 機能シミュレーション・モデルを使用します。

IP 機能シミュレーション・モデルは、2–4 ページのステップ 1 で指定したように、生

成された .vo または .vho ファイルです(デザイン・ディレクトリにあるファイル)。

f IP 機能シミュレーション・モデルについて詳しくは、「Quartus II Handbook Volume 3」の「Simulating Altera Designs」の章を参照してください。

ModelSimでのシミュレーションTcl スクリプト (<variation name>_msim.tcl) も生成され、ModelSim シミュレータに

VHDL のテストベンチをロードするために使用することができます。

このスクリプトでは、FIR フィルタに入力データを提供するために、ファイル <variation name>_input.txt を使用しています。シミュレーションからの出力は、ファ

イル <variation name>_output.txt に格納されています。

MATLAB でのシミュレーションMATLAB 環境でシミュレートするには、デザイン・ディレクトリにあるテストベンチ

m-script の <variation_name>_model.m を実行します。このスクリプトは、<variation name>_input.txt ファイルを使用して入力データを提供します。MATLAB シミュレー

ションからの出力は、ファイル <variation name>_model_output.txt に格納されていま

す。

MCV のデシメーションフィルタの場合、 <variation name>_model_output_full.txt ファイ

ルは、フィルタのすべての位相を表示するために生成されます。出力が属する位相

を理解するために、このファイルは、<variation name>_output.txt ファイルを比較する

ことができます。他のすべてのアーキテクチャでは、デシメーション・フィルタは

N 番目の位相を提供します。N 番目はデシメーション係数としています。

NativeLink を使用したサード・パーティ・シミュレーション・ツールのシミュレーションシミュレーションは、NativeLink を使用して Quartus II ソフトウェアからサード・パー

ティ製シミュレーション・ツールを使用して実行できます。

Tcl スクリプト・ファイル <variation name>_nativelink.tcl を使用して、デフォルトの

NativeLink テストベンチ設定を Quartus II プロジェクトに割り当てることができます。

Quartus II ソフトウェアで NativeLink を使用してシミュレーションを実行するには、以

下のステップを実行します。

1. この章で前述した手順に従って、カスタム MegaCore ファンクションのバリエー

ションを作成します。バリエーション名が Quartus II プロジェクト名と一致して

いるか確認します。

2. Quartus II ソフトウェアの Tools メニューの Options ページに、サード・パーティ

製 EDA ツールへの絶対パスが設定されているかチェックします。

3. Processing メニューから Start を選択し、Start Analysis & Elaboration をクリックし

ます。

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 2 章 : 使用法 2‒11MegaWizard Plug-In Manager フロー

4. Tools メニューの Tcl scripts をクリックします。Tcl Scripts ダイアログ・ボックス

で <variation name>_nativelink.tcl を選択して、Run をクリックします。 Tcl スクリプ

トが正常にロードされたことを確認するメッセージをチェックします。

5. Assignments メニューの Settings をクリックして、EDA Tool Settings を展開し、

Simulation を選択します。 Tool Name でシミュレータを選択し、NativeLink Settingsで Compile Test Bench を選択して、Test Benches をクリックします。

6. Tools メニューで EDA Simulation Tool をポイントして、Run EDA RTL Simulation を

クリックします。

Quartus II ソフトウェアは、シミュレータを選択し、アルテラのライブラリ、デザ

イン・ファイル、およびテストベンチをコンパイルします。テストベンチが実行

して、波形ウィンドウには、分析のためのデザイン・シグナルを示します。

f 詳細は、「Quartus II HandbookVolume 3」の「Simulating Altera Designs」の章を参照して

ください。

デザインのコンパイルおよびデバイスのプログラムQuartus II ソフトウェアを使用して、デザインをコンパイルすることができます。

デザインをコンパイルした後、ターゲットのアルテラ・デバイスをプログラムし、

ハードウェアでデザインを検証します。

f デザインのコンパイルとプログラミングのインストラクションおよび MegaWizard Plug-In Manager について詳しくは、「Quartus II Help」を参照してください。

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

2‒12 第 2章 : 使用法MegaWizard Plug-In Manager フロー

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

© 2011 年 5月 Altera Corporation

3. パラメータの設定

この章では、FIR コンパイラ MegaCore ファンクションをパラメータ化する方法の例

を提供して、使用可能なパラメータについて説明します。

Parameterize - FIR Compiler のページでは、DSP Builder または MegaWizard Plug-In Manager のフローから開いているかどうか、同じオプションを提供します。

パラメータ化の開く方法について詳しくは、2–1 ページの「デザイン・フロー」を参

照してください。

1 ユーザー・インタフェースは、パラメータの適正な組み合わせのみの選択を可能に

し、無効なパラメータの組み合わせに対しては警告を出します。

係数の指定FIR フィルタは係数で定義されます。FIR コンパイラの係数設定方法には、以下のオ

プションがあります。

■ FIR コンパイラを使用して、係数を生成することができます。係数生成機能は、

シングル・レート、補間、およびデシメーション・レート仕様のフィルタ・タイ

プをサポートしています。これらのフィルタ・タイプの係数を生成する方法につ

いて詳しくは、 3–3 ページの「FIR コンパイラを使用した係数生成機能」を参照し

てください。

■ ファイルから係数をロードすることができます。例えば、MATLAB、SPW、また

はユーザーが作成したプログラムなどの別のアプリケーションで係数を作成し、

ファイルに保存して FIR コンパイラにインポートすることができます。詳細は、 3–7 ページの「ファイルから係数のロード」を参照してください。

3–2 ページの図 3–1 に、Parameterize - FIR Compiler ページを示します。

FIR コンパイラ ユーザーガイド

3‒2 第 3 章 : パラメータの設定係数の指定

このページでは、New Coefficient Set をクリックして新しい係数を定義するまたは

ロードすることができます。 あるいは、Edit Coefficient Set をクリックしてデフォルト

の係数セットを編集し、または Remove Coefficient Set をクリックして現在のロード

されている係数を削除することができます。

図3‒1. IP Toolbench Parameterize のページ

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 3 章 : パラメータの設定 3‒3係数の指定

FIR コンパイラを使用した係数生成機能1. Parameterize - FIR Compiler ページでは、New Coefficient Set をクリックして、

Coefficients Generator Dialog ボックスを開きます。

このダイアログ・ボックスを使用して、フィルタ・タイプ、ウィンドウ・タイ

プ、サンプル・レート、Excess Bandwidth(コサイン・フィルタで使用)などの多

くのパラメータを指定することができます。

3–3 ページの図 3–2 に、ロー・パス・フィルタのデフォルト値を示します。

2. シンプルなパラレル・フィルタの係数を生成するには、Coefficients Generator Dialog ボックスを使用して、表 3–1 に示す設定のリストを作成します。

図3‒2. デフォルトのロー・パス・フィルタのパラメータが表示された Coeffic ients Generator Dialog ボックス

表3‒1. シンプルなパラレル・フィルタに対する係数生成機能のパラメータ設定

パラメータ 値

レートの仕様 シングル・レート e

フィルタ・タイプ Band Pass

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

3‒4 第 3 章 : パラメータの設定係数の指定

3. 設定を作成した後、 Apply をクリックしてください。 ダイアログボックスには、青

色のフィルタの周波数応答を表示し、また実際の係数値のリストが表示されます

(図 3–3)。

係数 77

Cutoff Freq. 1 5e+006

ウィンドウ・タイプ Hamming

Sample Rate: 50e+006

Cutoff Freq. 2 10e+006

表3‒1. シンプルなパラレル・フィルタに対する係数生成機能のパラメータ設定

パラメータ 値

図 3‒3. Band Pass フィルタに対するパラレル FIR フィルタの係数パラメータ

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 3 章 : パラメータの設定 3‒5係数の指定

4. 補間またはデシメーションの浮動小数点の係数を生成するには、Output Specification ドロップダウン・ボックスで、Interpolation または Decimation、およ

び必要な Factor を選択します。

Auto Generate をクリックすると、IP Toolbench は、指定されたレートに基づいて、

遮断周波数を持つロー・パス・フィルタの係数を生成します。

3–5 ページの図 3–4 に、デシメーション・フィルタを示します。遮断周波数はサ

ンプリング・レートとハーフ・バンドの係数セットの結果の 4 分の 1 です。

補間およびデシメーションについて詳しくは、4–9 ページの「補間およびデシ

メーション」を参照してください。

5. パラメータ設定の作成が終了したら、OK をクリックします。

Parameterize - FIR Compiler のページ ( 3–2 ページの図 3–1)が更新されて、浮動

係数での周波数応答を青色で表示し、固定係数での周波数応答を緑色で表示しま

す。

Time Response & Coefficient Values タブをクリックして、3–6 ページの図 3–5 に示

すように、係数を表示します。

図3‒4. インターポレーション・フィルタのロー・パス・フィルタの結果

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

3‒6 第 3 章 : パラメータの設定係数の指定

図3‒5. IP Toolbench での Parameterize ページおよび Time Response and Coeffic ient Values タブ

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 3 章 : パラメータの設定 3‒7係数の指定

ファイルから係数のロードファイルから係数セットをロードするには、以下のステップに従います。

1. Parameterize - FIR Compiler のページ ( 3–2 ページの図 3–1)で、New Coefficient Set をクリックして、Coefficients Generator Dialog ボックス( 3–7 ページの図 3–6)の Imported Coefficient Set を選択します。

2. ファイル・システム内に、使用するファイルに移動し、 Open をクリックします。

係数ファイルが個別回線上に各係数が必要であり、ファイルの終わりに改行が必

要ではありません。 科学的な表記法として、浮動小数点または固定小数点数を使

用することができます。

図3‒6. 係数セットのインポート

図3‒6 の注:(1) Floating Coefficient Setおよび Imported Coefficient Set のパラメータのラジオ・ボタンが相互にリンクしているため、1つを選択す

ると、もう片方が無効にされます。

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

3‒8 第 3 章 : パラメータの設定係数の解析

1 ファイルの終わりに追加の改行を挿入しないでください。FIR コンパイラ

は、 近の過去の係数値を持つ追加の係数として各キャリッジ・リターン

を解釈します。ファイルには、5 つの 0 でない係数の 小値を持つ必要が

あります。

3. OK をクリックして係数セットをインポートします。

係数の解析FIR コンパイラでは、係数の解析ツールが含まれています。係数のセットを作成し、

各セットに処理を実行するにはそれをできます。

スケーリングなどのいくつかの動作は、すべてのセットに適用されます。再作成、

リロード、または削除などの他の動作は、現在表示しているセットに適用されます。

FIR コンパイラは 大 16 セットの係数をサポートします。Parameterize - FIR Compilerのページには、係数タブを使用して、セットを切り替えることができます。 (係数

セットは番号が付けられます。例えば、 Low Pass Set 1、 Low Pass Set 2 など。)

係数セットを選択すると、浮動小数点係数での周波数応答を青色で表示し、固定小

数点係数での周波数応答を緑色で表示します。また、Time Response & Coefficient Values をクリックして、実際の係数値も表示できます。

FIR コンパイラは、フィルタリング時に、どのビットが保持されるか、およびどの

ビットが削除されるかをモニタするために、符号付きバイナリ小数表記法の 2 の補

数をサポートします。符号付きバイナリ小数は次のフォーマットをしています。

<sign> <integer bits>.<fractional bits>

符号付きバイナリ小数は以下に示すとおり、解釈されます。

<sign> <x1 integer bits>.<y1 fractional bits> オリジナルの入力データ

<sign> <x2 integer bits>.<y2 fractional bits> オリジナルの係数データ

<sign> <i integer bits>.<y1 + y2 fractional bits> FIR 計算後のフル精度

<sign> <x3 integer bits>.<y3 fractional bits> 精度を制限した後の出力データ

ここで、i = ceil(log2(number of coefficients)) + x1 + x2

例えば、3 分数ビットと 4 の整数ビット + 符号ビットを持っている数の場合は、全体

の 8 ビットの整数は 8 によって分割されて、バイナリ小数部を持つ数値が得られま

す。

1 DSP Builder は符号ビットを整数ビットの一部として取り込みます。したがって、DSP Builder デザインで FIR フィルタを使用している場合は、DSP Builder は、追加の整数

のビットとして符号ビットを認識します。

10 進数に変換すると、特定の小数部分は、バイナリビットの無限の数を持っていま

す。例えば、10 進数に 1 /3 を変換することで、0.333n(n は 3 秒の無限の数を表す)

が得られます。同様に、完全な精度で有限数のバイナリー・ディジットで 1/10 など

の数を表すことができません。符号付きバイナリ小数表記法を使用する場合、FIR コ

ンパイラは選択された精度のビット数を持つオリジナルの数字に も近い数を使用

します。

このチュートリアルには、Coefficients Scaling のために Auto を選択し、Coefficient Bit Width のために 12 を選択してください。

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 3 章 : パラメータの設定 3‒9係数の解析

1 Auto スケーリングは、 大の信号対ノイズ比を提供します。Signal Binary Fractional など他のすべてのスケーリングでは、有効ビットが失われることがあります。

図 3–7 に、選択した後の結果を示します。ビット幅を 8(デフォルト)から 12 に変

更すると、固定小数点周波数応答のサイド・ローブが減少することに注意してくだ

さい。

図3‒7. 係数の解析

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

3‒10 第 3 章 : パラメータの設定入力および出力仕様の指定

入力および出力仕様の指定Parameterize - FIR Compiler ページで、Number of Input Channels(すなわち、各スト

リームに出力を生成するデータ・ストリーム数)および Input Number System を指定

できます(図 3–7)。

FIR コンパイラは、実際の係数または係数ビット幅の 2 つの手法を使用したフル解像

度に対してフィルタが必要とするビット数を計算します。これらのパラメータは正

および負の 大出力値を定義します。Output Specification ドロップダウン・ボックス

で、Bit Width Only または Actual Coefficients を選択します。 FIR コンパイラは、演算結

果を表わすのに必要なビット数を推定します。完全精度(Full Precision)を実現する

には、推定されたビット数をシステムで使用する必要があります。

1 フィルタに係数のリロードまたは複数の係数セットが存在する場合、Bit Widths Onlyを選択する必要があります。

フィルタされた出力(out)に対して完全または制限付き精度を使用することができ

ます。完全な精度を使用するには、Output Number System を Full Resolution(デフォル

ト)に設定します。精度を制限するには、ドロップ・ダウン・ボックスで、Custom Resolution または Signed Binary Fractional を選択します。

Output Number System が Custom Resolution に設定されているときは、 上位ビット

(MSB)を切り捨てまたは飽和処理するオプション、および 下位ビット(LSB)を

丸め処理または切り捨て処理するオプションを選択できます。飽和、切捨て、およ

び丸め処理は非線形操作です。

表 3–2 にフィルタの精度を制限するオプションを示します。

表3‒2. 精度を制限するオプション

ビット範囲

オプション 結果

MSB 切り捨て 切り捨て処理では、フィルタは指定されたビットを無視します (図 3–8)。

飽和 飽和処理では、フィルタされた出力が表示可能な正または負の大値より大きい場合、出力は正または負の 大値に強制(すなわち、飽和処理)されます。

LSB 切り捨て MSB の場合と同じ処理です。

丸め 出力は丸められます。

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 3 章 : パラメータの設定 3‒11アーキテクチャ仕様の指定

図 3–8 に MSB および LSB からのビットの削除例を示します。

あるいは、Signed Binary Fractional 表記を選択し、保存するビット数を指定すること

ができます。FIR コンパイラは削除するビット数を表示します。

入力および出力仕様を調整するには、以下のステップを実行します。

■ MSB から切り捨てると、飽和以上にロジック・リソースが減少します。

■ Number of Input Channelsオプションは、IおよびQチャネルを持つモジュレータおよ

びデモジュレータなどのデザインに役立ちます。このタイプのアプリケーション

をデザインする場合は、2 を選択してください。このチュートリアルではデフォ

ルトの設定を使用します。

アーキテクチャ仕様の指定これで、Parameterize - FIR Compiler ページの下半分からアーキテクチャ・パラメー

タを選択できます。

FIR コンパイラは、以下を含むフィルタ構造をサポートします。

■ 固定 / 可変係数:マルチサイクル

■ 汎用ロジックを使用した演算器:完全パラレル・フィルタ

■ 汎用ロジックを使用した演算器: 完全シリアル・フィルタ

■ 汎用ロジックを使用した演算器:マルチ・ビット・シリアル・フィルタ

1 大クロック速度は、汎用ロジックを使用した演算器: 完全シリアル・フィルタ構

造を選択します。(Stratix、Stratix II、Stratix III、または Stratix IV デバイスに関しては、

係数とデータ保存により小さいメモリ・リソースを使用するのは、より大きいメモ

リ・リソースを使用するより速いです。) 大のスループットを得るには、汎用ロ

ジックを使用した演算器:完全パラレル・フィルタ構造を選択します。

係数をリロードするときに、マルチサイクル FIR フィルタの構造は、固定 FIR フィル

タに比べて短いリロード時間を持っています。さらに、より小さいメモリ・ブロッ

クは、大きなメモリ・ブロックよりも短いリロード時間を持っています。

図3‒8. MSB および LSB からのビットの削除

D15D14D13D12D11D10D9D8..D0

D9D8..D0

Bits Removed from MSB

FullPrecision

LimitedPrecision

D15D14....D4D3D2D1D0

D11D10...D1D0

Bits Removed from LSB

FullPrecision

LimitedPrecision

D15D14D13D12...D3D2D1D0

D10D9...D1D0

Bits Removed from both MSB & LSB

FullPrecision

LimitedPrecision

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

3‒12 第 3 章 : パラメータの設定アーキテクチャ仕様の指定

表 3–3 に、異なるアーキテクチャのオプションのためのトレードオフの相対を説明

します。

フィルタのアーキテクチャの動作方法について詳しくは、 4–1 ページの「FIR コンパ

イラ」を参照してください。

表3‒3. アーキテクチャのトレードオフ

テクノロジ オプション 領域 スピード (データ・スループット)

汎用ロジックを使用した演算器

完全パラレル

面積(大) 高速フィルタの作成:Stratix II デバイスでパイプライン化により 140 から 300 超の MSPS スループット。

汎用ロジックを使用した演算器

完全シリアル

面積(小) 1 回の演算に複数のクロック・サイクルが必要です。

汎用ロジックを使用した演算器

マルチ・ビット・シリアル

面積(中) 複数のシリアル・ユニットを使用してスループットを向上させます。これによりスループットは完全シリアルより高く、完全パラレルより低くなります。

DSP ブロックのマルチプライヤ

マルチサイクル

面積は選択した計算サイクル数に依存します(計算サイクル数が増加すると面積も増加します)

計算サイクル数が減少するとデータ・スループットは向上します。このアーキテクチャでは、Stratix、 Stratix II、 Stratix III、 または Stratix IV DSP ブロック、および CycloneII 乗算器を活用しています。

すべてのアーキテクチャで使用可能なオプション

パイプライニング

面積の増加とより高い性能のフィルタを作成します。

追加のレイテンシとサイズの増加に伴ってスループットを向上させます。

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 3 章 : パラメータの設定 3‒13アーキテクチャ仕様の指定

表 3–4、表 3–5、表 3–6、および表 3–7 に、各アーキテクチャに使用可能な FIR コン

パイラのオプションを説明します。

表3‒4. マルチサイクル・フィルタ・アーキテクチャ ( 注 1)

パラメータ 説明

計算するクロック 結果を計算するために必要なクロックサイクル数を指定します。結果を計算するために多くのクロック・サイクルを使用すると、フィルタのリソース使用量を減らすことができます。フィルタが使用する乗算器の数は、結果を計算するために、クロック・サイクル数で割ったタップ数に等しくなります。

データ・ストレージ

データ・ストレージで使用されるデバイス・リソースを指定します。Logic Cells、 M512、 M4K、 M-RAM、 MLAB、 M9K、 M144K、または Auto を選択できます。Auto を選択すると、選択したデバイスのリソース、データ・ストレージのサイズ、および入力チャネル数に応じて、Quartus Ⅱソフトウェアがデータをロジック・セルまたはメモリに保存することができます。

オプション・リストは、選択するデバイスおよび結果の計算に使用するクロック・サイクル数に応じて変化します。エンベデッド・メモリを選択すると、ロジック・セルの利用率が低下し、フィルタの速度を向上させることができます。

係数の保存 係数の保存で使用されるデバイス・リソースを指定します。Logic Cells、 M512、 M4K、 M-RAM、 MLAB、 M9K、または Auto を選択できます。Auto を選択すると、Quartus II ソフトウェアは自動的に選択したデバイスのための も適切なメモリ・ブロックのサイズを選択します。

オプション・リストは、選択するデバイスおよび結果の計算に使用するクロック・サイクル数に応じて変化します。エンベデッド・メモリを選択すると、ロジック・セルの利用率が低下し、フィルタの速度を向上させることができます。

乗算器の実装 乗算器の実装を使用されるデバイス・リソースを指定します。Logic Cells、 DSP Blocks、 または Auto を選択できます。Auto を選択すると、Quartus II ソフトウェアは DSP Block Balancing ロジック・オプションをオンにします。

エンベデッド DSP ブロックを使用すると、DSP ブロックを活用した小型で高速なデザインを実現します。DSP ブロックの も効率的な使用は、9 × 9(8 つのグループで)または 18×18(4 のグループで)乗算のためです。

Force Non-Symmetric Structure(アシンメトリック構造の強制)

シンメトリック係数およびアシンメトリック係数の両方を使用するデザインを作成する場合は、このオプションをオンにします。

シンメトリック・アーキテクチャでは、リソース使用を低減させることが可能です。

係数のリロード 係数をリロードできるようにするには、このオプションをオンにします。

パイプライン・レベル

このオプションをオンにすると、FIR コンパイラはより多くのデバイス・リソースを使用してより高い性能のフィルタを作成します。

シングル・クロック

DSP Builder でデザインを作成するときに、このオプションを使用します。Coefficients Reload がオンであるときに、そして、M512、M4K、MLAB または M9K が Coefficient Storage で指定されるときにだけ、このオプションは利用可能です。

このオプションは、coef_clk_inと clk信号を結び付けます。

表3‒4の注: (1) 入力データが符号なしの場合、入力データのビット幅は 1以上でなければなりません。入力データが符号付きの場合、入力

データのビット幅は 2以上でなければなりません。

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

3‒14 第 3 章 : パラメータの設定アーキテクチャ仕様の指定

表3‒5. 完全シリアル・フィルタ・アーキテクチャ ( 注 1)

パラメータ 説明データ・ストレージ

データ・ストレージで使用されるデバイス・リソースを指定します。 Logic Cells、 M512、 M4K、 M-RAM、 MLAB、 M9K、 M144K、または Auto を選択できます。Auto を選択すると、選択したデバイスのリソース、データ・ストレージのサイズ、および入力チャネル数に応じて、Quartus II ソフトウェアがデータをロジック・セルまたはメモリに保存することができます。

係数の保存 係数の保存で使用されるデバイス・リソースを指定します。Logic Cells、 M512、 M4K、 M-RAM、 MLAB、 M9K、または Auto を選択できます。Auto を選択すると、Quartus II ソフトウェアは自動的に選択したデバイスのための も適切なメモリ・ブロックのサイズを選択します。

オプション・リストは、選択するデバイスに応じて変化します。エンベデッド・メモリを選択すると、ロジック・セルの利用率が低下し、フィルタの速度を向上させることができます。

Force Non-Symmetric Structure(アシンメトリック構造の強制)

シンメトリック係数およびアシンメトリック係数の両方を使用するデザインを作成する場合は、このオプションをオンにします。

シンメトリック・アルゴリズムは計算サイクルごとに追加クロック・サイクルを必要とし、それによりスループットが低下します。

係数のリロード 係数を変化する場合、このオプションをオンにします。係数を変化する場合、このオプションをオンにします。データ・ストレージで使用されるデバイス・リソースを指定します。

このオプションを選択するとリソース使用量が増加し、複数の 適化手法がオフになり、フィルタに入力ポートが追加されます。

パイプライン・レベル

リソース使用量の増加とより高い性能のフィルタを作成します。

シングル・クロック

DSP Builder でデザインを作成するときに、このオプションを使用します。Coefficients Reload を選択するとき、そして、M512、M4K、MLAB または M9K が Coefficient Storageで指定されるときにだけ、このオプションは利用可能です。

このオプションは、coef_clk_inと clk信号を結び付けます。

表3‒5の注:(1) 入力データのビット幅は 4以上でなければなりません。

表3‒6. マルチビット・シリアル・フィルタ・アーキテクチャ ( その1 ) ( 注 1)

パラメータ s 説明

シリアル・ユニット数

フィルタを行うために必要なシリアルユニット数を指定します。2、 3、 または 4 を選択できます。各結果の計算サイクルは、対応するシリアル・フィルタの一つの n 番目に減少しています。ここで、n はシリアル・ユニット数です。これに対応し、リソース使用量の増加があります。

データ・ストレージ

データ・ストレージを使用されるデバイス・リソースを指定します。 Logic Cells、 M512、 M4K、 M-RAM、 MLAB、 M9K、 M144K、または Auto を選択できます。 Auto を選択すると、選択したデバイスのリソース、データ・ストレージのサイズ、および入力チャネル数に応じて、Quartus Ⅱソフトウェアがデータをロジック・セルまたはメモリに保存することができます。

マルチレート(補間またはデシメーション)を選択するかどうか、および選択するデバイスに応じてオプションのリストを変更します。エンベデッド・メモリを選択すると、ロジック・セルの利用率が低下し、フィルタの速度を向上させることができます。

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 3 章 : パラメータの設定 3‒15アーキテクチャ仕様の指定

係数の保存 係数の保存で使用されるデバイス・リソースを指定します。Logic Cells、 M512、 M4K、 M-RAM、 MLAB、 M9K、または Auto を選択できます。Auto を選択すると、Quartus II ソフトウェアは自動的に選択したデバイスのための も適切なメモリ・ブロックのサイズを選択します。

オプション・リストは選択するデバイスに応じて変化します。エンベデッド・メモリを選択すると、ロジック・セルの利用率が低下し、フィルタの速度を向上させることができます。

Force Non-Symmetric Structure(アシンメトリック構造の強制)

シンメトリック係数およびアシンメトリック係数の両方を使用するデザインを作成する場合は、このオプションをオンにします。

シンメトリック・アルゴリズムは計算サイクルごとに追加クロック・サイクルを必要とし、それによりスループットが低下します。

係数のリロード 係数を変化する場合、このオプションをオンにします。このオプションはエンベデッド・メモリに係数を保存するときに使用できます。

このオプションを選択するとリソース使用量が増加し、複数の 適化手法がオフになり、フィルタに入力ポートが追加されます。

パイプライン・レベル

リソース使用量の増加とより高い性能のフィルタを作成します。

シングル・クロック

DSP Builder でデザインを作成するときに、このオプションを使用します。Coefficients Reload を選択するときに、そして、M512、M4K、MLAB または M9K が Coefficient Storage で指定されるときにだけ、このオプションは利用可能です。

このオプションは、coef_clk_inと clk信号を結び付けます。

表3‒6の注:(1) 入力データのビット幅はシリアル・ユニット数で均等に分割する必要があり、除算の結果は 4以上でなければなりません。

表3‒7. 完全パラレル・フィルタ・アーキテクチャ ( その1 ) ( 注 1)

パラメータ 説明

データ・ストレージ

データ・ストレージで使用されるデバイス・リソースを指定します。Logic Cells または Auto を選択できます。 Auto を選択すると、選択したデバイスのリソース、データ・ストレージのサイズ、および入力チャネル数に応じて、Quartus II ソフトウェアがデータをロジック・セルまたはメモリに保存することができます。

係数の保存 係数の保存で使用されるデバイス・リソースを指定します。Logic Cells、 M512、 M4K、MLAB、 M9K、または Auto を選択できます。 Auto を選択すると、Quartus II ソフトウェアは自動的に選択したデバイスのための も適切なメモリ・ブロックのサイズを選択します。

オプション・リストは選択するデバイスに応じて変化します。エンベデッド・メモリを選択すると、ロジック・セルの利用率が低下し、フィルタの速度を向上させることができます。

Force Non-Symmetric Structure(アシンメトリック構造の強制)

シンメトリック係数およびアシンメトリック係数の両方を使用するデザインを作成する場合は、このオプションをオンにします。シンメトリック・アーキテクチャでは、リソース使用を低減させることが可能です。

このオプションはエンベデッド・メモリに係数を保存するときに使用できます。

係数のリロード 係数を変更する場合は、このオプションをオンにします。このオプションはエンベデッド・メモリに係数を保存するときに使用できます。

このオプションを選択するとリソース使用量が増加し、複数の 適化手法がオフになり、フィルタに入力ポートが追加されます。

表3‒6. マルチビット・シリアル・フィルタ・アーキテクチャ ( その2 ) ( 注 1)

パラメータ s 説明

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

3‒16 第 3 章 : パラメータの設定アーキテクチャ仕様の指定

パイプライン・レベル

リソース使用量の増加とより高い性能のフィルタを作成します。

シングル・クロック

DSP Builder でデザインを作成するときに、このオプションを使用します。Coefficients Reload を選択するときに、そして、M512、M4K、MLAB または M9K が Coefficient Storage で指定されるときにだけ、このオプションは利用可能です。

このオプションは、coef_clk_inと clk信号を結び付けます。

表3‒7の注:(1) 入力データが符号なしの場合、入力データのビット幅は 1以上でなければなりません。入力データが符号付きの場合、入力

データのビット幅は 2以上でなければなりません。

表3‒7. 完全パラレル・フィルタ・アーキテクチャ ( その2 ) ( 注 1)

パラメータ 説明

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 3 章 : パラメータの設定 3‒17アーキテクチャ仕様の指定

1. このチュートリアルでは、3 のパイプライン・レベルの Distributed Arithmetic: Fully Parallel Filter 構造を選択します。

これらの設定は、ロジック・セルを多数使用したフィルタを作成していますが、

3 にパイプラインのレベルを増加させるとクロック・サイクル数は 1 に減少させ

ます。これにより、大幅にシステムのパフォーマンスが向上します。これらの設

定を図 3–9 に示します。

2. アーキテクチャ・パラメータをセットすると、Finish をクリックします。

図3‒9. フィルタ・アーキテクチャの指定

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

3‒18 第 3 章 : パラメータの設定推定リソース

推定リソースFIR コンパイラは自動的に、Architecture Specification セクション(Parameterize FIR Compiler ページ)の Resource Estimates ボックスに使用する推定リソースを計算して

表示します。

FIR コンパイラは、エンベデッド・メモリ・ブロック、DSP ブロック、およびロジッ

ク・セルに推定されたサイズを提供します。 Throughput ボックスは、結果の計算に使

用するクロック・サイクル数を表示します(図 3–10)。

1 リソース使用量の推定値は、Quartus II ソフトウェアで使用するどの 適化手法に応

じて、 Quartus II リソースの使用状況の +/-30%と異なる場合があります。さらに、

リソースの推定量は小さなフィルタ(500 ロジック・セル以下)のための精度が低く

なります。小さなフィルタは、リソース使用量を取得するのに Quartus II 開発ソフト

ウェアでデザインをコンパイルします。

フィルタ・デザインのヒントここでは、FIR コンパイラを使用した追加のヒントを提供します。

■ ハイパス・フィルタがナイキストの近くで転がり落ちるのを防ぐには、タップの

奇数を選択します。

■ 係数は、テキスト・ファイルを通じて MATLAB ソフトウェアから FIR コンパイラに

インポートすることができます。単に係数は、1 行に 1 つの係数で、ASCII ファイ

ルへの固定または浮動小数点数として保存します。

■ QPSK(Quadrature phase shift keying:四位相偏移変調)、QAM(Quadrature amplitude modulation:直交振幅変調)、または FIR コンパイラを使用した位相偏移変調

(PSK)モジュレータやデモジュレータを作成するには、入力仕様のエリアに 2 つ

以上のチャネルを示すことでマルチ・チャンネル・フィルタを作成します。

■ 櫛形フィルタは、反復ノッチを持つフィルタです。櫛形フィルタを作るには、

初、シングル・ノッチ・フィルタを作るし、サブサンプリングを使用します。サ

ブサンプリングのプロセスは、ナイキスト上記のすべての周波数で周波数領域で

のノッチを反映またはミラーリングします。

図3‒10. 推定リソース

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 3 章 : パラメータの設定 3‒19フィルタ・デザインのヒント

■ 浮動小数点係数をインポートするときは、固定小数点整数の番号を生成するス

ケーリング係数を適用する必要があります。係数は も近い整数に丸めているの

で、スケーリング(またはゲイン)係数は、ゼロ(それが小さすぎる場合)に設

定することができます。適切な係数をスケーリングしない場合、多くのゼロがあ

るフィルタを持つことができます。

■ 高のスループットのフィルタは、クロック・サイクルごとに出力を生成する拡

張パイプラインのパラレル・フィルタです。

■ アルテラでは、面積を減らすためにメモリ・ブロックを使用することを推奨しま

す。

■ FIR フィルタは、次の制約が設定されている場合、通常より高い fmax で動作しま

す。

set_global_assignment -name "PHYSICAL_SYNTHESIS_COMBO_LOGIC" "ON"set_global_assignment -name "PHYSICAL_SYNTHESIS_REGISTER_RETIMING" "ON"

■ Standard Fit ( 高エフォート)が 適な合成結果を得るために、Quartus II ソフト

ウェアのフィッタ設定を推奨します。

■ デシメーション・ハーフ・バンドに 適化されたアーキテクチャを有効にするに

は、データ・ストレージおよび係数の保存を利用可能なブロック・メモリの Autoまたは 1 のいずれかに設定する必要があります。次、奇数になるのフィルタ・

タップ数を選択します。係数セットは対称でなければならず、他のすべての係数

の値は 0 であるはずです。

■ 対称補間に 適化されたアーキテクチャを有効にするには、データ・ストレージ

および係数の保存を利用可能なブロック・メモリの Auto または 1 のいずれかに

設定する必要があります。タップ数が奇数の値である必要があります。現在だけ

でも、対称性がサポートされています。

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

3‒20 第 3 章 : パラメータの設定フィルタ・デザインのヒント

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

© 2011 年 5月 Altera Corporation

4. 機能の説明

FIR コンパイラFIR コンパイラは、ウィザードで対話的に操作するインタフェースを備えており、カ

スタム FIR フィルタを簡単に作成できます。ウィザードは、Verilog HDL および VHDLシミュレータで使用する IP 機能シミュレーション・モデル・ファイルを出力しま

す。

数のシステムと固定小数点精度FIR コンパイラ機能は 2 の補数で 4 から 32 までのビット幅の符号付きまたは符号な

し固定小数点数および符号付きバイナリ小数のフォーマットをサポートします。

フィルタ全体は単一数体系で動作します。係数の精度は、入力データ幅とは無関係

であるため、出力精度を任意に設定できます。

係数の生成またはインポート係数は、FIR コンパイラ機能を使用して作成するか、または MATLAB のような別のア

プリケーションを使用して作成し、ASCII ファイルとして保存して FIR コンパイラで

読み込むことができます。

係数は浮動小数点または整数で表し、1 行に 1 つの係数をリストしてください。

1 係数に負の値を指定すると、FIR コンパイラは符号付きの 2 の補数を生成します。

図 4–1 に、係数テキスト・ファイルの内容の一例を示しています。

FIR コンパイラは、以下のフィルタの係数(タップ数はユーザーが指定)を自動的に

生成します。

■ ロー・パス

■ ハイ・パス

■ バンド・パス

Figure 4‒1. フィルタ係数のサンプル-3.09453e-005-0.000772299-0.00104106-0.0002578450.00150377...0.001631250.002785060.00150377-0.000257845-0.00104106-0.000772299-3.09453e-005

FIR コンパイラ ユーザーガイド

4‒2 第 4 章 : 機能の説明FIR コンパイラ

■ バンド・リジェクト

■ 累乗コサイン

■ ルート累乗コサイン

■ ハフ・バンド(ロー・パス)

タップ数、カット・オフ周波数、サンプル・レート、フィルタ・タイプ、および

ウィンドウ・メソッドを調整することによって、カスタム周波数応答を構築するこ

とができます。設定を適用するたびに、FIR コンパイラは係数値を計算し、対数ス

ケールに周波数応答を表示します。係数は浮動小数点の数値であるため、スケーリ

ングを行い固定小数点に変換します。

値は、Coefficients Generator Dialog ページの Coefficients スクロール・ボックスに表示

されます。 3–3 ページの図 3–2 を参照してください。

FIR コンパイラは係数で読み込むとき、それは自動的に対称性を検出します。フィル

タは、いくつかのスケーリングのオプションを提供します。例えば、指定された

ビット数のスケーリングまたはユーザー指定の係数でのスケーリングです。

スケーリングされた係数は Parameterize FIR Compiler ページの Time Response & Coefficient Values タブで表示されます。3–6 ページの図 3–5 を参照してください。

係数のスケーリング係数値は通常、浮動小数点の数値で表されています。これを固定小数点系に変換す

るには、係数をスケーリング・ファクタで乗算し、丸められます。FIR コンパイラ

は、5 種類のスケーリング・オプションを提供しています。

■ Auto scale to a specified number of precision bits—係数の 大値が指定されたビット数

で表現できる 大値となるよう、スケーリング・ファクタが設定されます。これ

により、指定されたビット数内での係数の量子化誤差を 小にすることができま

す。これにより、指定されたビット数内での係数の量子化誤差を 小にすること

ができます。

■ Auto with a power of 2— このアプローチでは、FIR コンパイラは、分解能ビットの特

定の数の中で 大の数値を表すことができる 2 つのスケーリング・ファクタの

大電力を選択します。特定のゲイン・ファクタで係数のすべてを乗算すると、

FIR フィルタの前にゲイン・ファクタを追加するのと同じです。これにより、ス

ケーリング・ファクタをフィルタ出力から取り除くのはビット・シフトで行えま

す。

■ Manual— 指定したゲイン・ファクタで係数値をマニュアルでスケーリングするこ

とができます。

■ Signed binary fractional—小数点のいずれかのサイドで使用する桁数を指定すること

ができます(Variable アーキテクチャでのみサポートされる)。

■ None— 係数をスケーリングされた値とみなし、スケーリング・ファクタを適用し

ません。

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 4 章 : 機能の説明 4‒3FIR コンパイラ

シンメトリカル・アーキテクチャの選択多くの FIR フィルタは、シンメトリカルな係数値を持っています。FIR コンパイラ

は、係数を検査して、フィルタの対称性(偶数、奇数、なし)を自動的に判定しま

す。フィルタの対称性が検出されると、必要な計算を 小限に抑えるため、ウィ

ザードが 適なアルゴリズムを選択します。FIR コンパイラは、係数は四捨五入され

た後に係数の対称性を決定します。対称性が存在する場合、2 つのデータ・ポイント

は、前の乗算のステップに追加されて、乗算演算を保存します(フィルタの対称性

の利点を取ることは約半分で乗算器の数を減らすことができる)。

1 ウィザードでは、非対称構造を強制するオプションを提供します。対称性が 適化

されたアーキテクチャが利用できない場合は、このオプションは無効になっていま

す。

奇数フィルタおよび偶数フィルタの構造は 図 4–1 および図 4–2 に示します。

対称的なシリアル対称的なシリアル・フィルタでは FIR の計算(そのフィルタはキャリーを計算する

ことができる)を実行するために追加クロック・サイクルが必要です。追加のロ

ジック・セルは対称加算器のリソースに必要です。

非対称シリアル FIR フィルタは、このリソースを必要としないので、非対称フィル

タは小さいおよび / または高速な場合があります。

図4‒1. 7 タップのシンメトリカル FIR フィルタ

Data In

Data Out

Z -1

C0

Z -1

C1 C2 C3

Z -1

Z -1

Z -1

Z -1

Z -1

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

4‒4 第 4 章 : 機能の説明FIR コンパイラ

利用可能な 善のソリューションを決定するために、Parameterize FIR Compiler ペー

ジの Architecture Specification エリアでの Resource Estimator を使用できます。3–17ページの図 3–9 を参照してください。

係数リロードおよびリオーダリングすべての FIR コンパイラ構造は、複数の係数セットを可能にして、フィルタが動的

に係数セットを切り替えることができます。さらに、フィルタが 1 つの係数セット

を使用しているときに、他のセットを更新できます。したがって、フィルタは、係

数セットの無限の数を切り替えることができます。

係数は、シリコンの効率を 大化するために、正規の順序で格納されていません。

リオーダリングは初期デザインの時に自動的に実行されます。しかし、フィルタ係

数はリロード可能である場合、フィルタ動作中に任意の新しい係数セットをリロー

ドする時に、リロードする前にリオーダする必要がありますが係数のリオーダする

ために使用できる C++ プログラムが提供されています。 Windows 用のコンパイル済み

の実行ファイルも提供されています。

プログラムは <install path>\fir_compiler\misc に見つけることができます。C++ ソース・

コード・ファイルの名前は coef_seq.cpp で、実行可能なプログラム(Windows オペ

レーティング・システム用)の名前は coef_seq.exe です。 係数生成プログラムにソー

ス・コードを追加したり、係数をリオーダする実行可能ファイルを使用することが

できます。

coef_seq.exe を使用するコマンドは、次の通りです。

coef_seq.exe <path>/input.txt <path>/output.txt <FIR structure> <coefficient store> <alLow or disalLow symmetry> <number of calculations for MCV| coefficient bit width for others> <number of coefficient sets> <filter rate> <filter factor> <coefficient bit width>

図4‒2. 6 タップのシンメトリカル FIR フィルタ

Data In

Data Out

Z -1

C0

Z -1

C1 C2

Z -1

Z -1

Z -1 Z -1

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 4 章 : 機能の説明 4‒5FIR コンパイラ

1 上に示したように、入力と出力係数のファイル名とディレクトリ・パスを

含める必要があります。

ここで、

■ <FIR structure> は

■ MCV— マルチサイクル(multicycle variable)

■ SER— 完全シリアル

■ MBS— マルチビット・シリアル

■ PAR— 完全パラレル

■ <coefficient store> は

■ LC— ロジック・セル

■ M512—M512 および MLAB ブロック

■ M4K—M4K および M9K ブロック

■ AUTO— 自動のメモリ・ブロック選択

■ <alLow or disalLow symmetry> は

■ MSYM— 対称係数を利用

■ NOSYM— 非対称係数を使用

■ <number of calculations for MCV|coefficient bit width for others> は

■ マルチサイクル・フィルタに対しては、結果の計算に必要なクロック・サイ

クル数

■ すべての他のフィルタに対しては、係数のビット幅を使用

■ <number of coefficient sets> は係数セットのユーザー指定の数である。

■ <filter rate> は、次のいずれか(SGL、INT、DEC)として指定する。

■ SGL— シングル・レート FIR フィルタ

■ INT— 補間 FIR フィルタ

■ DEC— デシメーション FIR フィルタ

■ <filter factor> はレート変更ファクタを表す整数値である。

■ シングル・レート・フィルタの場合、この引数を 1 に設定する必要がありま

す。

■ マルチレート FIR フィルタの場合、この引数は 1 から 16 までの整数値である必

要があります。

■ <coefficient bit width> >は2~32の範囲でユーザー指定の係数ビット幅を表す整数値

です。

例:

coef_seq.exe D:/FIR/coef_log.txt D:/FIR/coef_in.txt MCV M4K MSYM 4 1 SGL 1 8

1 プログラムは自動的に対称性をチェックしますが、禁止する対称性にそれを強制す

ることができます。ユーザーの仕様では、FIR コンパイラのウィザードでの設定と一

致している必要があります。

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

4‒6 第 4 章 : 機能の説明FIR コンパイラ

リロード機能を使用すると、係数値を変更することができます。これらのフィルタ

は、対称的なフィルタの 適化が含まれている場合があります。対称と非対称フィ

ルタの両方を必要とするかもしれないフィルタが必要な場合は、Parameterize FIR Compiler ページの Architecture Specification セクションでの Force Non-Symmetrical Structures をオンにします。

複数セットの係数を選択すると、フィルタは 1 つの係数セットが演算に使用されて

いる間に、別の係数セットを更新することができます。

構造の種類FIR コンパイラのウィザードにより、マルチサイクル、パラレル、シリアル、マルチ

ビット・シリアル、およびマルチ・チャネル構造を選択できます。これらの構造す

べてが係数のリロードをサポートしています。

係数のリオーダについて詳しくは、 4–4 ページの「係数リロードおよびリオーダリン

グ」を参照してください。

マルチサイクル構造マルチサイクル(MCV)フィルタは、高スループットに 適化されます。マルチサ

イクル構造では、フィルタが 1 ~ 1024 クロック・サイクルを使用して結果を計算す

るよう指定します。

Stratix、Stratix II、 Stratix III, または Stratix IV デバイスの場合、Multiplier リスト・ボッ

クスで、DSP Blocks を選択して、マルチサイクル構造を選択すると、FIR コンパイラ

は乗算器にエンベデッド DSP ブロックを使用します。この実装により、小型で高速

なデザインを実現します。

パラレル構造パラレル構造は、フィルタ出力を単一クロック・サイクルで計算します。パラレル・

フィルタは 高の性能を提供しますが、使用するリソースも 大となります。パラ

レル・フィルタをパイプライン化すると、パイプラインのレイテンシ・コストでは

120 ~ 300 MHz の間で実行されるフィルタを生成することができます。

図 4–3 に、パラレル・フィルタのブロック図を示しています。

図4‒3. パラレル・フィルタのブロック図

yout

Array Multiplier Array Multiplier

xin xoutD Q D Q D QD QD QD Q

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 4 章 : 機能の説明 4‒7FIR コンパイラ

シリアル構造シリアル構造は、スループットよりリソースを優先した構造です。このフィルタは、

1 クロック・サイクルごとに 1 ビットの入力データを処理します。したがって、シリ

アル構造は出力を計算するために、クロック・サイクルを N が必要です(N は入力

データの幅です)。Stratix IV、Stratix III、Stratix II、Stratix、Cyclone III、Cyclone II、およ

び Cyclone デバイス・ファミリでは、データ・ストレージ用のメモリ・ブロックを使

用すると、面積の大幅な削減になります。

図 4–4 に、シリアル・フィルタのブロック図を示します。

マルチビット・シリアル構造マルチビット・シリアル構造では、並列にいくつかの小さなシリアル FIR フィルタ

を組み合わせて、FIR の結果を生成します。この構造は、完全に平行な構造よりも少

ない領域を使用しながら、標準シリアル構造よりも高いスループットを提供します。

このより、速度のためにデバイスの領域をトレードオフすることができます。

図4‒4. シリアル・フィルタのブロック図

yout

Bit Array Multiplier Bit Array Multiplier

xin

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

D Q

SerialAccumulator

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

4‒8 第 4 章 : 機能の説明FIR コンパイラ

図 4–5 に、マルチビット・シリアル構造を示します。

図 4–6 に、固定 FIR フィルタの面積 / 速度の「トレードオフ」を示します。

パラレルで動作する 2 つのシリアル・フィルタは、単一のシリアル・フィルタの 2倍の速度での結果を計算します。3 つのシリアル・フィルタは、トリプル速度で動作

して、4 つのシリアル・フィルタは 4 倍の速度で動作します。例えば、16 ビットの

シリアル FIR フィルタは、単一の FIR 計算を完了するためにクロック・サイクルを必

要とします。2 つのシリアル構造を持つマルチビット・シリアル FIR フィルタは、結

果を計算するために、8 クロック・サイクルだけをかかります。4 つのシリアル構造

を使用する場合、計算を実行するために 4 クロック・サイクルだけが必要です。16は 3 で均等に分割されていないため、3 つのシリアル構造は、16 ビットのシリアル

構造に適用できません。

マルチ・チャネル構造DSP システムをデザインするとき、同一の係数を持つ 2 つの FIR フィルタを生成す

る必要が生じることがあります。 高速が必要ない場合は、デザインは 2 個のフィルタ

よりも少ないリソースを使用して、一つのフィルタを共有することができます。例

えば、2 チャネルのパラレル・フィルタは、2 つの出力を計算するために、2 クロッ

ク・サイクルが必要です。結果としてハードウェアは、個々のフィルタの倍データ・

レートで実行する必要があります。

図4‒5. マルチビット・シリアル構造

図4‒6. 固定 FIR フィルタ:面積対スループット

SerialFIR

Filter

SerialFIR

Filter

SerialFIR

Filter

InputData

FilteredData

FIR CompilerCreated Glue

Logic

Multi-BitSerial

Throughput

Area

Serial

Parallel

With ExtendedPipelining

With ExtendedPipelining

With ExtendedPipelining

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 4 章 : 機能の説明 4‒9FIR コンパイラ

1 ロジック・エレメントの数を 小にするには、シリアル演算アーキテクチャ、複数

チャネル、およびデータと係数の保存用のメモリ・ブロックを使用します。

補間およびデシメーション信号を補間するまたはデシメーションするために、FIR コンパイラを使用できます。

補間は、元のサンプル間で余分な点を生成し、デシメーションは、冗長なデータ・

ポイントを削除します。両方の操作は、信号の有効サンプル・レートを変更します。

1 同じ入力データを持っている補間およびデシメーション・フィルタからの出力は異

なる傾向があります。リセット信号と 初の非ゼロ入力データのサンプル間の遅延

を変更すると、入力サンプルは、多相フィルタの異なるパスを行かせることがある

ため、この違いがあります。これにより、入力データは係数の異なるセットを掛け

てフィルタ結果が異なっていることを意味します。

数学的には、信号が補間されるとき、ゼロはデータ・ポイントの間に挿入され、そ

して、データは、オリジナルの信号に存在していないスペクトル成分を取り外すた

めにフィルタにかけられます(図 4–7)。

信号をデシメーションするには、ロー・パス・フィルタは適用されて、ロー・サン

プル・レートに存在していないスペクトル成分を取り外します。フィルタリングし

た後、適切なサンプル値が取られます(図 4–8)。

図4‒7. 信号補間

図4‒8. 信号デシメーション

N

InputData

AfterZeroStuffing

AfterLow-PassFiltering

LPFInput Output

M

InputData

FilteredData

DecimatedData

LPFInput Output

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

4‒10 第 4 章 : 機能の説明FIR コンパイラ

FIR コンパイラは高レベルおよび低レベルの 適化手法を組み合わせて、補間フィル

タとデシメーション・フィルタを生成します。

FIR コンパイラは、演算処理を多相に分解して 適化します。多相分解は 1 つのフィ

ルタを複数の小さなフィルタに分割します。

■ 補間フィルタを使用すると、ゼロ詰めのデータを計算する必要ではないで、リ

ソースを節約する可能性があります ( 4–10 ページの図 4–9)。

■ デシメーション・フィルタを使用すると、ダウン・サンプリングの間に廃棄され

る出力データは計算されなく、リソースを節約する可能性があります( 4–11ページの図 4–10)。

低レベルの 適化手法を使用すると、多相分解フィルタは、複数の係数セットの構

造と適切なラッパーを持つマルチチャネルを使用して実装されます。

FIR コンパイラは、自動デザイン・ツールであるため、マルチ・チャンネル、複数の

係数セットの補間またはデシメーション・フィルタ(さらにマルチ・チャンネル、

複数の係数セットの構造として実装されている)が実装可能です。

これらの 適化手法のネット結果はリソースの一般的な節約です。

補間およびデシメーション構造のための実装の詳細図 4–9 および 4–15 に、補間およびデシメーション・フィルタに多相分解を適用した

場合の結果を示します。

図4‒9. 補間フィルタ構造

P(0)

P(1)

P(2)

P(N-1)

input output

input LPF

output N

input N Channel N Coefficient Set Single Rate FIR Filter

Control Circuitry

output

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 4 章 : 機能の説明 4‒11FIR コンパイラ

図 4–9 に補間フィルタの構造を示します。各多相出力は、一定数のクロック毎に計

算されます。各多相出力と多相ユニット数(補間ファクタ)の乗算に必要なクロッ

ク数だけ、入力データを保持する必要があります。

4–11 ページの図 4–10 に、多相分解によるデシメーション・フィルタを示します。

各多相フィルタは、 終結果を計算する前に計算する必要があります。いくつかの

多相の結果が蓄積される必要があるため、出力はすべての N クロックを更新するこ

とが明らかです。ここで、N =多相フィルタの数 × 各多相の結果を計算するための

クロック数です。

1 多相フィルタの数はデシメーション・ファクタに等しくなります。 入力データは、単

一の多相フィルタを計算するために、かかる時間の間が保持さなければなりません。

補間およびデシメーション・フィルタの可能性下記のアーキテクチャで補間およびディシメーション・フィルタが実現可能:

■ 汎用ロジックを使用したパラレル演算

■ 汎用ロジックを使用したシリアル演算

■ 汎用ロジックを使用したマルチビット・シリアル演算

■ マルチサイクル構造

下記のアーキテクチャで補間およびディシメーション・フィルタが実現可能:

■ データ・ストレージ・タイプのユーザー・コンフィギュレーション(メモリまた

はロジック・セル)

■ 係数の保存タイプのユーザー・コンフィギュレーション(メモリまたはロジッ

ク・セル)

図4‒10. デシメーション・フィルタ構造

P(0)

P(1)

P(2)

P(N-1)

output input

input N Channel N Coefficient Set Single Rate FIR Filter

Control Circuitry

Accumulator

input LPF

output N

output

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

4‒12 第 4 章 : 機能の説明FIR コンパイラ

■ マルチ・チャネル機能

■ 複数の係数セットの機能

ファミリ固有の機能Stratix IV、Stratix III、および Stratix II フィルタは下記のアーキテクチャで三加算器構

造を実装します。

■ 汎用ロジックを使用した完全パラレル演算

■ 汎用ロジックを使用した完全シリアル演算

■ 汎用ロジックを使用したマルチビット・シリアル演算

■ マルチサイクル

すべてのマルチサイクル構造では、Stratix IV、Stratix III、Stratix II、Stratix、Cyclone IIIおよび Cyclone II 構造でハード乗算器を使用できます。また、Stratix IV、Stratix III、Stratix II、および Stratix マルチサイクルの実装では、DSP ブロックのビルトイン加算

器構造を利用しています。

1 Stratix シリーズのデバイスは、データおよび係数の保存に 大限の柔軟性を提供しま

す。Stratix および Stratix II により、ユーザーは(適切な場合)M512、M4K、および

M-RAM の中から選択できます。Stratix III および Stratix IV は MLAB、M9K、および

M144K をサポートしています。

ハーフ・バンドのデシメーション・フィルタデシメーション・ハーフ・バンドに 適化されたアーキテクチャは、マルチサイク

ル変数の構造のために利用可能です。このアーキテクチャでは、ハーフ・バンドの

係数セットが選択されたときに、デシメーション対称のアーキテクチャと比較して

乗算器の数の半分を使用します。ハーフ・バンド係数セットは、対称係数値が奇数

を持っており、他のすべての係数値は 0 です。

現在、唯一の単一の固定係数のセットはこの 適化されたアーキテクチャでサポー

トされています。データ・ストレージおよび係数の保存は Auto または利用可能なブ

ロック・メモリに設定する必要があります。デシメーション・ファクタとチャネル

数の任意の値を選択することができます。計算するためのクロック数が 1 より大き

い必要があります。これらの条件が満たされた場合、FIR コンパイラは、自動的にデ

シメーション・ハーフ・バンドに 適化されたアーキテクチャを選びます。

対称補間のフィルタ新対称補間に 適化されたアーキテクチャは、マルチサイクル構造に利用できます。 このアーキテクチャは、対称係数のセットが選択されている場合、標準の補間フィ

ルタに比べて乗算器の数を半分にする必要があります。

フィルタ・タップ数が奇数でなければなりません。現在、唯一の単一の固定係数の

セットはこの 適化されたアーキテクチャでサポートされています。 データ・スト

レージおよび係数の保存は Auto または利用可能なブロック・メモリに設定する必要

があります。補間ファクタとチャネル数の任意の値を選択することができます。計

算するためのクロック数は、1 以上にする必要があります。これらの条件が満たされ

た場合、FIR コンパイラは、自動的にデシメーション・ハーフ・バンドに 適化され

たアーキテクチャを選びます。

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 4 章 : 機能の説明 4‒13シミュレーション出力

Pipeliningパイプライン化は、遅延の増大のコストで高性能なフィルタを製造するための も

効果的であり、より多くのパイプライン・ステージを追加すると、フィルタは速く

なります。

1 パイプライン化は、長いキャリー・チェインは短い長さに分解します。 したがって、

デザイン内のキャリー・チェーンがすでに短い場合、パイプラインを追加すると、

設計時間を短縮することはできません。

FIR コンパイラでは、1 つ、2 つ、または 3 つのパイプライン・レベルを追加するか

どうかを選択できます。

シミュレーション出力FIR コンパイラはデザイン・シミュレーションのために、出力ファイルの数を生成し

ます。カスタム FIR フィルタを作成した後、出力ファイルは MATLAB とまたは VHDLシミュレーション・ツールと使用できます。テスト・ベクタと MATLAB ソフトウェ

アを使用して、デザインをシミュレートできます。

1 データ・ストレージがクリアされている場合、IP 機能シミュレーション・モデルは

適切なデータを出力します。データ・ストレージがクリアされていない場合、機能

シミュレーション・モデルは不定なデータを出力します。 関連するサンプルが利用可

能になる前に必要なクロック・サイクル数は、N です。ただし、N = (チャネル数)

x (係数の数)x (出力計算に必要なクロック・サイクル数)。

FIR コンパイラで生成されたファイル・リストは 2–7 ページの表 2–1 を参照してくだ

さい。

Avalon Streaming インタフェースAvalon® Streaming (Avalon-ST) インタフェースは、ソース・インタフェースからシン

ク・インタフェースへのデータ転送に対して標準的な柔軟性の高いモジュラ式プロ

トコルを定義しており、データパスにおけるデータ・フローのコントロール・プロ

セスを簡略化します。

Avalon-ST インタフェース信号は、チャネルやパケット境界の概念のない従来の単一

データ・ストリームをサポートします。このようなインタフェースは通常、data、ready、および valid 信号から構成されます。

Avalon-ST インタフェースは、複数のチャネルに渡ってインタリーブされたパケット

でバーストとパケット転送のために、より複雑なプロトコルをサポートすることが

できます。

Avalon-ST インタフェースは、本質的に複雑な制御ロジックを実装せずに効率的な達

成を可能にするマルチ・チャンネル・デザイン時間多重実装を同期させます。

Avalon-ST インタフェースでは、シンクがデータの送信を停止するようにソースに通

知できるフロー制御メカニズムであるバックプレッシャをサポートしています。FIFOバッファがいっぱいである場合、または、その出力で輻輳が発生している場合、シ

ンクは常にデータの流れを止めるためにバックプレッシャを使用しています。

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

4‒14 第 4 章 : 機能の説明Avalon Streaming インタフェース

FIR コンパイラ MegaCore ファンクションを含むデータパスを設計するときに、ダウ

ンストリーム・コンポーネントが常にデータを受け取ることができることを知って

いれば、バックプレッシャを必要としないことがあります。FIR コンパイラが高い ast_source_ready 信号を駆動すると、および ast_sink_ready 信号を接続しないこ

とにより、より高いクロック・レートを達成するかもしれません。

1 マルチセット・フィルタの係数のリロードに関連するポートおよび係数セットの選

択ポートは Avalon ストリーミング準拠ではないです。

Avalon Interface Specifications は、Avalon-ST インタフェースのいずれかのタイプを指定

するために使用できるパラメータを定義します。 4–14 ページの表 4–1 に、FIR コン

パイラで使用される Avalon-ST インタフェースを定義されるパラメータ値を示します

表に、明示的に表示されないすべてのパラメータは未定義値を持っています。

Avalon Interface Specifications はオプションで、多くの信号の種類を定義します。 表 4–2 に、FIR コンパイラ MegaCore ファンクションの Avalon-ST インタフェースで使用され

る信号タイプを示します。表に明示的に記載されていない信号タイプが含まれてい

ません。

f Avalon-ST インタフェース・プロトコルの詳細について、 「Avalon Interface Specifications」を参照してください。

表4‒1. Avalon-ST インタフェースのパラメータ

パラメータ名 値READY_LATENCY 0

BITS_PER_SYMBOL データ幅

SYMBOLS_PER_BEAT 1

SYMBOL_TYPE 符号ありまたは符号なし

ERROR_DESCRIPTION 00: エラーなし

01: 不在 startofpacket (SOP)

10: 不在 endofpacket (EOP)

11: 予想外の EOP またはその他のエラー

表4‒2. Avalon-ST インタフェースの信号タイプ

信号タイプ 幅 入力 / 出力ready 1 シンク - ソース

valid 1 ソース - シンク

data データ幅 ソース - シンク

channel log2(チャネル数) ソース - シンク

error 2 ソース - シンク

startofpacket 1 ソース - シンク

endofpacket 1 ソース - シンク

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 4 章 : 機能の説明 4‒15Avalon Streaming インタフェース

Avalon-ST データ転送のタイミング 図 4–11 に、Avalon-ST インタフェース信号を示します。

シンクは、単一のクロック・サイクルの ready 信号をアサートすることによって、ア

クティブなサイクルのための準備ができているソースに示します。シンクがデータ

の準備ができている中のサイクルは、ready cycles と呼ばれます。 準備サイクル中に、

ソースが validをアサートして、シンクにデータを提供しています。送信するデー

タが存在しない場合、それは validをデアサートし、任意の値にデータを駆動する

ことができます。

READY_LATENCY=0 のとき、データは、同じサイクルでアサートされた ready および

valid のみで転送されます。この操作モードでは、ソース・データは有効なデータ送

信を開始する前にシンクの ready 信号を受信する必要はありません。ソースは、い

つでもデータを提供して、 valid をアサートします。また、データをキャプチャする

シンクおよび readyをアサートするシンクを待ちます。ソースは、ready および

validを両方アサートするとき、ソースからの入力データを取り込みます。

図 4–12 に、データ転送のタイミングを示しています。

ソースは、シンクの準備ができていないにもかかわらず、データを提供し、1 サイク

ルで valid をアサートします。 ソースは、シンクが次のデータ・サイクルに移る前

に、 readyがアサートされるときにサイクル 2 まで待機します。 サイクル 3 では、

ソースは同じサイクルでデータを駆動し、シンクはそれを受信する準備ができたの

で転送はすぐに発生します。サイクル 4 では、シンクは readyがアサートが、ソー

スが有効なデータを駆動しません。

図4‒11. Avalon-ST インタフェース

Data Source Data Sink

valid

data

error

ready

channel

startofpacket

endofpacket

図4‒12. READY_LATENCY=0 の Avalon-ST インタフェースのタイミング

Do D1 D2

0 1 2 3 5 6 7 84

clk

ready

valid

error

data

00 00 00 00

D2

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

4‒16 第 4 章 : 機能の説明信号

パケット・データ転送ビートは、ソースとシンクのインタフェース間のデータの 1 単位の移転として定義

されています。データ・ユニットは、1 つまたは複数の記号で構成され、各有効なサ

イクルに関する複数の情報を伝えるモジュールをサポートすることが可能です。 パケット・データ転送は、マルチ・チャネル転送に使用されます。 2 つの追加信号

(startofpacket および endofpacket)は、パケット転送のために実装されます。

図 4–13 に、データ・サンプルが属するチャネルを示すチャネル信号の例を示しま

す。

1 channel 入力信号は、FIR コンパイラ・インタフェースに使用されません。

図 4–13 のデータ転送には , readyおよび valid がアサートされているとき、サイク

ル 1、2、4、および 5 で発生します。サイクル 1 の間に、 startofpacket がアサート

されて、 初のデータが転送されます。サイクル 5 の間に、 endofpacket がアサート

されて、これはパケットの終わりであることを示しています。

channel 信号は、データに関連付けられたチャネルのインデックスを示します。例え

ば、サイクル 1 で、チャネル 0 に関連付けられている D0 のデータが入手可能です。

error 信号は、通常の動作中に値 00 に保存します。 00 以外の値がデータ・ソース( 図 4–11 のように)を受信されたとき、またはパケット・エラーが FIR フィルタの

Avalon-ST インタコントローラによって検出されたときに、コントローラがリセット

されて、次の有効な startofpacket 信号を待ちます。 また、コントローラは、その

データ・ソース・モジュールのエラー出力から受信されたエラー信号を送信します。

1 error 信号は、デザインではなく、Avalon-ST コントローラをリセットするだけです。 そのため、出力データは、エラー状態が数サイクルの無効なデータが含まれている

可能性がある後に生成されます。エラー・メッセージはシステム中に存在する場合、

常にそれはグローバル・リセットが適用されることを推奨します。

信号表 4–3 に、FIR コンパイラ MegaCore ファンクションの入力および出力信号を示しま

す。

図4‒13. Packet Data 転送

0 1 2 3

00 00 00 00

D0 D1 D2 D3

1 2 3 4 5 6 7

clkreadyvalid

startofpacketendofpacketchannel[1:0]

dataerror[1:0]

表4‒3. FIR コンパイラの信号 ( その1 )

信号入力 /出力 説明

clk 入力 クロック信号はすべての内部 FIR フィルタ・レジスタをクロックするために使用されます。

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 4 章 : 機能の説明 4‒17信号

enable 入力 アクティブ High クロック・イネーブル信号。Parameterize FIR Compilerページで Add global clock enable pin オプションを選択した場合、このピンを表示されます。(Avalon-ST レジスタはクロック・イネーブルに接続されません。)

reset_n 入力 同期のアクティブ Low リセット信号です。clk. の立ち上がりエッジでFIR フィルタの制御回路をリセットします。 この信号は 1 クロック・サイクルよりも長く持続します。

ast_sink_ready 出力 t 現在のクロック・サイクルでデータを受け入れることができる FIR フィルタによってアサートされます。

ast_sink_valid 入力 データが有効であるとこの信号がアサートされます。 ast_sink_valid がアサートされていない場合、新しいデータが要求されるとき、およびデータは Avalon-ST 入力 FIFO に残されていないときに、FIR 処理は停止します。それ以外の場合は、FIR 処理が続行されます。

ast_sink_data 入力 サンプル入力データです。

ast_sink_sop 入力 受信サンプル・グループの開始をマークします。パケット開始(SOP)はチャネル 0 からのサンプルとして解釈されます。

ast_sink_eop 入力 受信サンプル・グループの終了をマークします。N チャネルに関連付けられているデータがある場合、サンプルが 後のチャネル(つまり、チャネル N - 1)に属するとき、パケット終了 EOP(End of Packet)は高ければ、データ入力で表示されます。

ast_sink_error 入力 シンク側の Avalon-ST プロトコル違反を示すエラー信号:

■ 00: エラーなし

■ 01:SOP の欠落

■ 10:EOP の欠落

■ 11:予期しない EOP

他のエラーは 11 にマークします。

ast_source_ready 入力 データを受け入れることができる場合、ダウンストリーム・モジュールによってアサートされます。

ast_source_valid 出力 出力への有効データが存在するときに FIR フィルタによりアサートされます。

ast_source_channel 出力 その結果データの出力で表示されているチャネル・インデックスを示します。 信号幅= log2(チャネル数)。

ast_source_data 出力 フィルタ出力。データ幅はパラメータ設定に依存します。

ast_source_sop 出力 発信 FIR フィルタ結果グループの開始をマークします。「1」の場合、チャネル 0 に対応する結果は出力です。

ast_source_eop 出力 発信 FIR フィルタ結果グループの終了をマークします。「1」の場合、チャネル N-1 に対応する結果は出力です。ここで、N はチャネル数です。

ast_source_error 出力 ソース側の Avalon-ST プロトコル違反を示すエラー信号:

■ 00:エラーなし

■ 01: SOP の欠落

■ 10: EOP の欠落

■ 11:予期しない EOP

他のエラーは 11 にマークします。

表4‒3. FIR コンパイラの信号 ( その2 )

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

4‒18 第 4 章 : 機能の説明タイミング図

タイミング図reset_n 信号は、FIR コンパイラを制御するコントロール・ロジックおよびステー

ト・マシン(以前の入力を保持するデータ保存エレメントは含まれません)をリ

セットします。

reset_n 信号が印加されても、以前のデータはクリアされません。データをクリアす

るには、n クロック・サイクルのために ast_sink_data ポートを 0 に設定します。

ここで、 n = (係数の数) × (入力チャネル数)× (FIR 結果を計算するために必要なクロック・サイクル数)。

FIR 出力値はデザインでの係数値によって決定される値です。したがって、ユーザー

のデザインのタイミング図は次の図に示すものと異なる場合があります。しかし、

特定のパラメータ化された場合の信号の間の正しいタイミングの関係を得るために、

FIR コンパイラによって生成されたテストベンチを使用することができます。

すべてのタイミング図は、 ast_source_ready および ast_sink_ready が常に 1(別に

注記がない限り)のときに完全なストリーミングの動作を前提とします。

coef_set 入力 計算のための FIR フィルタの使用を設定した係数を選択します。 (複数の係数セットを使用されているときに表示されます。)信号幅= log2

(係数セットの数)。

coef_in_clk 入力 係数がメモリに保存されているときに係数リロードのためのクロックです。(Coefficient Reload オプションを選択されている場合および Use Single Clock オプションを選択されていない場合で表示されます。)このクロックは clk とは異なります。

coef_set_in 入力 リロードされる係数セットを選択します。(複数の係数セットを使用されているおよび Coefficient Reload オプションを選択されている場合で表示されます。)信号幅= log2(係数セットの数)。

coef_in 入力 係数をリロードするときの入力係数値。 (Coefficient Reload オプションを選択されている場合で表示されます。)

coef_we 入力 アクティブ High ライト・イネーブル信号。係数はリロード可能な場合、上書き係数を有効にします。

coef_ld 出力 係数リロードのコントロール・ポート。このポートは、マルチサイクル・フィルタが選択されている場合および係数ストレージはロジック・セルであることのみで作成されます。

表4‒3. FIR コンパイラの信号 ( その3 )

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 4 章 : 機能の説明 4‒19タイミング図

リセットおよびグローバル・ クロック・イネーブル動作図 4–14 に、リセットおよびグローバル・ クロック・イネーブル動作を示します。

フィルタにリセット(reset_n)が供給されると、 ast_sink_ready 信号および

ast_source_valid 信号は Low になります。リセットが解放された後のクロックの次

の立ち上がりエッジで、ast_sink_readyは High になり、設計が新しいデータを受け

入れる準備ができていることを示します。Avalon-ST コントローラの小さな FIFO があ

るので、この動作は、フィルタ・タイプとアーキテクチャとは無関係です。

FIR MegaCore ファンクションが停止されたときに、グローバル・クロック(それが

存在する場所)信号を制御することもできます。Avalon-ST コントローラがグローバ

ル・クロック・イネーブルとは独立に動作します。グローバル・クロック・イネー

ブルが Low レベルになると、FIR はすぐに停止されます。 しかし、Avalon-ST コント

ローラにおける内部のバッファリングのため、 ast_sink_ready 信号は次のサイクル

で Low にできます。同じ理由で、グローバル・イネーブルが High のとき、 ast_sink_ready は次のサイクルで High になることがあります。

ast_source_valid 信号は、Avalon-ST コントローラによって生成され、グローバル・

クロック・イネーブルとは無関係です。利用可能な有効なデータが転送され、これ

以上の出力データが使用可能の場合、転送する有効なデータがあるまでに、この信

号が Low になります。

シングル・レート・ フィルタのタイミング図図 4–15 に、 MCV アーキテクチャと 1 の値を計算するためのクロックまたはパラレ

ル・アーキテクチャで実装されたシングル・レート・ フィルタのタイミング図を示

します。

図4‒14. リセットおよびクロック・イネーブル・プロトコル

図4‒15. シングル・チャネル、シングル・レート(パラレルまたは MCV シングル・サイクル)

© 2011 年 5月 Altera Corporation FIR コンパイラ ユーザーガイド

4‒20 第 4 章 : 機能の説明タイミング図

このフィルタは各クロック・サイクルの入力を受け入れて、出力を生成します。 ast_source_ready および ast_sink_valid が High に保たれるため、フィルタは内部的

に完全なストリーミングを実行することができます。 ast_sink_ready および

ast_sink_valid はクロックの立ち上がりエッジの間に両方とも High の場合、入力が

転送されます。

図 4–16 は図 4–15 に、単一チャネル・フィルタと同じ仕様を持つ 3 つのチャネル・

フィルタを示しています。

FIR フィルタはシンク(入力)とソース(出力)モジュールの両方のために、パケッ

ト開始(sop)およびパケット終了 (eop) 信号を持っています。 FIR フィルタの 初

の入力データは、 ast_sink_sop ポートの High 値を伴っていて、 初のチャネルに属

しています。

3 番目の入力データは、ast_sink_eop ポートの High 値でパケットの終わりとして

マークされています。このシーケンスは、各サイクルで継続的に繰り返します。

フィルタ出力の準備が整うと、 ast_source_valid は High になり、 初のデータ出力 ast_source_sop は High になってパケット開始をマークします。 ast_source_channel 出力は、どの特定の出力が属しているチャネルを示しています。 後のチャネルの

データは、ast_source_eop ポートの High 値でマークされています。

図 4–17 および 4–21 ページの図 4–18 に、別のシングル・チャネル、シングル・レー

ト・フィルタのタイミング図を示しています。これらの図は、各 3 のクロック・サ

イクルで、FIR フィルタは入力データが必要であり、1 つの出力データを生成しま

す。 一般的に、MCV のマルチサイクル・フィルタ(値を計算するためのクロックが 1より大きい場合)は、シリアル・フィルタ、マルチビット、およびシリアル・フィ

ルタは、N は以下を表すすべての N クロック・サイクルの新入力データを必要とし

ます。

■ MCV マルチサイクル・フィルタのために、N は、値を計算するためのクロック

■ マルチビット・シリアル・フィルタのために、 N =(入力データのビット幅)/(シリアル・ユニット数)

図4‒16. 3 チャネル、シングル・レート(パラレルまたはMCV シングル・サイクル)

FIR コンパイラ ユーザーガイド © 2011 年 5月 Altera Corporation

第 4 章 : 機能の説明 4‒21タイミング図

■ シリアル・フィルタのために、 N =(入力データのビット幅 +1)

図 4–17 に、3 クロック・サイクルごとに、フローは ast_sink_valid をアサートす

るデータ・プロバイダによって制御されます。

図 4–18 に、各クロック・サイクルで、 ast_sink_valid は常に High に保たれ、デー

タ・プロバイダは、新しいデータをフィードすることができます。しかし、フィル