Bölüm 7 Ardışıl Lojik Devreler - Fırat...

Transcript of Bölüm 7 Ardışıl Lojik Devreler - Fırat...

7-1

Bölüm 7 Ardışıl Lojik Devreler

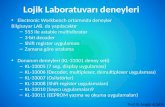

DENEY 7-1 Flip-Floplar

DENEYİN AMACI

1. Kombinasyonel ve ardışıl lojik devreler arasındaki farkları ve çeşitli bellek birimi

uygulamalarını anlamak.

2. Çeşitli flip-flop türlerinin çalışma prensiplerini ve uygulamalarını incelemek.

GENEL BİLGİLER

Şekil 7-1-1’de, iki DEĞİL (NOT) yada TÜMLEME kapısı gösterilmiştir. IC2’nin çıkışı

IC1’in girişine bağlanmıştır. IC1’in çıkışı ”1” ise, IC2’nin çıkışı “0” olur. IC2’nin çıkışı

IC1’in girişine bağlı olduğu için, IC1’in girişi tekrar “1”e çevrilmiş olur. Eğer IC1’in

girişine harici bir darbe uygulanırsa IC1’in çıkışı “0”, IC2’nin çıkışı “1” olur (IC1’in

çıkışı tekrar “0”a döner).

Şekil 7-1-1 İki NOT kapısı ile oluşturulan RS mandal (latch)

Harici darbe A, IC2’nin çıkışı B olarak ifade edilirse, A ya da B “1” olduğu zaman,

IC1’in çıkışı “0” olur.

Şekil 7-1-1’deki NOT kapıları, iki adet NOR kapısıyla değiştirilirse ve iki giriş R ve S

olarak ifade edilirse, Şekil 7-1-2’deki R-S flip-flop elde edilmiş olur.

R = Reset (sıfırlama) girişi, Q çıkışını “0” yapar.

S = Set (birleme) girişi, Q çıkışını “1” yapar.

7-2

Şekil 7-1-2 İki NOR kapısı ile oluşturulan RS flip-flop

IC1’in çıkışı Q (normal çıkış) olarak adlandırılırken, IC2’nin çıkışı ise Q (tümleyen çıkış) olarak adlandırılır. Flip-flop, uygun bir lojik giriş uygulandığında durum değiştirir,

güç sağlandığı sürece yada girişi değişene kadar kararlı durumda kalır.

Çoğu durumda, flip-floplar NOR yada NAND kapılarıyla gerçekleştirilir. Şekil 7-1-3,

NOR kapılarıyla gerçekleştirilmiş bir pozitif lojik R-S flip-flopu, Şekil 7-1-4 ise, NAND

kapılarıyla gerçekleştirilmiş bir negatif lojik R-S flip-flopu göstermektedir.

R-S flip-flop, en basit flip-flop olup diğer flip-flopları gerçekleştirmek için kullanılabilir.

Bu yüzden RS flip-flop, “temel-flip-flop” olarak da adlandırılır. Tablo 7-1-1’de, R-S flip-

flopun doğruluk tablosu gösterilmiştir. Qn şimdiki çıkış durumunu ifade ederken,

Qn+1 ise bir sonraki çıkış durumunu ifade eder.

Şekil 7-1-3 NOR RS flip-flop Şekil 7-1-4 NAND RS flip-flop

Tablo 7-1-1 RS flip-flop doğruluk tablosu

7-3

R-S flip-flopun doğruluk tablosundan aşağıdaki sonuçlar çıkarılabilir:

(1) R=0 ve S=0 iken Qn+1=Qn’dir, yani Qn+1 bir önceki Qn durumuna (“0” yada “1”

olabilir) eşittir.

(2) R=0 ve S=1 iken, flip-flop birlenir (Qn+1=”1”).

(3) R=1 ve S=0 iken, flip-flop sıfırlanır (Qn+1=”0”).

(4) R=1 ve S=1 iken, Qn+1 aynı anda hem “0” hem “1” olmaya çalışır. Çıkış aynı anda

iki duruma sahip olamayacağı için, R=S=1 durumunda Qn+1 “tanımsız” yada

“belirsiz”dir.

Şekil 7-1-5’te, R-S flip-flopun tam sembolü gösterilmiştir. CK saat sinyalidir ve flip-flop,

saat sinyali mevcut ise, durum değiştirecektir.

PR = Preset ; Saat sinyaline bakmaksızın, Q çıkışını “1” yapar.

CL = Clear (Sil) ; Saat sinyaline bakmaksızın, Q çıkışını “0” yapar.

Şekil 7-1-5 R-S flip-flop

Bir R-S flip-flop kullanılarak, D flip-flop gerçekleştirilebilir. D flip-flopun sembolü ve R-

S flip-flop ile gerçekleştirilme şeması sırasıyla Şekil 7-1-6(a) ve (b)’de gösterilmiştir.

(a) Sembol (b) RS flip-flop ile gerçekleştirilmesi

Şekil 7-1-6 D flip-flop

7-4

D flip-flop, genellikle veri iletimi için kullanılır. Doğruluk tablosu Tablo 7-1-2’de

gösterilmiştir.

Tablo 7-1-2 D flip-flop doğruluk tablosu

Bir D flip-flop kullanılarak, T flip-flopu gerçekleştirilebilir. T flip-flopun sembolü ve D

flip-flop ile gerçekleştirilme şeması sırasıyla Şekil 7-1-7(a) ve (b)’de gösterilmiştir. T

flip-flopun doğruluk tablosu Tablo 7-1-3’te gösterilmiştir.

(a) Sembol (b) D flip-flop ile gerçekleştirilmesi

Şekil 7-1-7 T flip-flop

Tablo 7-1-3

Tablo 7-1-3’ten görüldüğü gibi, T flip-flopun çıkış durumu sadece T=1 ve CK=1 iken

değişir. Başlangıçta Qn=”0” kabul edilirse, T=1 ve CK=1 olduğunda, T flip-flopun

çıkışı “1” olur. T flip-flopun çıkışı, tekrar T=1 ve CK=1 oluncaya kadar, “1” durumunda

kalır ve koşul sağlanınca tekrar “0” durumuna döner.

7-5

T flip-flopun çıkışı, T=1, CK=1 olduğu zaman, “0” ve “1” arasında durum değiştirir. T

flip-flopun bu benzersiz karakteristiğinden yararlanılarak, “2’ye bölme” devreleri

gerçekleştirilebilir. Şekil 7-1-8’e bakılacak olursa, iki giriş dalga şekline karşılık,

sadece bir çıkış dalga şekli vardır. T flip-floplar genellikle sayıcıların gecikme

devrelerinde kullanılır.

Şekil 7-1-8 T flip-flopun giriş ve çıkışı

J-K flip-flop, R-S flip-flopun “belirsiz” durumunu ortadan kaldırabilir. J-K flip-flopun

sembolü, Şekil 7-1-9’da gösterilmiştir.

Şekil 7-1-9 JK flip-flop Şekil 7-1-10 RS flip-flop ile gerçekleştirilmesi

Şekil 7-1-10’da, R-S flip-flopla gerçekleştirilmiş bir J-K flip-flop eşdeğeri gösterilmiştir.

Tablo 7-1-4’teki doğruluk tablosuna bakılacak olursa, J-K flip-flopun, J=1, K=1 ve

CK=1 durumu dışında, S-R flip-flopuyla aynı olduğu,bu durumda da T flip-flopa

benzediği görülür.

7-6

Tablo 7-1-4 J-K flip-flop doğruluk tablosu

J-K flip-flop, belirsiz duruma sahip olmadığı ve hemen hemen tüm flip-flopları

gerçekleştirmek için kullanılabildiği için, “genel flip-flop” olarak da adlandırılır.

Şekil 7-1-11’de, bir Master/Slave J-K flip-flop devresi gösterilmiştir.

Şekil 7-1-11 Master/Slave J-K flip-flop

CK=0 iken, master flip-flop yeni giriş kabul etmez ve Q’ ve 'Q çıkışları aynı kalır, Q’

ve 'Q , uydu flip-flopun Q ve 'Q çıkışlarına iletilir.

CK=1 iken master flip-flop yeni giriş kabul edebilir, ancak slave flip-flopun Q ve Q çıkışları değişmez.

Şekil 7-1-12’de, master/slave flip-flopun zamanlama diyagramı verilmiştir. CK=1 iken,

CK’nın düşen kenarıyla son giriş değeri tutuluncaya kadar, giriş sürekli olarak değişir.

CK=0 iken, slave flip-flop CK’nın düşen kenarıyla tetiklendiği için, master flip-flopun

çıkışı, slave flip flopa gönderilir.

7-7

Şekil 7-1-12 Master/slave flip-flopun zamanlama diyagramı

KULLANILACAK ELEMANLAR

1. KL-22001 Temel Elektrik Devreleri Deney Düzeneği

2. KL-26006 Ardışıl Lojik Devre Deney Modülü (1)

DENEYİN YAPILIŞI

A. Lojik Kapılar ile RS Flip-Flop Gerçekleştirmek

1. Şekil 7-1-13 yardımıyla gereken bağlantıları yapın. +5VDC ve

+12VDC sabit güç kaynaklarını, KL-26006 modülüne bağlayın.

2. A3,A4 girişlerini sırasıyla SW1,SW2 veri anahtarlarına ve F6,F7 çıkışlarını

L1,L2 Lojik Göstergelerine bağlayın. F6 ve F7’nin durumları nedir? Gücü

kapatın ve birkaç saniye sonra yeniden açın. Şu anda F6 ve F7’nin durumları

nedir?

7-8

Şekil 7-1-13 Bağlantı diyagramı (KL-26006 blok c)

Şekil 7-1-14 NAND RS flip-flop

3. Tablo 7-1-5’teki giriş dizilerini takip edin. F6,F7’yi gözleyin ve kaydedin.

STATE A4 A3 F6 F7 0 1 2 3

0 0 1 1

0 1 0 1

Tablo 7-1-5

4. Tablo 7-1-5’teki sonuçlardan, Q ve Q çıkışları ile R ve S girişlerini belirleyin.

R=________ , S=________ , Q=________ , Q =________

5. Şekil 7-1-15’teki bağlantı diyagramı ve Şekil 7-1-16’daki devre yardımıyla

gerekli bağlantıları yapın. CK2’yi +5V’a bağlayın.

6. A1 ve A5 girişlerini sırasıyla SW1 ve SW2 girişlerine bağlayın.

7-9

Şekil 7-1-15 Bağlantı diyagramı (KL-26006 blok c)

Şekil 7-1-16 RS flip-flop

7. Tablo 7-1-6’daki giriş dizilerini takip edin. F6,F7’yi gözleyin ve kaydedin.

STATE A5 A1 F6 F7 0 1 2 3

0 0 1 1

0 1 0 1

Tablo 7-1-6

B. RS Flip-Flop Kullanarak D Flip-Flop Gerçekleştirmek

1. Şekil 7-1-17’deki bağlantı diyagramı ve Şekil 7-1-18’deki D flip-flop devresi

yardımıyla gerekli bağlantıları yapın.

7-10

Şekil 7-1-17 Bağlantı diyagramı (KL-26006 blok c)

Şekil 7-1-18 D flip-flop

2. A1’i SW1’e, CK2’yi SWA Darbe Anahtarının A çıkışına ve F6’yı L1 Lojik

Göstergesine bağlayın.

3. Tablo 7-1-7’deki giriş dizilerini takip edin. Çıkış durumlarını gözleyin ve

kaydedin.

Tablo 7-1-7

7-11

C. RS Flip-Flop Kullanarak D Flip-Flop Gerçekleştirmek

1. Şekil 7-1-19’daki bağlantı diyagramı ve Şekil 7-1-20’deki JK flip-flop devresi

yardımıyla gerekli bağlantıları yapın.

Şekil 7-1-19 Bağlantı diyagramı (KL-26006 blok c)

Şekil 7-1-20 JK flip-flop

2. CK2’yi SWA Darbe Anahtarının A çıkışına, A1’i SW1 veri anahtarına ve F6’yı

L1 Lojik Göstergesine bağlayın.

3. Tablo 7-1-8’deki giriş dizilerini takip edin. Çıkış durumlarını gözleyin ve

kaydedin.

7-12

Tablo 7-1-8

D. RS Flip-Flop Kullanarak Master/Slave JK Flip-Flop Gerçekleştirmek

1. Şekil 7-1-21’deki bağlantı diyagramı ve Şekil 7-1-22’deki master/slave JK flip-

flop devresi yardımıyla gerekli bağlantıları yapın.

Şekil 7-1-21 Bağlantı diyagramı (KL-26006 blok c)

Şekil 7-1-22 Master/Slave JK flip-flop

7-13

2. CK1’i SWA Darbe Anahtarının A çıkışına; J ve K’yı, SW0 ve SW1 veri

anahtarlarına bağlayın. F1,F2,F6,F7’yi sırasıyla L0,L1,L2,L3 Lojik

Göstergelerine bağlayın.

3. Tablo 7-1-9’daki giriş dizilerini takip edin. Çıkış durumlarını gözleyin ve

kaydedin.

CK1 K J F1 F2 F6 F7 -> F1 F2 F6 F7 0 0 1 1 1

0 1 0 1 1

-> -> -> -> ->

Tablo 7-1-9

E. D Flip-Floplar ile Kaydırmalı Kaydedici Gerçekleştirmek

1. Şekil 7-1-23 yardımıyla gereken bağlantıları yapın. +5VDC ve

+12VDC sabit güç kaynaklarını, KL-26006 modülüne bağlayın.

Şekil 7-1-23 Bağlantı diyagramı (KL-26006 blok a)

7-14

2. B(clear)’yi SW0’a; A(I/P)’yı SW1’e; CK’yı SWA’nın A çıkışına; F1,F2,F3,F4’ü

sırasıyla L1,L2,L3,L4’e bağlayın.

3. D flip-flopları silmek için, SW0’ı “0” konumuna getirip daha sonra tekrar “1”

konumuna getirin. SW1 anahtarını “1” konumuna getirin. SWA Darbe

Anahtarını kullanarak, CK’ya dört saat darbesi uygulayın. Her saat darbesi

sonunda çıkış göstergelerini gözleyin ve kaydedin.

F1-F4=___________________________________________________

4. D flip-flopları silmek için, SW0’ı “0” konumuna getirip daha sonra tekrar “1”

konumuna getirin. SW1 anahtarını “1” konumuna getirin ve bir saat darbesi

sonunda tekrar “0” konumuna getirin. Daha sonra SWA Darbe Anahtarını

kullanarak, CK’ya üç saat darbesi uygulayın. Her saat darbesi sonunda çıkış

göstergelerini gözleyin ve kaydedin.

F1-F4=___________________________________________________

F. İki Yönlü Kaydırmalı Kaydedici Gerçekleştirmek

1. Şekil 7-1-24 yardımıyla gereken bağlantıları yapın. +5VDC ve

+12VDC sabit güç kaynaklarını, KL-26006 modülüne bağlayın.

Şekil 7-1-24 Bağlantı diyagramı (KL-26006 blok b, U7=7495)

2. Aşağıda belirtilen bağlantıları tamamlayın:

A,B,C,D girişleri, SW0,SW1,SW2,SW3 veri anahtarlarına

F1,F2,F3,F4 çıkışları, L4,L3,L2,L1 lojik göstergelerine

D1 (LOAD), SWA Darbe Anahtarının A çıkışına

C1 (CK), SWB Darbe Anahtarının B çıkışına

7-15

B1 (Seri Giriş), SW7 veri anahtarına

A1 (MODE), SW6 veri anahtarına

Tablo 7-1-10 7495’in fonksiyon tablosu

3. A1 ve B1 için, Tablo 7-1-11’deki giriş dizilerini takip edin. Çıkışları gözleyin ve

kaydedin.

GİRİŞLER ÇIKIŞLAR C1 B1 A1 F1 F2 F3 F4

1 1 1 1 1 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 Tablo 7-1-11

4. A1 ve B1 girişlerini “1” yapın. D,C,B,A için, Tablo 7-1-12’deki giriş dizilerini

takip edin. Çıkışları gözleyin ve kaydedin.

GİRİŞLER ÇIKIŞLAR D1 D C B A F1 F2 F3 F4

0 1 1 0 0

0 0 1 1 1

1 1 1 1 1

0 0 0 1 0

Tablo 7-1-12

7-16

G. RS Flip-Floplar ile Gürütü Giderme Devresi Gerçekleştirmek

1. Şekil 7-1-25 yardımıyla gereken bağlantıları yapın. Gürültü giderme devresini

gerçekleştirmek için, Şekil 7-1-25 ve 7-1-26’daki RS flip-flop devresi

kullanılacaktır.

Şekil 7-1-25 Bağlantı diyagramı (KL-26006 blok c)

Şekil 7-1-26 RS flip-flop

2. A4 girişini SW0 veri anahtarına ve A3’ü Saat Üretecinin çıkışına bağlayın. Bu

durumda, Saat Üreteci, RS flip-flop için gürültü kaynağı gibi davranır.

3. A4=”1” yapın. F6’yı ölçün. F6=_________

4. A3 girişini SW0 veri anahtarına ve A4’ü Saat Üretecinin çıkışına bağlayın

5. A3=”1” yapın. F6’yı ölçün. F6=_________

7-17

DENEY 7-2 Sayıcılar

DENEYİN AMACI

1. Sayıcıların çalışma prensiplerini ve JK flip-floplarla nasıl gerçekleştirileceğini

anlamak.

2. Asenkron ve senkron sayıcıları incelemek.

GENEL BİLGİLER

Sayıcılar, flip-floplar ve temel lojik kapılar kullanılarak gerçekleştirilirler. Önceki

deneyde, T flip-flop çıkışının, T=1 ve CK=1 durumunda, “0” ile “1” durumları arasında

değiştiği ifade edilmişti.

Şekil 7-2-1 Üç adet T flip-flopla gerçekleştirilen 3-bitlik sayıcı

Şekil 7-2-1’de seri olarak bağlanmış üç adet T flip-flop görülmektedir. Önde bulunan

flip-flopların Q çıkışları, bir sonraki flip-floplar için saat girişi (CK) olarak kullanılmıştır.

Ardarda seri olarak bağlanan flip-flop sayısının “n” olduğu ve “N” adet giriş bulunduğu

kabul edilirse, en son flip-flopun çıkışı N/2n olur. Çıkış dalga şekilleri, Şekil 7-2-2’de

gösterilmiştir.

7-18

Şekil 7-2-2 Şekil 7-2-1’deki sayıcının zamanlama diyagramı

Şekil 4-27’den görülebildiği gibi, CK düşen kenarla tetiklendiği için, normal A,B,C

çıkışları yukarı doğru sayarken, tümleyen A,B,C çıkışları aşağı doğru saymaktadır.

A’nın periyodu CK’nın iki katı, frekansı ise CK’nın yarısıdır.

B’nin periyodu A’nın iki katı, frekansı ise A’nın yarısıdır.

C’nin periyodu B’nin iki katı, frekansı ise B’nin yarısıdır.

CK’nın yükselen-kenarla tetiklenmesi durumu için çıkış dalga şekilleri, Şekil 7-2-3’te

gösterilmiştir. Açıkça görüldüğü gibi, A,B ve C çıkışları yukarı doğru saymaktadır.

Şekil 7-2-4’teki devre, CK, Q çıkışına bağlıyken yukarı doğru, Q çıkışına bağlıyken aşağı doğru sayacaktır.

7-19

Şekil 7-2-3 Sayıcının zamanlama diyagramı (yükselen kenarla tetikleme)

Bu deneyde temel sayıcıları gerçeklemek için kullanılacak olan J-K flip-flop, genel bir

flip-floptur. Şekil 7-2-4’te gösterilen devre, J-K flip-flopların ardarda seri olarak

bağlanmasıyla elde edilmiş bir yukarı/aşağı sayıcıdır.

Şekil 7-2-4 Yukarı/aşağı sayıcı

M=0 iken, CK, Q çıkışına bağlanır ve devre “YUKARI” doğru sayar.

M=1 iken, CK, Q’ çıkışına bağlanır ve devre “AŞAĞI” doğru sayar.

Şekil 7-2-4’teki gibi seri bağlantılarla gerçekleştirilen devreler “Asenkron Sayma”

yapar. “n’e Bölme” etkisi’ni elde etmek için, çıkış “SİLME” ucuna bağlanmalıdır.

7-20

Şekil 7-2-5(a)’da, bir 5-e bölme devresi gösterilmiştir. Bu devrenin Şekil 7-2-5(b)’deki

doğruluk tablusundan, 5-e bölme devresi denilen bir çevrim oluşturacak şekilde, “0”

ve “5” durumlarının eşit olduğu görülmektedir.

(a) Lojik diyagram

(b) Doğruluk tablosu

Şekil 7-2-5 Silme girişli 5-e bölen sayıcı

Şekil 7-2-5(a)’da A ve C çıkışları, bir VE kapısıyla CL (SİLME) girişine bağlanmıştır.

“5” durumu 101’e karşılık olduğu için, CBA=101 olduğunda sayıcı sıfırlanır.

Asenkron N-e bölme işlemini gerçekleştirmenin bir başka yolu da, Şekil 7-2-6’da

gösterilen, 5’e bölen sayıcı devresidir. CBA=100 durumunda, C çıkışı, bir VE

kapısıyla, CL girişine bağlanmıştır. “SİLME” fonksiyonunun süresini uzatmak için, CL

girişine bir kondansatör bağlanır. Kondansatör, CK düşerken, “1” durumunu

sürdürerek, flip-flopu “SİLME” modunda tutmaya devam eder. CK’nın düşen

kenarında, sayıcı hala etkisiz durumdadır.

7-21

Şekil 7-2-6 Farklı bir, silme girişli 5-e bölen sayıcı, yöntemi

2-ye bölen ve 5-e bölen sayıcı devrelerinin seri olarak bağlanması, bir BCD sayıcı

oluşturur. 10-a bölen yada 6-ya bölen gibi endüstriyel sayıcıların, 60Hz’lik AC güçle

birlikte kullanılmasıyla, 1Hz’lik bir zamanlama sinyali üretilebilir. Eğer tüm CK girişleri

birbirine bağlıysa, bir senkron sayıcı elde edilmiş olur. Senkron sayıcıların çalışma

hızı, seri olarak bağlanmış asenkron sayıcılara göre çok daha yüksektir, ancak

senkron sayıcılarla, 2’nin kuvveti (2n) olmayan sayıcılar tasarlamak oldukça

karmaşıktır.

Şekil 7-2-7’de, 4-bitlik senkron sayıcı yada 16-ya bölen sayıcı gösterilmiştir.

Şekil 7-2-7 4-bitlik senkron sayıcı

Şekil 7-2-8’de, senkron 5’e bölen sayıcı devresi gösterilmiştir. Bu devrenin yapısının,

asenkron sayıcıdan daha karmaşık olduğu açıktır.

7-22

Şekil 7-2-8 Senkron 5-e bölen sayıcı

KULLANILACAK ELEMANLAR

1. KL-22001 Temel Elektrik Devreleri Deney Düzeneği

2. KL-26007 Ardışıl Lojik Devre Deney Modülü (2)

3. Osiloskop

DENEYİN YAPILIŞI

A. JK Flip-Floplar ile 8-e Bölen Sayıcı Gerçekleştirmek

1. Şekil 7-2-9’daki bağlantı diyagramına göre, gerekli bağlantıları yapın. +5VDC

sabit güç kaynağını, KL-26007 modülüne bağlayın.

2. CK girişini, SWA Darbe Anahtarının A çıkışına bağlayın.

3. Q1, Q2 ve Q3 çıkışlarını, sırasıyla L5, L6 ve L7 Lojik Göstergelerine bağlayın.

7-23

Şekil 7-2-9 Bağlantı diyagramı (KL-26007 blok c)

4. SWA Darbe Anahtarını kullanarak, CK girişine saat darbeleri uygulayın. Q1, Q2

ve Q3 çıkışlarını gözleyin ve Tablo 7-2-1’e kaydedin.

CK Q3 Q2 Q1

Tablo 7-2-1

B. JK Filip-Floplar ile Senkron Sayıcı Gerçekleştirmek

1. Şekil 7-2-10’daki bağlantı diyagramına göre, gerekli bağlantıları yapın. +5VDC

sabit güç kaynağını, KL-26007 modülüne bağlayın.

7-24

Şekil 7-2-10 Bağlantı diyagramı (KL-26007 blok c)

2. CK1 girişini, SWA Darbe Anahtarının A çıkışına bağlayın.

3. Q2 ve Q3 çıkışlarını, sırasıyla L6 ve L7 Lojik Göstergelerine bağlayın.

4. SWA Darbe Anahtarını kullanarak, CK1 girişine saat darbeleri uygulayın. Q2 ve

Q3 çıkışlarını gözleyin ve Tablo 7-2-2’ye kaydedin.

CK1 Q3 Q2

Tablo 7-2-2

7-25

C. 7490 ile 8-e Bölen Sayıcı Gerçekleştirmek

1. Şekil 7-2-11’deki bağlantı diyagramına göre, gerekli bağlantıları yapın. +5VDC

sabit güç kaynağını, KL-26007 modülüne bağlayın.

Şekil 7-2-11 Bağlantı diyagramı (KL-26007 blok b)

2. J girişini, SWA Darbe Anahtarının A çıkışına bağlayın.

3. A, B, C, D çıkışlarını sırasıyla L5, L6, L7, L8 Lojik Göstergelerine bağlayın.

4. SWA Darbe Anahtarını kullanarak, J girişine saat darbeleri uygulayın. A, B, C,

D çıkışlarını gözleyin ve Tablo 7-2-3’e kaydedin.

J D C B A

Tablo 7-2-3

7-26

D. 7490 ile BCD Sayıcı Gerçekleştirmek

1. Şekil 7-2-12’deki bağlantı diyagramına göre, gerekli bağlantıları yapın. +5VDC

sabit güç kaynağını, KL-26007 modülüne bağlayın.

Şekil 7-2-12 Bağlantı diyagramı (KL-26007 blok b)

2. J girişini, SWA Darbe Anahtarının A çıkışına bağlayın.

3. A, B, C, D çıkışlarını sırasıyla, D1 Dijital Göstergesinin A, B, C, D girişlerine

bağlayın.

4. SWA Darbe Anahtarını kullanarak, J girişine saat darbeleri uygulayın. D1 Dijital

Göstergesini gözleyin ve Tablo 7-2-4’e kaydedin.

J D1

Tablo 7-2-4