7.4 数据存储器的扩展

description

Transcript of 7.4 数据存储器的扩展

第 7章 AT89C51单片机系统扩展

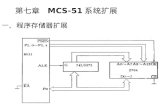

7.4 数据存储器的扩展 7.4.1 并行传送外部数据存储器的扩展方法 单片机和数据存储器的连接方法与程序存储器的

连接方法大致相同,主要区别在控制信号上。地址线、数据线均与程序存储器的连接方法一致。因为数据存储器既要读又要写,所以必须有控制读写的信号线。

图 7-7 是单片 SRAM6116(2 K×8 位 ) 的扩展连接图。

第 7章 AT89C51单片机系统扩展

图 7-7 AT89C51 与 6116 接口连接图

第 7章 AT89C51单片机系统扩展 7.4.2 串行传送数据存储器的扩展方法

1) 一般特性 AT24C01 是一种采用 CMOS 工艺制成的 128×8 位串行

可电擦除的可编程只读存储器,自动擦除时间不超过 10 ms ,典型时间为 5 ms 。

2) 引脚图及说明 AT24C01A 引脚图见图 7-8 ,各引脚功能如下: (1) SCL :串行时钟端,用于对输入和输出数据的同步。 (2) SDA :串行数据地址输入或输出端,串行双向数据

输入、输出端。

第 7章 AT89C51单片机系统扩展

8765

A0A1A2VSS

1234

VCC

WPSCLSDA

图 7-8 AT24C01A 引脚图

第 7章 AT89C51单片机系统扩展

(3) WP :写保护,硬件数据保护端接地时可对整个存储器进行正常读写,接电源时具有写保护功能。

(4) A0 、 A1 、 A2 :片选输入。 (5) VCC :电源端,接 +5 V 电源。 (6) VSS :接地端。

第 7章 AT89C51单片机系统扩展 3) 芯片操作 (1) 功能描述: AT24C01A 支持 I2C 双向二线制串

行总线及其传输规约。在串行 EEPROM 系统中,必须有一片可以产生串行时钟 (SCL) 的主器件控制,通常这个主器件就是单片机,控制其总线访问及产生“启动”和“停止”信号。

(2) 总线特性: I2C 双向二线制串行总线协议定义只有在总线处于“非忙”状态时,数据传输才能被初始化。

第 7章 AT89C51单片机系统扩展

SCL

SDA

A B D

Æô¶¯ÐźÅ

#Êý¾ÝµçƽÎȶ¨Êý¾Ý²ÅÓÐЧ

#Êý¾ÝÔÚ´ËÆÚ¼ä±ä»¯

Í£Ö¹ÐźÅ

D C A

图 7-9 AT24C01A 总线状态图

第 7章 AT89C51单片机系统扩展 ① A 段:总线非忙状态,在此期间 SDA 、 SCL 都

保持高电平。 ② B 段:启动数据传输,当 SCL 为高电平时, SD

A 由高电平变为低电平的下降沿被认为是“启动”信号,只有出现了启动信号后,其他命令才有效。

③ C 段:停止数据传输,当 SCL 为高电平时, SDA低电平的上升沿被认为是“停止”信号。

④ D 段:数据有效,在出现“启动”信号以后, SCL 为高电平且数据线稳定,这时数据线的状态表示要传送的数据。

第 7章 AT89C51单片机系统扩展

图 7-10 AT24C01A 控制字

第 7章 AT89C51单片机系统扩展

(3) 芯片寻址:当芯片接收到“启动”信号后,需要接收一个 8 位的控制字,控制字的格式如图 7-10 所示。

A2 、 A1 、 A0 三位地址与引脚上的 A2 、 A1 、 A

0 的接法 ( 接 VCC=1 ,接 VSS=0) 相比较,如果一致,该芯片被选通。所以一个总线上总共可以挂八个 AT24C01A 。

(4) 字节编程方式:在这种方式下,微处理器发送EEPROM 存储单元地址和一个字节数据至 EEPROM 。字节写入的帧格式见图 7-11 。

第 7章 AT89C51单片机系统扩展

S 1 0 1 0 X X XSDAÏß

Ö÷»úÆô¶¯ ¿ØÖÆ×Ö½Ú

Ó¦´ð

д

´æ´¢µ¥ÔªµØÖ·

Ó¦´ð

Êý¾Ý

Ó¦´ð

Í£Ö¹

P

WR/

图 7-11 AT24C01A 字节写入帧格式

第 7章 AT89C51单片机系统扩展

(5) 读操作:读操作分三种情况,即读当前地址存储单元的数据,读指定地址存储单元的数据,读连续存储单元的数据。

(6) AT89C51 与 AT24C01A 接口电路:因为 89C51 不带 I2C 总线,所以必须用 I/O 口来模拟 I2C 总线的工作时序。硬件接口见图 7-13 。

第 7章 AT89C51单片机系统扩展

S 1 0 1 0 X X XSDAÏß

Ö÷»úÆô¶¯ ¿ØÖÆ×Ö

Ó¦´ð

д

´æ´¢µ¥ÔªÖ¸¶¨µØÖ·

Ó¦´ð

Êý¾Ý

·ÇÓ¦´ð

Í£Ö¹

P

Æô¶¯ ¿ØÖÆ×Ö

Ó¦´ð

¶Á

1WR/ £½0WR/ £½

S 1 0 1 0 X X X

图 7-12 读 AT24C01A 指定地址存储单元数据的帧格式

第 7章 AT89C51单片机系统扩展

图 7-13 AT89C51 与 AT24C01A 的硬件接口连接图

第 7章 AT89C51单片机系统扩展

软件编程非常关键,一定要注意 P1.0 、 P1.1 的时序应严格符合 I2C 总线时序,否则 AT24C01A 将不能正常工作。以下给出用单片机模拟 I2C 总线时序的程序,此程序向 AT24C01A 指定地址写入一个字节数据。 30H 单元放要写入 AT24C01A 数据的地址, R0 放要写入的数据。

第 7章 AT89C51单片机系统扩展 程序如下:WROM : SETB P1.0

LCALL DELAY

SETB P1.1

LCALL DELAY

CLR P1.0

LCALL DELAY

CLR P1.1

LCALL DELAY

MOV R2 , #08H ;送写控制字MOV A , #0A0H

第 7章 AT89C51单片机系统扩展 WM2 : LCALL WRITE

LCALL DELAY

SETB P1.1

LCALL DELAY

CLR P1.1

LCALL DELAY

MOV R2 , #08H ;送写入数据的首地址MOV A , 30H

LCALL WRITE

LCALL DELAY

第 7章 AT89C51单片机系统扩展 SETB P1.1

LCALL DELAY

CLR P1.1

LCALL DELAY

MOV R2 , #08H ;连续放一个字节的数据 MOV A , R0

LCALL WRITE

CLR P1.0

LCALL DELAY

SETB P1.1

LCALL DELAY

CLR P1.1

第 7章 AT89C51单片机系统扩展 LCALL DELAY

WM : SETB P1.1 ;给出停止信号LCALL DELAY

SETB P1.0

LCALL DELAY

RET

WRITE : CLR C ;写入数据子程序

第 7章 AT89C51单片机系统扩展 RLC A

MOV P1.0 , C

LCALL DELAY

SETB P1.1

DJNE R2 , WRITE

RET

DELAY : MOV R3 , #1FH ;延时子程序 DELY : DJNE R3 , DELY

RET

第 7章 AT89C51单片机系统扩展

7.5 I/O 口的扩展 7.5.1 简单 I/O 口的扩展 只要根据“输入三态,输出锁存”的原则,选择 74

系列的 TTL 电路或 MOS 电路就能组成简单的扩展电路,如 74LS244 、 74LS273 、 74LS373 、 74LS377 等芯片都能组成输入、输出接口。

第 7章 AT89C51单片机系统扩展 对于 AT89C51 单片机,外部 I/O 接口和外部 RAM

是统一编址的,也就是说它们共用 64 K 存储空间。每个扩展 I/O 接口相当于一个扩展的外部单元,因此,访问外部接口就如同访问外部 RAM 一样,用的都是MOVX 指令, MOVX 指令产生的 、 信号可以对 I/O 口进行读写。图 7-14 给出了一个用 8 位三态缓冲器 74LS244 作为输入口和八 D 锁存器 74LS273 作为输出口组成的简单 I/O 口扩展电路。

RD WR

第 7章 AT89C51单片机系统扩展

图 7-14 简单 I/O 口扩展图

第 7章 AT89C51单片机系统扩展 在图 7-14 中,输出电路控制采用 P2.0 和的组合信号。

当 P2.0 和都为 0 时,或门输出为 0 ,将 P0 口数据锁存到 74LS273 ,其 Q 端控制发光二极管 LED;当某个 Q端为 0 时,与其相连的发光二极管被点亮。

第 7章 AT89C51单片机系统扩展 按照图 7-14 ,若让某一个按键按下,对应的发光二极管亮,程序如下:

LOOP : MOV DPTR , #0FEFFH ;置 I/O 口地址 MOVX A , @DPTR ;产生 读入键值 MOVX @DPTR , A ;产生 输出信号 AJMP LOOP ;循环7.5.2 可编程 I/O 口的扩展 1. 8255 的内部结构 8255 是一个可编程并行 I/O 口芯片,由以下四个逻辑结构组成,逻辑结构图如图 7-15 所示。

RD

WR

第 7章 AT89C51单片机系统扩展

图 7-15 8255内部结构框图

第 7章 AT89C51单片机系统扩展 (1) 数据总线驱动器:具有双向三态的 8 位驱动器,用于

和单片机数据总线相连,以实现单片机与 8255 数据的传送。 (2) 并行 I/O 端口:共有三个并行端口,分别是 A 口、 B

口、 C 口。 (3) 读写控制逻辑:用于管理所有的数据、控制字或状态

字的传送。 (4) A 组、 B 组控制块:用于接收来自读、写控制逻辑命

令和内部数据总线的控制字,并向对应口发出操作命令。2. 8255 的引脚介绍 8255 是一个具有 40 个引脚的 DIP封装的芯片,引脚图见

图 7-16 。

第 7章 AT89C51单片机系统扩展 1234567891011121314151617181920

4039383736353433323130292827262524232221

PA4PA5PA6PA7WRRESETD0D1D2D3D4D5D6D7VCCPB7PB6PB5PB4PB3

PA3PA2PA1PA0RDCS

GNDA1A0

PC7PC6PC5PC4PC0PC1PC2PC3PB0PB1PB2

图 7-16 8255 引脚图

第 7章 AT89C51单片机系统扩展 引脚功能介绍如下: (1) PA0~ PA7 : A 口,具有 8 位数据输出锁存

器 / 缓冲器和一个 8 位数据输入锁存器。 (2) PB0~ PB7 : B 口,具有 8 位数据输出锁存

器 / 缓冲器和 8 位数据输入缓冲器 ( 不锁存 ) 。 (3) PC0~ PC7 : C 口,具有 8 位数据输出锁存器 /

缓冲器和 8 位数据输入缓冲器 ( 不锁存 ) ,该口可分为两个 4 位口使用,它除了作为输入 / 输出口外,还可以作为 A 口、 B 口选通工作方式操作时的状态控制信号。

第 7章 AT89C51单片机系统扩展 (4) :读控制端,低电平有效,允许从 8255 读取

数据或状态字。 (5) :写控制端,低电平有效,允许向 8255 写入

数据或控制字。 (6) :片选端,低电平有效。 (7) A0 、 A1 :口地址选择端,通过 A0 、 A1 可选

中 8255 的四个寄存器,每个寄存器口地址见表 7-3 。 (8) RESET :复位控制端,当 RESET=1 时, 8255复位,通常与单片机的复位端直接相连。

RD

WR

SC

第 7章 AT89C51单片机系统扩展 3. 8255 的操作方式 8255 的全部工作状态是通过读 / 写控制逻辑和工作方

式选择来实现的。 1) 读 / 写控制逻辑操作选择 由单片机输出的地址线 A0 、 A1 及 、 、 来

选择口的操作状态,具体说明如表 7-3 所示。RD WR SC

第 7章 AT89C51单片机系统扩展 表 7-3 8255A 控制信号功能表

第 7章 AT89C51单片机系统扩展

第 7章 AT89C51单片机系统扩展

2) 8255 三种工作方式的功能 8255 有三种工作方式,分别是方式 0 、方式 1 和方

式 2 ,它们是通过程序对控制口送控制字来选择的,下面分别介绍三种工作方式:

(1) 方式 0 :基本 I/O 方式。 (2) 方式 1 :单向选通 I/O 方式。 (3) 方式 2 :双向总线方式。

第 7章 AT89C51单片机系统扩展

3) 8255 的编程选择控制字 8255 的传输方式和工作方式的选择是通过对控制口

输入控制字的方式实现的。 8255 的控制字有两种:方式选择控制字和 C 口位操作控制字。

方式选择控制字为 8 位,每一位都有固定含义,用于选择每个口的工作方式和数据传输方向,具体定义见图 7-17 。

第 7章 AT89C51单片机系统扩展

B×é

C¿ÚµÄµÍ4λ1£ºÊäÈë0£ºÊä³ö

B¿Ú1£ºÊäÈë0£ºÊä³ö

¹¤×÷·½Ê½Ñ¡Ôñ0£º·½Ê½01£º·½Ê½1

A×é

C¿ÚµÄ¸ß4λ1£ºÊäÈë0£ºÊä³ö

A¿Ú1£ºÊäÈë0£ºÊä³ö

¹¤×÷·½Ê½Ñ¡Ôñ00£º·½Ê½001£º·½Ê½11X£º·½Ê½2

¹¤×÷·½Ê½±êÖ¾1£ºÓÐЧ

D7 D6 D5 D4 D3 D2 D1 D0

图 7-17 8255 方式选择控制字

第 7章 AT89C51单片机系统扩展 位控制字用于对 C 口进行位操作。 C 口不仅在方式

0 下具有并行数据传输功能,还可以进行位操作。把一个置“ 1” 或置“ 0” 的控制字送入 8255 的控制口,就能把 C 口的某一位置 1 或清 0而不影响其他位的状态,位操作控制字格式见图 7-18 。

第 7章 AT89C51单片机系统扩展

ÖÃλ»ò¸´Î»

0£º¸´Î»1£ºÖÃλ

D7 D6 D5 D4 D3 D2 D1 D0

λѡÔñ

D3D2D1 C¿Ú

000001010011100101110111

PC0PC1PC2PC3PC4PC5PC6PC7

¿ØÖÆÑ¡Ôñ

0£ºÎ»²Ù×÷

ûÓÃ

图 7-18 8255 C 口置 /复位控制字

第 7章 AT89C51单片机系统扩展

4. AT89C51 与 8255 的接口电路 在 89C51 单片机的 I/O 口上扩展 8255 芯片,硬件连

接图比较简单。在图 7-19 中, 8255 的片选及口地址选择线 A0 、 A1 分别由单片机的 P0.7 、 P0.0 、 P0.1经地址锁存后提供,故 8255 的 A 、 B 、 C 口及控制口的地址分别为 FF7CH 、 FF7DH 、 FF7EH 、 FF7FH( 当然这不是惟一的连接方法,与单片机不同的地址线相连, 8255 的口地址也不会相同 ) 。数据线直接与单片机的数据线相连, 、 也直接连在单片机的 、 端。

RD WR RD WR

第 7章 AT89C51单片机系统扩展

89C51 74LS373

8255

PC0PC1PC2PC3PC4PC5PC6PC7

PB0PB1PB2PB3PB4PB5PB6PB7

PA0PA1PA2PA3PA4PA5PA6PA7

D0D1D2D3D4D5D6D7

D0D1D2D3D4D5D6D7

Q0Q1Q2Q3Q4Q5Q6Q7

G OE

ALE

WRRD

WRRD

RESET

A1A0P0.0

P0.1P0.2P0.3P0.4P0.5P0.6P0.7

CS

图 7-19 8255 与 AT89C51 连接图

第 7章 AT89C51单片机系统扩展

[例 7.1] 如图 7-19 所示,用 8255 扩展单片机并行I/O 口并读、写数据。要求 8255 工作在方式 0 ,且 A口作为输入, B 口、 C 口作为输出。

分析:从图 7-19 可知, 8255 的 A 、 B 、 C 、控制口的地址分别为 FF7CH 、 FF7DH 、 FF7EH 、 FF7FH 。编程时,应先按题目要求对 8255 初始化设置每个口的工作方式,然后再使数据输入、输出。程序如下:

第 7章 AT89C51单片机系统扩展 MOV A , #90H ; A 、 B 、 C 口方式 0 , A 口输入, B 、 C 口

输出MOV DPTR , #0FF7FH ;MOVX @DPTR , A ;方式控制字→控制寄存器MOV DPTR , #0FF7CH

MOVX A , @DPTR ;从 A 口读取数据MOV DPTR , #0FF7DH

MOV A , #DATA1

MOVX @DPTR , A ;将数据 DATA1 从 B 口输出MOV DPTR , #0FF7EH

MOV A , #DATA2

MOVX @DPTR , A ;将数据 DATA2 从 C 口输出

第 7章 AT89C51单片机系统扩展

[例 7.2] 对 C 口的位操作,把 PC5置 1 ,再把 PC5复位,程序如下:

MOV DPTR , #0FF7FH ;控制口地址→ DPTR

MOV A , #0BH ; PC5 置 1 的控制字→ A

MOVX @DPTR , A ;控制字→控制口, PC5=1

MOV A , #0AH ; PC5 复位的控制字→ A

MOVX @DPTR , A ;控制字→控制口, PC5=0