06139542

-

Upload

raveendhra-iitr -

Category

Documents

-

view

218 -

download

0

Transcript of 06139542

-

8/11/2019 06139542

1/5

Robust Digital Voltage-Mode Controller Design

For Split-Inductor SEPIC ConverterM. Veerachary

Dept. of Electrical Engineering, IIT Delhi, Hauz Khas, New Delhi, INDIA

E-mail: [email protected]

Abstract- In this paper a robust digital voltage-mode controllerdesign is designed for a split inductor SEPIC converter toachieve load voltage regulation. Split-inductor SEPIC convertersalient features are compared with the conventional SEPICconverter and then discrete-time mathematical models areestablished. Digital controller is designed using discrete-timemodel through direct digital design approach. A two-pole two-zero compensator is adopted in the design and then an edge

theorem is employed for testing the robustness of the controller.Compensator design is validated through simulations and thenexperimental measurements. Load voltage regulationcharacteristics are obtained against line and load perturbations.A 15 to- 36 V,25 Watt laboratory prototype converter is builtfor experimental investigations. Simulation and experimentalresults are demonstrating the robustness feature of the designeddigital controller.

I. INTRODUCTION

Switch-mode power conversion application is increasing

in the low power compact electronic circuits. To realize

compact power supply system, increasing the power density

is one of the challenging issues for the power supply

designers. One of the main orientations in power electronics

in the last decade has been the development of switching-

mode converters with higher power density and low

electromagnetic interference (EMI). Light weight, small size

and high power density are also some of the key design

parameters [1]-[3].

High frequency switch-mode power supplies are becoming

an integral part of many power electronic systems [1] and the

dc-dc converters are mainly used in these application areas.

Technological developments are is taking place in order to:

(i) improve converter performance, (ii) achieve better

reliability, and (iii) increasing the power density, etc. The

aspect of increasing the power density is mainly related to the

converter design and packaging. Performance improvementof the dc-dc converter topologies is broadly classified into

two different categories, which are: (i) steady-state

performance, and (ii) dynamic performance. Among these

two, the converter system dynamic performance mainly

governed by the type of controller used. Conventional SEPIC

converter based topologies are well established for

applications requiring both bucking and boosting the up-

stream voltages. However, in the applications where the

voltage gain requirement is higher, not possible to realize

with single conventional converter, then there are two

alternate solutions, which are: (i) cascading the boost

converters, (ii) cascading the SEPIC converters. Although

these methods are capable of resulting higher transformation

ratios, but more number of components are required for their

realization and also results in lesser efficiency. Some times to

realize the predefined transformation ratio the converter

needs to be operated at the extreme duty ratios wherein the

device utilization is poor with increased thermal loading. In

order to alleviate some of these limitations coupled inductor

boost converters and quadratic topologies have been proposed

in the literature [1]-[4]. However, more device stress is the

major limitation of these topologies. By using the split-inductor [2] concept it is possible to increase the voltage gain

of the conventional SEPIC converter. In this paper the input

side inductance of the conventional SEPIC converter has been

replaced with split inductor, and then voltage transformation

properties, load voltage regulation, and robustness issues

have been addressed.

The dynamic performance and its robustness are primarily

decided by the control strategy employed for a particular

topology. The two most commonly used control schemes in

dc-dc switching power converters are: (i) voltage-mode

control, (ii) two-loop current-mode control. It is well knownthat the voltage-mode control is slow in its response against

supply disturbances on account of single-loop voltage

feedback. On the other hand the two-loop control strategy,

inner current mode control together with outer voltage loop,

results in faster dynamic response. However, selection of a

particular control scheme is essentially decided by the

complexity and cost trade-offs requirements together with

robustness requirements dictated by the end-user.

Considering robustness as the requirement a single-loop

digital voltage-mode controller is designed in this paper for

the split-inductor SEPIC (SI-SEPIC) converter and detailed

design methodology is given in the following paragraphs.

2 2,L r

3

3

,

L

r

1 1, cC r

0

0

,

c

C

r1 1,L r

Fig. 1. SI-SEPIC circuit diagram

-

8/11/2019 06139542

2/5

II.STEADY-STATE ANALYSIS AND DISCRETE-TIME MODELFORMULATION OF THE SPLIT-INDUCTOR SEPIC

CONVERTER

The split-inductor SEPIC converter is shown in Fig. 1.

This converter is derived from the conventional SEPIC

converter where-in the source side inductance is divided into

two halves and then arranged in a bridge form using twoadditional diodes as shown in Fig. 1. The main purpose of

such split inductance is to provide additional boosting in the

load voltage. In comparison to the conventional SEPIC

converter, as it is indicated within the box, it consists of three

additional diodes (D1, D2 and D3) and inductors (L1,L2). Due

to this structural arrangement the circuit exhibits more

important features as compared to the conventional SEPIC

converter, which are: (i) the SI-SEPIC is capable of giving

higher load voltage boosting at lower duty ratios, (ii) switch

voltage/current stress is almost same as conventional

converter, and (iii) inductance requirement is almost same asthe conventional converter. Steady-state performance

comparison of this converter with conventional SEPIC

converter is given in Table I for ready reference.

This SI-SEPIC can operate either in continuous or

discontinuous inductor current mode of operation. However,for a given power rating and boosting factor requirement the

source current magnitude is high for most of the loading

conditions and correspondingly the current is continuous in

all the three inductors. In view of this, the SI-SEPIC analysis

as well as its discrete-time model formulation is discussed

here for the continuous inductor current mode of operation.As stated earlier the high voltage gain of this converter is

mainly due to the presence of the split inductors (L 1, L2),

while there is no change in the load side ripple current as

there is no structural change in the circuit configuration. The

split inductor combination will draw the energy from the dc-

voltage source during switch-ON time period and then pumps

into the load for the remaining time period. In this process the

split inductors will be connected in series during the switch-

OFF period contributing to additional boosting as compared

to conventional SEPIC converter.

A. Converter parameter Design Equations

A steady-state analysis of the SI-SEPIC is established in

this section and the analysis is based on the following

simplifying assumptions: (i) switching devices are ideal, and

effect of non-idealities of the passive and energy storage

components on the steady-state performance is negligible, (ii)ripple current/ voltage magnitude is very small, (iii) converter

time constant is very high as compared to the switching

period, and (iv) non-idealities of the energy storage elements

are neglected. By employing the kirchoffs voltage and

current laws the steady-state relationships among the various

voltage and currents are established. Assuming voltage drops

across inductors L1, L2 are same, various voltages across

inductor elements L1, L2 and L3 during switch-ON/OFF

periods respectively are:

Inductor ON-time OFF-Time

L1 Vg (Vg- Vc- Vo)/2

L2 Vg (Vg- Vc- Vo)/2L3 Vc -Vo

0v

Fig. 2. Control block diagram of voltage-mode controlled SI-SEPIC.

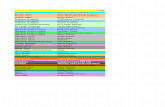

TABLEIPERFORMANCE COMPARISON

SEPIC SI-SEPIC

Voltage gain Low High

Efficiency Moderate Moderate

Transient response Moderate Low

Switching stresseson elements

High Low

Applying volt-sec balance to the inductors L1, L2 and L3and

then simplifying results in the following voltage

transformation ratio [7] for the converter.

( )

( )0

1

1 -g

D DV

V D

+=

(1)

Using the power balance, VgIg=V0I0, and time-domain

analysis the SI-SEPIC design equations are established. The

minimum and maximum inductor current expressions can

easily be obtained by using the ripple quantities,

L1 g 1i V DT L ; = L2 g 2i V DT L = and the capacitor

voltage ripple relationships are:

C1 L2 1V I DT C , =2

C0 g 2 0V V (DT) (8L C ). = These

expressions together with current/ voltage ripple requirements

give the basis for the design of energy storage componentsL1, L2, L3and C1, C2.

B. State-space Models For Continuous Inductor Current

Mode of Operation

Application of state-space modeling is widely used in the

switch-mode power conversion systems. Conventionally, thediscrete-time models are obtained through suitable

transformation applied to the state-space models. However,

accuracy of such discrete-time models mainly governed by

the type of transformation used and the switching frequency

employed. In ref[4] discrete-time modeling of digitally

controlled converters has been reported, where-in it has been

demonstrated that it is possible to include type of pulse width

modulation strategy as well as the sampling instant

information in the model itself. This methodology is used to

formulate the discrete-time model for the proposed SI-SEPIC

operating at trailing-edge OFF-time sampling [7]. In

continuous inductor current mode of operation the circuit has

two operating modes; Mode-1: S-ON (0

-

8/11/2019 06139542

3/5

linear, and its behavior can easily be described by the state-

space model [13] given by

[ ] [ ] [ ]

[ ] [ ]( 1)

j j

j j

j

x A x B ut t t

y E x+

= +