陳慶瀚 機器智慧與自動化技術 (MIAT) 實驗室 國立中央大學資工系 2009 年 10...

-

Upload

alysha-haught -

Category

Documents

-

view

249 -

download

13

Transcript of 陳慶瀚 機器智慧與自動化技術 (MIAT) 實驗室 國立中央大學資工系 2009 年 10...

陳慶瀚機器智慧與自動化技術 (MIAT)實驗室國立中央大學資工系2009 年 10 月 15日

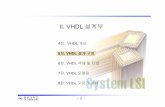

ESD-05Grafcet-to-VHDL 硬體合成

Grafcet-to-VHDL Hardware Synthesis

VHDL template

VHDL synthesis of Grafcet

X0

R0

Xn

A0

An

if X0='1' and R0='1' then X0<='0'; Xn<='1';end if;

A0 <= X0 ;An <= Xn ;

Fundamental Block

Convergence AND

if X0='1' and X1='1' and R0='1' then X0<='0'; X1<='0'; Xn<='1';end if;

A0 <= X0 ;A1 <= X1 ;An <= Xn ;

Xn

R0

X0

An

A0 X1 A1

VHDL synthesis of Grafcet

Divergence AND

VHDL synthesis of Grafcet

X0

R0

X1

A0

A1 Xn An

if X0='1' and R0='1' then X0<='0'; X1 <='1'; Xn<='1';end if;

A0 <= X0 ;A1 <= X1 ;An <= Xn ;

Convergence OR

VHDL synthesis of Grafcet

if X0='1' and R0='1' then X0<='0'; Xn <='1';elsif X1='1' and R1='1' then X1<='0'; Xn <='1';end if;

A0 <= X0 ;A1 <= X1 ;An <= Xn ;

Xn

R0

X0

An

A0 X1 A1

R1

Divergence OR

VHDL synthesis of Grafcet

X0

R0

X1

A0

A1 Xn An

if X0='1' and R0='1' then X0<='0'; X1 <='1';elsif X0='1' and R1='1' then X0<='0'; Xn <='1';end if;

A0 <= X0 ;A1 <= X1 ;An <= Xn ;

R1

Complete Synthesis of Grafcet Model

Synthesis of Grafcet Controller

X1 A1=1

S1

X2 A2=1

S2

X3 A3=1

S3

(a) (b)

VHDL code of Grafcet Controllerlibrary IEEE; use IEEE.std_logic_1164.all; entity DEMO1 is port ( CLK: in STD_LOGIC; RESET: in STD_LOGIC; S1: in STD_LOGIC; S2: in STD_LOGIC; S3: in STD_LOGIC; A1: out STD_LOGIC; A2: out STD_LOGIC; A3: out STD_LOGIC ); end DEMO1; architecture DEMO1_arch of DEMO1 is signal X1,X2,X3:STD_LOGIC; begin process(CLK) begin if RESET='1' then X1<='1'; X2<='0'; x3<='0'; elsif CLK'EVENT and CLK='1' then if X1='1' and S1='1' then X1<='0';X2<='1'; end if; if X2='1' and S2='1' then X2<='0';X3<='1'; end if; If X3='1' and S3='1' then X3<='0';X1<='1'; end if; end if; A1<=X1; A2<=x2; A3<=X3; end process; end DEMO1_arch;

(c)

VHDL synthesis of Grafcet Controller

VHDL synthesis of Grafcet Controller

library ieee;use IEEE.STD_LOGIC_1164.all; entity g0 is port( clk : in std_logic; rst : in std_logic; OK : in std_logic; L1,L2 : in std_logic; V1,V2 : out std_logic; Start_M : out std_logic; Stop_M : out std_logic);end g0;

architecture miat of g0 is signal s0,s1,s2,s3,s4 : std_logic;

begin process(clk,rst) begin if rst='0' then s0<='1'; s1<='0'; s2<='0'; s3<='0'; s4<='0'; elsif clk'event and clk='1' then if s0='1' and OK='1' then s0<='0'; s1<='1'; elsif s1='1' and L1='1' then s1<=‘0’; s2<=‘1’; s3<=‘1’; elsif s2='1' and s3='1' and L2='1' then s2<=‘0’; s3<=‘0’; s4<=‘1’; elsif s4='1' then s4<=‘0’; s0<=‘1’; end if; end if; end process; V1<=s1; Start_M<=s2; V2<=s3; Stop_M<=s4;END miat;

Synthesized Circuit Block Diagram

Simulated Timing Diagram

Synthesis of Microprogram Controller

Microprogram controller is control unit is responsible for coordinating actions within the CPU. The control unit decodes the instruction and issue a set of control signals that result in the instruction’s execution. These control signals cause data to be routed correctly within the CPU, generate correct external control signals, such as RD and WR in the 8085, and cause the ALU to perform the correct operation on the data.

Conventional Architecture Design

New Approach for Microprogram Controller Design

1. Instruction Design

2. Behavioral Description

3. GRAFCET Modeling

4. High-Level SynthesisGRAFCET Controller Synthesis

Datapath Synthesis

System Synthesis

Hardware Architecture Template

GRAFCET控制器

Datapath

Instruction Design

F3f2 f1 f0 指令 Operan

d功能說明

0 0 0 0 LD (addr) 從 RAM 的 addr 位址載入資料到 ACC

0 0 0 1 AND (addr) 從 RAM 的 addr 位址載入資料與 ACC 做 AND運算,結果放在 ACC

0 0 1 0 OR (addr) 從 RAM 的 addr 位址載入資料與 ACC 做 OR 運算,結果放在 ACC

0 0 1 1 ANDC (addr) 從 RAM 的 addr 位址載入資料,將之反相並與ACC 做 AND 運算,結果放在 ACC

0 1 0 0 STORE

(addr) 將 ACC 資料存放

0 1 0 1 JMP [addr] 程式無條件跳躍 ( 改變程式計數器 (PC) 值為addr)

0 1 1 0 JMPA [addr] 如果 ACC 為 1 ,程式跳躍 ( 改變程式計數器(PC) 值為 addr)

0 1 1 1 STOP [0] 結束

GRAFCET Modeling

0

1

0

85432 6 7 9

c3 c4 c5 c6 c7 c8 c9 c10

c2 : OP=LD(000)c3 : OP=AND(001)c4 : OP=OR(010)c5 : OP=LANDC(011)c6 : OP=STORE(100)c7 : OP=JMP(101)c8 : OP=JMPA(110)c9 : OP=STOP(111)

Acc<=0; PC<=0

Get OP(PC) ; Get Addr(PC)

10 PC++

VHDL Synthesis of Grafcet Controllergrafcet:PROCESS(CLK,RST)BEGIN

IF RST='1' THENX0<='1';X1<='0';X2<='0';X3<='0'; X4<='0';X5<='0';X6<='0';X7<='0';X8<='0';X9<='0';X10<='0';ELSIF CLK'EVENT AND CLK='1' THEN

IF X0='1' THEN X0<='0'; X1<='1';ELSIF X1='1' THEN

IF OP="000" THEN X1<='0'; X2<='1';ELSIF OP="001" THEN X1<='0'; X3<='1';ELSIF OP="010" THEN X1<='0'; X4<='1';ELSIF OP="011" THEN X1<='0'; X5<='1';ELSIF OP="100" THEN X1<='0'; X6<='1';ELSIF OP="101" THEN X1<='0'; X7<='1';ELSIF OP="110" THEN X1<='0'; X8<='1';ELSIF OP="111" THEN X1<='0'; X9<='1';END IF;

ELSIF X2='1' THEN X2<='0';X10<='1';ELSIF X3='1' THEN X3<='0';X10<='1';ELSIF X4='1' THEN X4<='0';X10<='1';ELSIF X5='1' THEN X5<='0';X10<='1';ELSIF X6='1' THEN X6<='0';X1<='1';ELSIF X7='1' THEN X7<='0';X1<='1';ELSIF X8='1' THEN X8<='0';X1<='1';ELSIF X9='1' THEN X9<='0';X0<='1';ELSIF X10='1' THEN X10<='0';X1<='1';END IF;

END IF;END PROCESS grafcet;

Synthesis of Datapath Module datapath:PROCESS(CLK,RST) BEGIN

IF X0='1' THEN ACC<='0';PC<=0;RAM<="10000001";ELSIF X1='1' THEN OP<="000";ADDR<=0;ELSIF X2='1' THEN ACC<=RAM(ADDR);ELSIF X3='1' THEN ACC<=ACC AND RAM(ADDR);ELSIF X4='1' THEN ACC<=ACC OR RAM(ADDR);ELSIF X5='1' THEN ACC<=NOT(RAM(ADDR));ELSIF X6='1' THEN RAM(ADDR)<=ACC;ELSIF X7='1' THEN PC<=ADDR;ELSIF X8='1' THEN

IF ACC='1' THEN PC<=ADDR; END IF;ELSIF X9='1' THEN PC<=0;ELSIF X10='1' THEN PC<=PC+1;END IF;

END PROCESS datapath;OUTPUT<=ACC;

END arch;

Complete Architecture Synthesis

architecture arch of microp2 isSIGNALX0,X1,X2,X3,X4,X5,X6,X7,X8,X9,X10:STD_LOGIC;SIGNAL ACC : STD_LOGIC;SIGNAL RAM : STD_LOGIC_VECTOR(7 downto 0);SIGNAL PC : INTEGER RANGE 0 TO 15;SIGNAL ADDR : INTEGER RANGE 0 TO 7;SIGNAL OP : STD_LOGIC_VECTOR(2 downto 0);

BEGIN grafcet:PROCESS(CLK,RST)... datapath:PROCESS(CLK,RST)... OUTPUT<=ACC;END arch;