원전 I&C 시스템 적용 FPGA 제어기 개발 · FLC(FPGA-based Logic Controller) Diagram...

Transcript of 원전 I&C 시스템 적용 FPGA 제어기 개발 · FLC(FPGA-based Logic Controller) Diagram...

http://www.wooriTG.com

2013. 11. 08

ISO9001-KSA9001 Excellent Korean Technology

Excellent Korean Technology New Technology Superior New-Tech.

원전 I&C 시스템 적용 FPGA 제어기 개발

㈜우리기술 정승권

http://www.wooriTG.com

아날로그

시스템

- 2 -

복잡도

(Complexity)

용량 (Capacity)

마이크로프로세서

시스템

FPGA

시스템

원전 I&C 시스템에 사용되는

하드웨어 Technologies

Analog/digital component 기

반 시스템에서 Microprocessor

기반 시스템으로 바로 진화

최근 FPGA 기반 시스템 적용

1. FPGA 개요

http://www.wooriTG.com

• AND, OR 게이트와 플립플롭 등의 기본 논리 소자들이 연결되지 않은 상태

– 설계 구현 후 소자들이 연결되어 logic을 수행

• 더 복잡한 FPGA는 메모리 블록과 마이크로 프로세서도 내장 가능

• 기본 소자들의 연결은 EDA 툴을 사용하여 설계/구현

• FPGA의 연결 정보를 저장 (memorize)하는 방법

– SRAM, Flash, Antifuse

• FPGA는 집적된 디지털 하드웨어로 동작 (그러나 소프트웨어로 설계)

=> Pure hardware during operation

FPGA (Field Programmable Gate Array)

Configurable Logic Block

1. FPGA 개요

- 3 -

http://www.wooriTG.com - 4 -

5. FIMS 데모 시나리오 #1

Microprocessor vs FPGA

특성 Microprocessor FPGA

동작구현 ALU 의 순차적 수행 Gate 연결에 의한 신호 생성

Code & Data 메모리 Gate Cell

신호생성 순차적 병렬적

실행속도 고속 초고속

기능용량 제한 없음 제한적

주변회로 복잡 간단

Language C, Assembly VHDL, Verilog

Targeting

Compile - C를 기계어로 변경 Synthesis - HDL을 로직으로 변경

Link - Target IC에 맞는 실행 코드 연결 P&R – Target IC 에 맞게 Gate의 연결관계 생성

코드 이식 주변 장치 Device Driver 이식 어려움 HW 기능이 코드화 되어 이식 가능

시스템 응용 범위 대규모, 다기능 MMI, 네트워크, 범용 소규모, 고속, 전용

1. FPGA 개요

http://www.wooriTG.com - 5 -

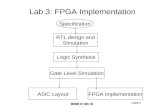

2-1. FLC 구조

FLC(FPGA-based Logic Controller) Diagram

공용 버스(I/O 버스)로 연결되는 기능별 모듈 구현

Logic Processing Module 이중화 구성 가능

범용성을 위한 기능별 FPGA 분리

Applica

-tion

FPGA

Admin

Block

Comm

Block

I/O Bus

Digital

Input

Part

DI

Control

Part

Analog

Input

Part

AI

Control

Part

Digital

Output

Part

DO

Control

Part

Analog

Output

Part

AO

Control

Part

PSM DIM AIM LPM AOMDOM

DI TB

Part

AI TB

Part

DO TB

Part

AO TB

Part

Applica

-tion

FPGA

Admin

Part

Comm

Part

Power

Supply

Part

LPM

Rear

Part

http://www.wooriTG.com - 6 -

2-2. LPM(Logic Processing Module)

Application FPGA

설계자 정의 Configuration

설계자 정의 제어 로직 수행

ADMIN FPGA

동작 스케쥴링

입출력 보드들과의 데이터 인터

페이스

통신 인터페이스

Main/Backup 전환

LPM 자체 진단

COM/NET FPGA

UART 프로토콜 구현

다수의 1:1 통신 채널 제공

FApp

I/O Bus

Com Bus

FCom FNet

FAdmin FIn FOut

Dual-Port

RAM

Net Bus

FPGA 구분으로 복잡도 증가하지만, 검증 작업을 최소화 함

http://www.wooriTG.com - 7 -

2-3. AIM(Analog Input Module)

Analog Input Control & Processing

Field AnalogConversion

IsolationBus

Interface

24 Channel Input

I/O Bus

Field AnalogValue

I/O Bus

입력 사양

24채널 0~10V / 4~20m, ±0.1% Accuracy, ±0.2% drift

60Hz 필터링 (common mode 90dB, normal mode 60dB)

±30VDC 과전압 입력 보호

Calibration

수동 보정: 외부 Reference 에 의한 보정

자동 보정: 내부 Reference 에 의한 보정

진단 기능

입력 회로 진단: 내부 Reference 값 확인

인터페이스 진단: 데이터 checksum, Parity, Heart-bit

FPGA 동작 진단: Watch Dog

http://www.wooriTG.com - 8 -

2-4. DIM(Digital Input Module)

Digital Input Control

Field ContactDetection

Isolation

LED Indication

BusInterface

32 Channel Input

I/O Bus

Field Discrete Contact

입력 사양

격리된 32채널 입력

Loop Power 24V, 48V

Programmable debouncing time

진단 기능

입력 회로 진단: 내부 switch 전환, 내부 테스트 신호 입력 확인

인터페이스 진단: 데이터 checksum, Parity, Heart-bit

FPGA 동작 진단: Watch Dog

http://www.wooriTG.com - 9 -

2-5. AOM(Analog Output Module)

Analog Input Control & Processing

Analog Output

IsolationBus

Interface

16 Channel Output

I/O Bus

Field AnalogOutput

출력 사양

16채널 0~10V / 4~20m, ±0.1% Accuracy, ±0.2% drift

Calibration

수동 보정: 외부 Reference 에 의한 보정

자동 보정: 내부 Reference 에 의한 보정

진단 기능

출력 회로 진단: 출력값 피드백 확인, 출력 Reference 확인

인터페이스 진단: 데이터 checksum, Parity, Heart-bit

FPGA 동작 진단: Watch Dog

이상 감지 시 Safety 상태 출력

http://www.wooriTG.com - 10 -

2-6. DOM(Digital Output Module)

Digital Input Control & Processing

ContactOutput

Isolation

LED Indication

BusInterface

24 Channel Output

I/O Bus

Field ContactOutput

입력 사양

격리된 24채널 접점 출력

Solid-state Relay 출력 – AC, DC 가능

진단 기능

입력 회로 진단: 출력값 피드백 확인,

인터페이스 진단: 데이터 checksum, Parity, Heart-bit

FPGA 동작 진단: Watch Dog

이상 감지 시 Safety 상태 출력

http://www.wooriTG.com - 11 -

3-1. Application Programming

Application FPGA, Admin FPGA, 통신(Com, Net) FPGA 나누어 구현하여 범용성 향상

Application 대상에 따라 Application FPGA 코드만 새로 작성

Application FPGA는 입출력 값과 상태 정보값의 Mirror Image를 내부 메모리에 가짐

Mirror Image 의 데이터 구조 정의되어, Admin FPGA에 의해 데이터 갱신됨

데이터 정의 종류

FLC I/O 보드 configuration 정보

Application Logic 수행을 제어하기 위한 정보

Application Logic 수행의 입출력 데이터

각 보드와 각 FPGA의 diagnostic 정보

통신으로 연결되는 외부 기기들에 대한 정보

통신을 제어하기 위한 정보

외부 기기들로 송신될 데이터

외부 기기들로부터 수신된 데이터

특별한 통신 프로토콜이 필요한 경우 통신(Com, Net) FPGA 코드 변경

http://www.wooriTG.com - 12 -

3-2. 데이터 구조

Configuration Data Block

FLC ID

IO 모듈 Type – slot 별로 종류 지정

IO 모듈 입력 데이터 base address

Input data block, output data block 개수

Application 개수

통신 Data base address

통신 Buffer 크기 및 개수

Diagnostic Status

Scan Time

통신 데이터 전송 주기

Sequence Number, Checksum

Control Data Block

Diagnostic Status

Input Data Block’s

Output Data Block’s

Block

Start Address

End Address

Contents Note

1 0x0000 0x00FF Configuration data Written from FApp

2 0x0100 0x01FF Control data Updated from FAdmin

3 0x0200 0x02FF InData block of

application #0 Updated from FAdmin

4 0x0300 0x03FF

5 0x0400 0x04FF OutData block of

application #0 Updated from FApp

6 0x0500 0x05FF

7 0x0600 0x06FF InData block of

application #1 Updated from FAdmin

8 0x0700 0x07FF

9 0x0800 0x08FF OutData block of

application #1 Updated from FApp

10 0x0900 0x09FF

11 0x0A00 0x0AFF ……….

13 ………. ……….

http://www.wooriTG.com - 13 -

3-3. 데이터 인터페이스

독립된 Application Logic

지원

Application Logic 별 데이

터 블록 설정

입력 데이터 블록

출력 데이터 블록

Safety 통신 블록

Non-safety 통신 블록

분리된 외부 인터페이스

COM Bus: IO Data,

Safety 통신 Data

Net Bus: Non-Safety

통신 Data

DI

AI

RX

DO

AO

TX

RAM Block

Application #1

MUX

MUX

FApp

Application Block #1

InData Block

OutData Block

TX

MUX(Non-

Safety)

RX

Com-

Bus

Net-

Bus

DI

AI

RX

DO

AO

TX

RAM Block

Application #N

MUX

Application Block #N

InData Block

OutData Block

TX

RX

InData Block

OutData Block

InData Block

OutData Block

http://www.wooriTG.com - 14 -

3-3. 데이터 인터페이스

FApp

D

I

A

I

R

x

1

N

R

x

N

D

I

A

I

R

x

1

N

R

x

N

Application Block #1

InData Blocks

R

x

1

N

R

x

N

FAdmin

FCom

FIn

D

I

A

I

Application Block #N

InData Blocks

FNet

입력 데이터 블록은 같은 값이 동시에 갱신됨

같은 포인트를 여러 Application Logic 에

서 사용 가능

출력 데이터 블록은 MUX에 의해 조합되어 갱신됨

Application Logic 별로 하나의 포인트 사용

http://www.wooriTG.com - 15 -

3-4. 특징

진단기능 강화

독립된 FPGA 들의 상호 감시

Parity, Checksum, Sequence

Number, Timeout 감시

FPGA 마다 전용 Watch Dog Timer 감시

내부 온도, 내부 전원 감시

출력 신호 피드백을 통한 출력 회로 건전

성 감시

테스트 입력 신호 자체 생성을 통한 입력

회로 건전성 감시

입력 Out-of-Range 검사

입출력 모듈의 Heart-bit 신호

채널별 파워 퓨즈 및 퓨즈 단선 감시

모듈 공유 버스의 어드레스, 데이터 Parity

통신 신호의 Parity, Checksum, Sequence

Number, Timeout 감시

Digital Input Data

One Scan Cycle

Analog Input Data

Receiving Data

Transfer Data to Application FPGA

Application FPGA Logic

Read Data from Application FPGA

Digital Output Data

Analog Output Data

Transmitting Data

Administration FPGA

Application FPGA

Digital Input

DIControl

Application FPGA

BusInterface

Ind

ication

Digital Output

DOControl

BusInterface

Ind

ication

Analog Input

AIControl

BusInterface

Analog Output

AOControl

BusInterface

Administration FPGA

Com FPGA Net FPGA

DIM DOM AIM AOM

LPM

Transmit / Receive Critical Data

Digital Input

Digital Output Analog Input

Analog Output

Read / Transfer

FPGA 동작 동기화

http://www.wooriTG.com

• Simpler, more effective safety/reliability justification

– Lower complexity levels and greater independence of functions

• No software component for the operation of the system

– Removal of S/W common mode failures

• Adequate capabilities for a wide range of applications

• Maintaining proven logic in an abstracted form

• Mitigation of impact of future obsolescence

– Easy to port to another FPGA

• Application as a diverse backup

• Fast execution time due to the parallel processing of logic algorithms

I&C 시스템에서의 FPGA

4. 결론

- 16 -

![〈鳥取・島根 便利な交通パス〉 3일간 교통 프리패스...[버스]* 고속 버스 * 이용가능한 초· 시 운영버스를 제외한 시,초,손이 운영하는](https://static.fdocument.pub/doc/165x107/5f42aaded4a1923876756ac7/ef-ef-3e-e-eoe-e.jpg)