第十一章 数模( D/A )转换与模数( A/D )转换

description

Transcript of 第十一章 数模( D/A )转换与模数( A/D )转换

第十一章 数模( D/A )转换与模数( A/D )转换

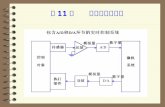

第一节 概 述一、实时控制系统的结构及组成

第二节 D/A 转换 一、数 / 模转换器的原理 ( 组成)

二、八位 D/A 转换器 DAC0832三、 12 位 D/A 转换器 DAC1210第三节 A/D 转换

一、逐次逼近式模 / 数( A/D )转换器原理

二、逐次逼近式 A/D 转换器基本组成

三、典型模 / 数转换器 ADC0809

习题: 11 - 4 , 11 -8

第一节 概 述

控

制

对

象

多路开关

MUX

采样保持器

S/H

I/O接

口

A/D转换器

传感器

传感器 放大滤波

放大滤波计

算

机执行部件

多路开关

MUX

I/O接

口

D/A转换器

包括 A/D 和 D/A 的实时控制系统

一、实时控制系统的结构及组成

1 . 传感器:把控制对象的各种参数的物理量用传感器测量 出来,并转换成电信号。

2 . 放大器:把传感器输出的信号 ( 一般为 mV 或 V) 放大到 A/D 转换所需的量程范围。

3 . 低通滤波器:抑制干扰,提高信躁比。4 . 多路开关:对传感器输出的多路信号进行切换,用一路装 置进行测量和控制。5. 采样保持电路:对模拟信号进行采样并保持以保证 A/D 转 换的正确性。

第二节 D/A 转换

一、数 / 模转换器的原理 ( 组成)

44

33

22

11

R

R4

R3

R2

R1

2d2d2d2dR

2V8R

Vd

4R

Vd

2R

Vd

R

Vd

44332211O IdIdIdIdI

。I1

I2 I3

If

d1 d2 d3 d4

R 2R 4R 8R

S1 S2 S4S3

Io Σ

-

+Vo

VR =5VI4

Rf = R/2

若 d1d2d3d4=1000

VR

RIoVo

5.2216

10

8

10

4

10

2

11

R

2VR

f

T 型电阻解码网络:

+

_D3 D2 D1 D0

VR R R R 2R

2R 2R 2R 2R

R

V0

I

I3 I2 I1 I0

I=I3D3+I2D2+I1D1+I0D0 VR=24R

(23D3+22D2+21D1+20D0)

二、 8 位 D/A 转换器 DAC0832

131415164567

8

12

11

9

3

20

10

IE

DI7DI6

DI5

DI4

DI3

DI2DI1

DI0

ILE

CS

WR1

WR2

XFER

19

1

18

2

17

VREF

IOUT2

IOUT1

RfbR1b

Vcc

DGND

8 位D/A

转换器

8 位DAC寄存器

8位输入寄存器

DAC0832 的内部结构图

AGND

IE

主要技术指标:

分辨率: 8 位

转换时间: 1 S

满量程误差: ±1LSB

参考电压: ±10V

单电源: +5V~+15V

1. 芯片介绍

2. 芯片的输出电路

0832-+

R数字量输入

i

VOUT

VOUT = - iR

0832-+

R

数字量输入

i

VOUT

R1 R2

VOUT = iR(1+R2 / R1)

0832-+

R1数字量输入

-+

R4

VOUT

VREF

R2

R3IOUT1

IOUT2

REFOUT VR

R

R

RiRV

3

4

2

41 )(

双极性输出

3. DAC0832 的三种工作方式

DAC0832

WR2WR1CSXFER

Vcc + 5V

D7-D0

Vo-+A

IOUT2IOUT1

AGND

DGNDVREFILE+ 5V

地址总线

DAC0832 与 8 位数据总线微机的连接图

地址译码

WRIO/M

②单缓冲方式:

ILE 接高电平;

CS 、 WR1 、 WR2 、XFER 接控制输出端(连接方式有多种形式);

当对 DAC0832 进行写操作时(执行 OUT 指令选中端口),数字量被转换成模拟量。

①直通方式: ILE 接高电平; CS 、 WR1 、 WR2 、 XFER 直接接地。 D/A 转换器的输出随着总线数据的变化而变化。

单缓冲方式的应用例 1 设 DAC 的口地址为 80H ,要求输出 0~4.98V 的周期性锯齿波

START : MOV AL , 0FFH

AGAIN : INC AL

OUT 80H , AL

CALL DELAY

JMP AGAIN阶梯的宽度由延时时间决定

例 2 要求 DAC 输出一三角波,波形下限电压为 0.5V ,上限电压为 2.5V 。

下限电压对应的数字量为:0.5*256/5=26=1AH

上限电压对应的数字量为:2.5*256/5=128=80H

BEGIN : MOV AL , 1AHUP : OUT 80H , AL INC AL CMP AL , 81H JNZ UP DEC ALDOWN : OUT 80H , AL DEC AL CMP AL , 19H JNZ DOWN JMP BEGIN

③ 双缓冲方式:

第一种应用情况:在前一个数据转换的同时, CPU将下一个数据先输入至输入寄存器,然后再在某个时刻启动 D/A 转换。

地址译码

320H

321H

DAC0832

Vcc + 5V

D7-D0

Vo-+A

IOUT2

IOUT1

AGND

DGNDVREF

ILE+ 5V

地址总线

DAC0832 与 8 位数据总线微机的连接图

WR1WR2IOWR

CS

XFER

MOV DX , 320H

MOV AL , DATA

OUT DX , AL

INC DX

OUT DX , AL

-+CS XFER WR2

ILE WR1

DAC1

-+ XFER WR2

ILE WR1

DAC2

-+CS XFER WR2

ILE WR1

DAC3

译码器AB

CS1

CS2

CS3

XFER

IO/M

WR

VO1

VO2

VO3

第二种应用情况:在多路 DAC 系统中,需要同步 D/A转换时,采用双缓冲方式。

在不同的时刻把要转换的数据分别打入各 DAC 的输入寄存器,然后由一个转换命令同时启动多个 DAC 转换。

DAC1210 的内部结构图

B1/B2

15161718192045

10

14

13

11

3

24

12

D11D10D9D8D7D6D5D4

CSWR1

WR2

XFER

23

1

212

22

VREF

IOUT2

IOUT1

RfbRfb

Vcc

DGND

12 位D/A

转换器

12 位DAC寄存器

8位输入寄存器

AGND4 位输入寄存器

D3D2D1D0

6789

LE LE

LE

三、 12 位 D/A 转换器 DAC1210

1. 芯片介绍主要技术指标:分辨率: 12位转换时间: 1 S满量程误差: ±1LSB参考电压范围: ±25V单电源范围: +5V~+15V

控制引脚 CS 、 B1/B2 、 WR1 作为输入寄存器的输入控制; WR2 、XFER 作为 DAC 寄存器的输入控制

2. DAC1210 与 8 位 CPU 接口方式

D7

D0

-+

Ri

VOUT

地址译码

D11

D0WR1

WR2

B1/B2

CSXFER

AB

IOW

A0

IOUT1

IOUT2

RFB

DAC

1210 控制 DAC1210 的转换共要用到 3 个 I/O 端口,CS 引脚的口地址为 220H-221H ,其中 220H 选通 8 位输入寄存器, 221H 选通 4 位输入寄存器; XFER 引脚的口地址为 222H-223H ,任一个地址都可启动 D/A 转换。若待转换的数字量在 BX 寄存器的低 12 位,则完成一次 D/A 转换的程序如下

START : MOV DX , 220H MOV CL , 4 SHL BX , CL MOV AL , BH OUT DX , AL

INC DXMOV AL , BLOUT DX , ALINC DXOUT DX , AL

第三节 A/D 转换

一、逐次逼近式模 / 数( A/D )转换器原理 实现 A/D 转换的方法有多种,而逐次逼近式 A/D转换具有速度快,分辨率高等优点获得了广泛的应用。这种 A/D 转换器的比较过程与天平的称重的过程相似。若一台天平具有 32 克、 16 克、 8 克、 4 克、 2 克和 1 克等6 种砝码,需要称量的物体重量为 27.4 克。称量从最重的砝码试起,过程如下表所示。次序 加砝码 天平指示 操作 记录

1 32 克 超重 去码 D5=0

2 16 克 欠重 留码 D4=1

3 8 克 欠重 留码 D3=1

4 4 克 超重 去码 D2=0

5 2 克 欠重 留码 D1=1

6 1 克 平衡 留码 D0=1

M=D5*32+D4*16+D3*8+D2*4+D1*2+D0*1=27 (克)

DAC

控制逻辑SAR

缓冲器

+

-

VR

ViCLK

输出数据

逐次逼近式 A/D 转换器原理框图

次序 试探码 D/A 输出 去留码 本次结果

1 1000 2.5V<Vi 留 1000

2 1100 3.75V>Vi 去 1000

3 1010 3.125V>Vi 去 1000

4 1001 2.8125V<Vi 留 1001

二、逐次逼近式 A/D 转换器基本组成控制逻辑 (SAR) :移位寄存器、数据寄存器、时序电路及去留码逻辑电路;DAC:产生电子砝码;比较器:对输入电压与电子砝码进行比较,并由控制逻辑决定该砝码的去留。 设转换器的位数 n=4 ,相应的电子砝码分别为2.5V 、 1.25V 、 0.625V 、 0.3125V 。Vi=3V, 则转换过程及结果如表所示。

三、典型 A/D 转换器 ADC0809

1. 芯片简介

8 路模拟开关

控制与时序

SAR

树状开关

电阻网络

三态输出锁存缓冲器地址

锁存与

译码

IN7

IN0

ADDAADDBADDC

ALE

Vcc GND VREF+ VREF- OE

D7

D0

EOC

CLKSTART

ADC0809功能方框图

主要技术指标

分辨率: 8 位

转换误差:

±1/2LSB~±1LSB

转换时间: 100 µS

时钟频率:

640KHZ

测量路数: 8 路

输出:三态缓冲

单一 5V供电,对应输入模拟电压范围 0~5V

2. ADC0809 工作时序START

ALE

通道地址

EOC

OE

DATA

64CLK

① 选择当前转换的通道,即将通道编码送地址锁存器;② 通过执行 OUT 指令在 START ,ALE 上产生一个正脉冲,锁存通道编码并启动 A/D ;

③A/D 转换开始后, EOC 变低,经过 64 个时钟周期后,转换结束, EOC 变高;④ 转换结束后,通过执行 IN 指令设法在 OE 脚上产生一个正脉冲,打开输出缓冲器的三态门读入转换数据。

⑴ 直接连接

MOV AL , 07H

OUT 84H , AL

CALL DELAY120

IN AL , 84H

若采用中断方式,可用 ADC0809 的 EOC 输出端作为 CPU 的中断申请信号,在中断服务程序中读入转换后的数据。

ADC0809 具有三态输出缓冲器,可以与 CPU直接连接。

若地址译码器的输出 Y1 的地址为 84H~87H ,则采用无条件传送方式从输入通道 IN7读入一个模拟量的程序为:

译码

8 分频

OE

ALESTARTADDCADDB

ADDA

D7~D0

EOC

CLOCK

A7~A0

D7~D0

CLK

Nc

IOR

IOW

Y1

VccVREF+

VREF-

GND

+5V

ADC0809 直接与微处理器的连接

ADC

0809

IN7

IN0

3. ADC0809 与微处理器的连接

⑵ 通过并行接口芯片同 CPU 连接

ADC 0809 通过 8255A 的接口原理图

译码Y1

Y0

IOWR

IORD

D7 ~ D0

A0

A1

A7 ~ A2

CLK

8088总线

8255A

PB4

PB2PB1PB0

PA

PC7

WR

RD

DB

A0

A1

CS

问题:用一片 8255A 并行接口芯片控制 ADC0809 的转换过程;分析: 8255A 有三个 8 位的并行口,可用 PB 口输出 0809 的通道选择编码和控制 ADC 的启动, PC 口输入 ADC 的状态。 PA 口作为他用,

实现:首先完成 CPU 与 8255 的连接,然后根据分析完成 ADC 与 8255 的连接

+5VCLOCK

ALESTARTADDCADDB

ADDA

EOC

OE

VccVREF+

VREF-

GND

ADC

0809

IN7

IN0

D7~D0

8 分频

Y0 地址为 80H~83HY1 地址为 84H~87H

例:对 ADC0809 的 IN0至 IN7巡回进行采样一次,并将采样的数据存放在以 DATA 开始的内存单元中。

第一步:程序初始化

MOV AL , 98H ; 8255 方式 0 , PA 口输入,OUT 83H , AL ; PB 口输出, PC 口高四位输入MOV SI , OFFSET DATA ;置内存首址MOV AX , 0H ;开关初始编码MOV CX , 8

第二步:输出通道号

启动 ADC

AGA : MOV AL , AH ;输出开关编码 OUT 81H , AL ADD AL , 10H ;启动 ADC OUT 81H , AL SUB AL , 10H OUT 81H , AL

第三步:判 ADC 转换结束否?结束则读入数据,存入内存。否则再判

LOP : IN AL , 82H ;检查 EOC TEST AL , 80H JZ LOP ; EOC=0 ,继续查询 IN AL , 84H ; EOC=1 ,读入数据 MOV [SI] , AL ;存入内存

第四步:修改循环变量

判测量完否?未完继续

INC SI ;修改指针INC AH ;修改开关编码LOOP AGA ;未完继续