基于 CFD 的离心压缩机整级性 能优化设计 · 而叶片扩 压器的进口角又是影响整个扩压器性能的重要 参数。为了继续优化扩压器叶片,本文对已优化

第七章 单片机系统扩展技术

description

Transcript of 第七章 单片机系统扩展技术

第七章 单片机系统扩展技术

§7-1 程序存储器的扩展 §7-2 数据存储器的护展

§7-3 MCS-51 并行 I/O 口的简单扩展

§7-4 可编程接口电路的扩展

前 言 单片机特点之一是在芯片内留有一定数量的数据存储器和程序

存储器,但容量有限。 MCS-51 系列的 CPU 芯片内部只有很少字节的数据存储器;程序存储器的数量很少,有的芯片中没有,不能满足实际控制的需要,在系统控制中必须扩展外部存储器。 外部存储器的扩展包括程序存储器和数据存储器,这两种扩展的实质都是根据单片机的结构特点和寻址能力,把不超过 64KB 的 RAM 和 ROM 存储器芯片按照一定规律连接到单片机的外部电路上去,作为单片机的片外存储器。

单片机外接程序存储器和数据存储器可以采用两种编址方法: 一种是程序存储器和数据存储器各自独立编址,两者最大编址空间均为 64KB ,但数据存储器的地址空间有一部分要被单片机扩展的外部设备( I/0 端口)所占用; 另一种是程序存储器和数据存储器及其它扩展的 I/O 器件统一编址,其总地址空间为 64KB 。 单片机访问外部存储器时,必须同时选通芯片和选中存储单元,才能占据不同存储空间的字节信息进行访问。通常采用两种方法获得芯片选择信号:线选法和通过译码器连接方法。

1 、线选法 线选法就是把 8031 的地址线直接或通过反相器连接到芯片的选通端( ),以 8031 送出的地址信号选通芯片,通常用单片机的低位地址线接至存储器芯片的地址输入端,而用余下的高位地址线接片选端。 线选法的连接方法有多种:一线二用、一线一选和综合线选方式。 在使用线选法时要注意以下的问题:

1 )地址浮动: 即在扩展芯片时,当芯片的地址线没有 16 位时,除片选信号线对电平

信号有要求外,其余的地址线应给于电平的固定,否则芯片的地址会发生变化(浮动),对存储器的访问会发生错误。

2 )地址的重叠 当不同的芯片在连接时由于共用地址线,它们的地址空间会有相同的情况下,此时,就发生地址重叠,对存储器的访问同样会发生错误。 为避免以上两种情况,在外部扩展时应注意:

1 )片选信号的地址线及其有效电平必须是唯一的; 2 )对未用的地址线,也不能输出任意的电平信号。

2 、地址译码器连接 通过地址译码器,使用较少的地址信号编码产生较多的译码信号,从而实现对多块存储器及 I/O 器件的选择。

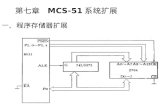

§7-1 程序存储器的扩展 返回 图 7-1 是 8031 扩展外部程序存储器的电路图,在通常情况下,扩展程序存储器常用 EPROM (光可擦除芯片)。在本例中选用的是 2764 。 单片机与外部存储器芯片的连接方式采用三总线的连接。

一、数据线的连接 (DB) 采用并连方式将各存储器芯片的数据线连接到 8031 的 P0 端口。

二、地址线的连接 (AB)

2764 地址信号来自单片机的 P0 口和 P2 口,低 8 位地址由 P0 口分时(地址 / 数据)送出。为了在访问存储器的整个周期内地址信号保持不变,必须将 P0 口先输出的低 8 位地址锁存起来(由锁存器 74LS373 来完成),在送数据信号时可以让出 P0 口,并且可以和由 P2 口送出的高

位地址一起实现对存储器内部存储器单元进行访问。

P0 口和 P2 口一起,最大能提供 16 位地址编码。存储器实际的地址线的数目由存储器芯片容量决定。由图 2764 所需地址线为 13 根,剩余的地址线可作为片选控制线使用中,如 P2.5 ,一起组成 2764 的地址编号。图中 2764 的地址代号为 0000H-3FFFH。(注意:本图中只有一块芯片扩展,没有进行高位地址线的处理,在实际系统中应注意与其它 I/O 设备及扩展芯片的地址处理)。

三、控制信号的连接 (CB)

存储器的控制信号线可以连接到 8031 相应的控制信号输出线上,如图中的 ALE 、 等,在程序存储器扩展时,特别注意芯片的 与 的连接。

扩展的联接过程如下图所示 :

图 7-1 程序存储器的扩展

§7-2 数据存储器的护展 返回 图 7-2 是 8031 扩展外部数据存储器的电路图,在通常情况下,扩展

数据存储器常用 RAM 芯片。在本例中选用的是 6116 。 和程序存储器一样,连接方式同样采用三总线的连接。 一、数据线的连接( DB )

采用并连方式将各存储器芯片的数据线连接到 8031 的 P0 端口。 二、地址线的连接( AB )

6116 地址信号来自单片机的 P0 口和 P2 口,低 8 位地址由 P0 口分时(地址 / 数据)送出,此时的片线信号为 P2.3 ,一起组成 6116 的地址编号。图中 6116 的地址代号为 0000H-0FFFH。(注意:本图中只有一块芯片扩展,没有进行高位地址线的处理,在实际系统中应注意与其它I/O 设备及扩展芯片的地址处理)。

三、控制信号的连接( CB) 存储器的控制信号线可以连接到 8031 相应的控制信号输出线上,如图中的 ALE等,在数据存储器扩展时,特点注意芯片的 、 与 的连接。

具体的联接图如图 7-2 所示:

图 7-2 数据存储器扩展图

§7-3 MCS-51 并行 I/O 口的简单扩展 返回 MCS-51 系列单片机有 4 个 8 位 I/O 口,共 32 根 I/O 线,但

并不是所有的 I/O 线都可以供用户使用,因为 P0 、 P2 、 P3口均有第二功能,在使用时不能仅作为 I/O传输口。除非且用 8051/8751 单片机且不作外部扩展。在实际应用系统中,常使用8031 芯片,此时 I/O 扩展技术成为系统控制能否实现的决定因素。

对于 8031 的 I/O 口注意其本身的特性(见第二章)。 I/O 扩展方法和单片机的 I/O 扩展性能有关。扩展的 I/O 口的寻

址方法与扩展的数据存储的寻址方式相同,即编址时与数据存储器统一编址,即 CPU视每个 I/O 口为外部数据存储器中的一个单元,只能用 MOVX 指令访问 I/O 口, I/O 口的读 /写操作分别受 信号控制。

应用系统扩展时常常需要有各种类型的简单 I/O 口,此时可能过 TTL芯片来扩展单元的简单的 I/O 口,数据的输入、输出须由单片机的读、写信号控制, I/O 口只能分时使用 P0 口。如果是输入口,则应根据输入数据的特点选择相应的芯片(要求接口电路具有三态缓冲或锁存选通功能);如作输出口,则要求接口电路具有锁存功能。 一、用三态口扩展 8 位并行输入口 当传送的数据的保持时间较长时,可用三态门扩展 8 们并行输入口。图 7-3 是用 74LS244 芯片通过 P0 口扩展的 8 位并行输入接口。 74LS244 是 8 位三态缓冲器,当 、 端为低平时输出与输入相同;当其为高电平时输出呈高阻态。

由图可知,当 P2.7 和 同时为低电平时 74LS244 才将由输入设备输出的数据送 8031 的 P0 口 .其中 P2.7决定了 74LS244 的地址 .它的地址 =0ⅹⅹⅹⅹⅹⅹⅹⅹⅹⅹⅹⅹⅹⅹⅹB,可取 7FFFH, 该接口的输入操作程序如下 :

MOV DPTR, #7FFFH ; 指向 74LS244 端口MOVX A, @DPTR ;输入数据

二、用锁存器扩展 8 位并行 I/O 口1 、扩展输入口 当传送的数据的保持时间较短时,不宜采用上述方法而应采用锁存器扩展 8 位并行输入口。图 7-4 是利用 74LS373 芯片通过 P0 口扩展 8 位并行输入接口。 74LS373 芯片的功能见表 7-1 ,利用中断方式进行数据传送。过程如下:

表 7-1 74LS373

2 、扩展输出口 当通过 P0 口扩展输出口时,要求接口电路具有锁存功能。为增加抗干扰能力,可采用带允许控制端的 8D锁存器。图 7-5 是用 74LS377 通过 P0 口扩展的 8 位并行输出接口,该芯片的功能见表 7-2 。由于 74LS377 的 G 端与 P2.6 相连 ,故地址为 0BFFFH 。用 8031 单片机的写脉冲信号作为该芯片的时钟,其输出操作程序如下:

MOV A , #DATA ;输出数据送 A MOV DPTR , #0BFFFH ; DPTR指向 74LS377 MOVX @DPTR , A ; P0 口经 74LS377 输出数据

出控制 使能 G 输入数据 D 输出数据Q

L H H H

L H L L

L L ҳ Q0

H ҳ ҳ Z

表 7-2 74LS377功能表

注: * 表示上升沿, ҳ 为任意状态, Q0 为建立稳态输入条件前的 Q的电平, Z为高阻态

输 入 输出CK D Q

H ҳ ҳ Q0

L * H H

L * L L

ҳ L ҳ Q0

其电路联接如图 7-5 所示:

§7-4 可编程接口电路的扩展 返回 当单片机应用系统中需要较为复杂的 I/O 口时不能采用§7-3 所介绍的方法扩展 I/O 口,通常采用可编程 I/O 接口芯片扩展 I/O 口。下面介绍两种常用标准可编程 I/O 接口及芯片扩展 I/O 口的方法。

一、可编程并行接口 8255A1 、 8255A 的基本性能

可编程外设接口电路( Programmable Peripheral Interface)简称PPI ,型号为 8255 (改进型为 8255A 及 8255A-5 ),具有 24条输入 / 输出引脚、可编程的通用并行输入 / 输出接口电路。

8255A具有三个相互独立的输入 / 输出通道: 通道 A 、通道 B 、通道 C 。 A , B , C 三通道可以联合使用,构成

单线、双线或三线联络信号的并行接口 ,此时 C 口完全服务于 A 、 B口。

A 口有三种工作方式:方式 0 、方式 1 、方式 2 。 B 口有两种工作方式:方式 0 、方式 1 。 2 、 8255A 内部结构 8255A 内部结构由以下四部分组成: 数据端口 A 、 B 、 C ; A组控制和 B组控制;读 /写控制逻辑电路;

数据总线缓冲器。结构如图 7-6 所示 端口 A :包括一个 8 位的数据输出锁存 /缓冲器和一个 8 位的数据输

入锁存器,可作为数据输入或输出端口, 并工作于三种方式中的任何一种。

端口 B : 包括一个 8 位的数据输出锁存 /缓冲器和一个 8 位的数据输入缓冲器,可作为数据输入或输出端口, 但不能工作于方式 2 。

端口 C : 包括一个 8 位的数据输出锁存 /缓冲器和一个 8 位的数据输入缓冲器, 可在方式字控制下分为两个 4 位的端口( C 端口上和下),每个 4 位端口都有 4 位的锁存器, 用来配合端口 A 与端口 B锁存输出控制信号和输入状态信号,不能工作于方式 1 或 2 。

A组和 B组控制的作用如下: A组控制逻辑控制端口 A 及端口 C 的上半部; B组控制逻辑控制端口 B 及端口 C 的下半部。

图 7-6 8255 结构图

2 、方式选择控制字及工作方式 方式选择控制字及各位的意义如图 7-7 所示。 1 )方式 0 是一种基本输入或输出方式,它适用于无需握手信号的简单输入输出应

用场合, 端口 A 、 B 、 C 都可作为输入或输出数据使用,输出有锁存而输入无锁存。

2 )方式 1 也称选通的输入 / 输出方式。在这种方式下,无论是输入还是输出

都通过应答关系实现, 这时端口 A 或 B 用作数据口,端口 C 的一部分引脚用作握手信号线与中断请求线。

若端口 A工作于方式 1,则 B 可工作于方式 0 ; 若端口 B工作于方式 1,则 A 可工作于方式 0 或余下的 13 位可工作于方

式 0 ; 若端口 A 和 B 同时工作于方式 1,端口 C 余下的两位还可用于传送数据

或控制信号。

3 )方式 2 也称选通的双向 I/O 方式,仅适用于端口 A , 这时 A 口的 P

A7-PA0 作为双向的数据总线,端口 C 有 5条引脚用作 A 的握手信号线和中断请求线,而 B 口和 C 口余下的 3 位仍可工作于方式 0 或 1 。它可以认为是方式 1 输出和输入的组合但有以下不同:

(1) 当 CPU 将数据写入 A 口时,尽管 OBF变为有效,但数据并不出现在 PA7-PA0 上,只有外设发出 ACKA 信号时,数据才进入 PA7-PA0 。

(2) 输出和输入引起的中断请求信号都通过同一引脚输出, CPU 必须通过查询 OBF和 IBF 状态才能确定是输入引起的中断请求还是输出引起的中断请求。

(3) ACKA 和 STBA 信号信号不能同时有效, 否则将出现数据传送“冲突”。

控制方式字及格式:

图 7-7 方式控制字及各位的意义

3 、 C 端口置 1置 0 控制字: 端口 C 的数位常常作为控制位来使用,所以,在设计 8255A 芯片时,

应使端口 C 中的各位可以用置 1置 0 控制字来单独设置。其具体格式如下图所示。

注意: C 端口置 1置 0 控制字尽管是对端口 C 进行操作,但此控制字必须写入控制口,而不是写入 C 端口。

4 、 MCS-51 和 8255A 的接口方法 如图所示为 MCS-51 和 8255A 的一种接口逻辑。 PA 口、 PB 口、 PC 口、控制口的地址分别为: 7FFCH、

7FFDH、 7FFEH、 7FFFH。

假设图中 8255A 的 PA 口接一组开关, PB 接一组指示灯, 如果,要将 MCS-51 的寄存器 R2 的内容送指示灯显示,将开关状态读入 MCS-51 的累加器 A ,则 8255初始化和输入 / 输出程序如下:

ORG 1000H R8255 : MOV DPTR , #7FFFH; MOV A , #98H MOVX @DPTR,A MOV DPTR,#7FFDH MOV A,R2 MOV @DPTR,A MOV DPTR,#7FFCH MOVX A,@DPTR RET

二、可编程接口芯片 8155

与 8255A 相比, 8155具有更强的功能,可以扩展单片机的 I/O 口、定时器、外部数据存储器 RAM 。

1 、 8155 芯片的构成 1 )逻辑结构 2 )引脚图 3 )接口信号 2 、 8155 的 RAM 和 I/O 口地址 RAM 地址 ---- 当 IO/ M 加低电平: 此时 AD0-AD7 上得到的地址值是指 8155 的某一 RAM 单元的地址,

地址范围是: 0000 0000--1111 1111 分别指向 8155 RAM 的 256 个存储单元。 I/O 口地址 ---- 当 IO/ M 加高电平: 此时 AD0-AD7 (仅用到低三位 AD2 、 AD1 、 AD0 )上得到的

地址值是指 8155 的某一 I/O 口的地址,具体端口地址分配是: 8155 的 RAM 和 I/O 口编址

8155 芯片的内部结构

256B静态RAM

A

定时器

B

C

口 A

PA0~PA7

口 B

PB0~PB7

PC0~PC5

口 C

IO/ M

AD0~AD7

CEALE

RDWR

RESET定时器输入定时器输出

接单片机

接外设

接外设

接外设

8155引脚功能

PC3PC4

PC5

IO/ MCERD

WRALEAD0AD1AD2AD3AD4AD5AD6AD7Vss

VccPC2PC1PC0PB7PB6PB5PB4PB3PB2PB1PB0PA7PA6PA5PA4PA3PA2PA1PA0

8155

TIMER INRESET

TIMER OUT

AD0-AD7

三态地址 /数据线

IO/ M 端口 / 存储器选择

RD 读

ALE地址锁存

允许

写 WR

选片 CE

定时器输入

TIMER IN

定时器输出

TIMER OUT

PA0-PA7

A 口端口线

PB0-PB7

B 口端口线

PC0-PC5

C 口端口线

地址编码

内部寄存器I/0 口地址

A7 A6 A5 A4 A3 A2 A1 A0

命令 /状态寄存器 X X X X X 0 0 0

PA 口寄存器 X X X X X 0 0 1

PB 口寄存器 X X X X X 0 1 0

PC 口寄存器 X X X X X 0 1 1

定时器低 8 位寄存器 X X X X X 1 0 0

定时器高 6 位和 2 位定时器方式寄存器

X X X X X 1 0 1

3 、 8155 的使用 1 ) 8155 内 RAM 的使用: 与一般外部数据存储器的使用基本一样,唯一区别是事先要

使 IO/ M 为低电平。 2 ) 8155 各端口的使用: A 、 B 、 C 各端口可工作于不同的工作方式,使用前要进行初始化(写命令字到命令口)

4 、扩展电路的连接实例 利用 8155 进行扩展时,方式常见的有如下 3 种,注意不同方

法的连线方式也各有特征: 1 )以高位地址直接作为 IO/M 信号扩展,接口电路非常简单,基本上是相同信号对接,如图 7-8 所示;

2 )多芯片扩展,如图 7-9所示; 3 )综合扩展,如图 7-10 所示。

1 )直接扩展法

图 7-8 8155 扩展实例

8031 8155

RESETRDWRALEP2.4

P0.0P0.1P0.2P.03P0.4P0.5P0.6P0.7

RESETRDWRALEIO/M

CE

AD0AD1AD2AD3AD4AD5AD6AD7

口 A

PA0~PA7

口 B

PB0~PB7

PC0~PC5

口 C

2 )多芯片扩展

图 7-9 多芯片扩展

8031

373

G2716

6116(2) 6116(1)

8155

P0

P2.2--P2.0PSEN

ALE

WRRD

ABCG2AG2BG1

P1.0

A0~A7 A8~A10

D7~D0 D7~D0 D7~D0CECE

CEOE

A0~A7 A8~A10

WE WEOE OE

WERD

ALE

AD0~AD7

CE

Y2

Y1

Y0

+5V

IO/ M

PA

PB

PC

P2.3P2.4P2.5P2.6P2.7

上图中的各扩展地址分别为: 8155 : 0000H 、 0001H 、……、 0005H 8031 的 P2.7-P2.3=00000 时,选中 8155 ,在此前提下,当

8031 的 P0 口输出地址是 XXXXX000-XXXXX101 ,且 IO/ M=1时,选中 8155 的各端口,即:

P2.7 ………………… P2.0 P0.7 ……… ………… P0.0 端口

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 ( 0000H) 命令口

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 ( 0001H) PA 口

0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 ( 0002H) PB 口

0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 ( 0003H) PC 口

0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 ( 0004H)计数器低

0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 ( 0005H)计数器高

当 IO/ M=0 时,选中 8155 的 RAM 单元,所以: 其内部 RAM 地址范围是: 0000H--00FFH 。 6116 ( 1 ): 0800H-0FFFH 6116 ( 2 ): 1000H-17FFH 分析: 根据 74LS138 , 8031 的 P2.7-P2.3=00001 时,选中 6116 ( 1 ),

在此前提下,加上 P2.2-P2.0 , P0.7-P0.0 低位地址,既有: 6116 ( 1 ) 的地址范围是: 0000 1 000 0000 0000-0000 1 111 1111 1111 即: 8000H-FFFFH。 6116 ( 2 ) 同理可得: 1000H-17FFH:

3 )综合扩展 线选法:

图 7-10 综合扩展

8031 6116CE

8255CS

8155IO/M CE

CE8253

CS0832

P2.3P2.4P2.0P2.5P2.6P2.7

线选法译码地址

外围器件 地址选择线( A15~A0 )

片内地址单元

数

地址编码

6116 1111 0AAA AAAA AAAA

2K F000~F7FFH

8255 1110 1111 1111 11AA

4 EFFC~EFFFH

8155 RAM 1101 111 0 AAAA AAAA

256 DE00~DEFFH

8155 I/O 1101 1111 1111 1AAA

6 DFF8~DFFDH

0832 1011 1111 1111 1111

1 BFFFH

8253 0111 1111 1111 11AA

4 7FFC~7FFFH

译码法

80316264CE

8255CS

8155IO/M CE

CE8253

CS0832

P2.5P2.6P2.7

P2.0

ABC

G2AG2B

G1

Y0Y1Y2Y3Y4

+5V

138

译码法的各芯片地址如下表所示。

外围器件 地址选择线( A15~A0 ) 片内地址单元数

地址编码

6264 000A AAAA AAAA AAAA 8K 0000~1FFFH

8255 0011 1111 1111 11AA 4 3FFC~3FFFH

8155 RAM

0101 111 0 AAAA AAAA 256 5E00~5EFFH

8155 I/O

0101 1111 1111 1AAA 6 5FF8~5FFDH

0832 0111 1111 1111 1111 1 7FFFH

8253 1001 1111 1111 11AA 4 9FFC~9FFFH

本章小结 1 、存储器扩展时的连接方式 2 、数据存储器、程序存储器扩展的方法 3 、常用 I/O 口的扩展 4 、可编程芯片 8255 、 6155 的结构及扩展方法 重点:系统功能扩展中的几种典型外围功能接口芯片

的结构、功能特性、工作原理、单片机与之连接后地址的确定及相应操作程序设定。

难点:单片机系统扩展的连接线路及地址确定。