630AmpT 型电缆接头 - gzbaye.com · 分接插头 15/2 kv k650rtp n ,7 8 9 缩径分接孔 15/2 kv k650rtw n ,7 8 9

基于可重构处理器的 图像并行插值缩放技术

description

Transcript of 基于可重构处理器的 图像并行插值缩放技术

基于可重构处理器的图像并行插值缩放技术

李钊2014.04.15

目录

面向可重构处理器的插值缩放算法的研究面向可重构处理器的插值缩放算法的研究

插值缩放算法的 RTL 级电路实现插值缩放算法的 RTL 级电路实现

对缩放后图像进行客观质量评价对缩放后图像进行客观质量评价

下一步工作计划下一步工作计划

面向可重构处理器的插值缩放算法的研究

图像缩放是通过插值算法重采样从而生成新的插值图像的过程。图像的算法根据是否利用图像边缘信息 , 可分为基于边缘的图像缩放算法:缩放后的图像视觉效果好 , 但其算法复杂 , 运算时间长 , 硬件电路难以实现 , 主要应用于医学领域。不基于边缘的图像缩放算法:最近邻域插值法 , 双线性插值法 , 双三次插值法 , B 样条插值法等。

最近邻域、双线性插值法:实现简单,效果不理想; 双三次插值法:较好的缩放效果,电路实现复杂 , 没有被广泛采用。

基于此 , 系统仍采用双三次插值算法 , 但提出了实现硬件电路的思路 , 避免三次方的计算 , 在没有显著增加硬件代价的同时 , 得到令人满意的图像缩放效果。

面向可重构处理器的插值缩放算法的研究

双三次插值算法: 在数值分析中 , 插值算法可用通式表示为

1

0k)x-h(x)(

n

kKCxg

其中, 为插值基函数, Ck 为第 K 个原函数的值。不同的插值算法只是基函数及选取的插值点个数 n 不同。

如果基函数的最高次幂为三次且在定义域内基函数的一阶 , 二阶导数连续 ,

则称该算法为三次插值算法 , 若在二维方向上应用该算法即双三次插值算法。

)x-h(x k

面向可重构处理器的插值缩放算法的研究

Hermite 双三次插值算法 :

如下图所示 x-1, x0, x1, x2 为等间隔的已知采样点 , x 为代求插值点 , 设 h=x1-

x0, s=(x-x0)/h ,则所求插值点的表达式为:

2

1k )s()f(x)(

k

�Sxf

面向可重构处理器的插值缩放算法的研究

Hermite 双三次插值算法 :

如下为三次插值基函数的拟合函数及表达式:

2||,0

2||1,||||5||84

1||,||||21

)( 2

22

s

ssss

sss

sS

面向可重构处理器的插值缩放算法的研究

Lagrange 双三次插值算法 :

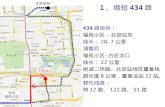

I. 本算法先进行水平方向的缩放: 水平计算时每计算一个插值点,需要水平位置上最邻近的连续四个源像素,

以及该插值点的水平插值位置。

如图所示,水平位置 x1、 x2、 x3、 x4 处是四个源像素。 x 表示插值点的位置,用 y 表示 x 处的像素值, y1、 y2、 y3、 y4 分别表示四个源像素值, position 代表 x与 x2 之间的距离,则水平插值计算的公式如下:

面向可重构处理器的插值缩放算法的研究

Lagrange 双三次插值算法 :

4)34)(24)(14(

)3)(2)(1(3

)43)(23)(13()4)(2)(1(

2)42)(32)(12(

)4)(3)(1(1

)41)(31)(21()4)(3)(2(

yxxxxxx

xxxxxxy

xxxxxxxxxxxx

yxxxxxx

xxxxxxy

xxxxxxxxxxxx

y

II. 竖直方向的缩放同理。

面向可重构处理器的插值缩放算法的研究

۞ Lagrange 双三次插值算法在可重构处理器上的映射

AXI/AHB

ARM11

USB Host Controller

Memory

DDR2/3 Controller

USB-PHY DDR-PHY

USB-DeviceDDR-

Memory

DMAC

RPU

IntCtrl

可重构处理器芯片

Carbon SoC Carbon SoC DesignerDesigner 中提供中提供

通过通过 Carbon Model Carbon Model StudionStudion将将 RTLRTL 转转化成化成 SystemCSystemC

9

面向可重构处理器的插值缩放算法的研究

۞ Lagrange 双三次插值算法在可重构处理器上的映射

RPU (RTL)

SoC Designer测试平台

算法分析手工配置结果

RPU 性能评估

手工配置工具

RPU (SystemC)

Carbon Model Studio

功耗面积估计

SoC 性能评估

Synopsys工具链

面向可重构处理器的插值缩放算法的研究

۞ 可重构处理器硬件架构

PE

PE PE PE

PE PE PE

PE PE PE

Dual-port shared

memory

PEA

ALU

配置包

数据源:SM/其他

PE/本PE的Registerfile

PE

ALU

配置包

面向可重构处理器的插值缩放算法的研究

۞ Lagrange 双三次插值算法在可重构处理器上的映射双三次插值算法分为两个 kernel

a. 行缩放:需要把源图像 ( 大小为 X*Y) 的每行 Y 列缩放为 N 列,一共计算 X 行数据,缩放后得到一个大小为 X*N 的图像 ;

b. 列缩放:需要把行缩放计算后的图像每列 X 行扩展为 M 行,一共计算 N 列,缩放后得到一个大小为 M*N 的图像。

一共要进行 N*(M+X) 次缩放计算。 每个插值点的缩放计算首先需要确定以这个插值点为中心的周围四个点在一行里

的位置,以及这个插值点与它周围四个点的距离,然后根据这个距离算得权重系数,权重系数分别与这四个点的像素值做乘法,最后求和算得插值点的像素值。每个插值点的缩放计算 DFG 如图所示。

面向可重构处理器的插值缩放算法的研究۞ Lagrange 双三次插值算法在可重构处理器上的映射for (i=0;i<x;i++){ i1=i+2;for(j=0;j<N;j++){ if (j==0)

{ x=0;j1=2;

}else { if(x+u>=0 && x+u<64)

{x=x+u;j1=j1;

}if ( x+u>=64 && x+u<128){

x=x+u-64; j1=j1+1;

}else if (x+u>=128 && x+u<192){

x=x+u-128;j1=j1+2;

}else if (x+u>=192 && x+u<256){

x=x+u-192; j1=j1+3;

}else if (x+u>=256 && x+u<320){

x=x+u-256; j1=j1+4;

}else if (x+u>=320 && x+u<384){

x=x+u-320; j1=j1+5;

}else if (x+u>=384 && x+u<448){

x=x+u-384; j1=j1+6;

}

else { x=x+u-448; j1=j1+7;

} A[0]=x*(64-x)*(128-x)/6; A[1]=(64+x)*(64-x)*(128-x)/2; A[2]=(64+x)*x*(128-x)/2; A[3]=(64+x)*(64-x)*x/6;

B[0]=image[i1][j1-1]; B[1]=image[i1][j1]; B[2]=image[i1][j1+1]; B[3]=image[i1][j1+2];

d1=A[1]*B[1]+A[2]*B[2]-(A[3]*B[3]+A[0]*B[0]); d2=d1/262144;

image_out[i][j]=d2;

}}

面向可重构处理器的插值缩放算法的研究

-

i64

?:

-

i128

?:

-

i192

?:

-

?:

-

?:

-

?:

-

?:

+

i255 i1

+

i255 i65

+

i255 i129

+

i255 i193

-

i 64

+i 0

m2-0

+i 64

+

-i 6

i 1r2

?:

-2

RF[15]

1

r2

× ×>

i 1

-i 128

r1

×

PE1 PE2 PE3 PE4 PE5 PE6 PE7

r1

r1

×× × ×

+

r2 i 0

+ + + +

?: ?: ?: ?:-2

RF[15]

1 -2

RF[15]

1 -2

RF[15]

1 -2

RF[15]

1

+ + + +

r1 i 0 r1 i 0 r1 i 0 r1 i 0

i 0

r1

i 0

r1

i 0

r1

i 0

r1

×× × ×

+ + + +i 0 i 0 i 0 i 0

r3 r3 r3 r3

r1 r1 r1 r1

?:

i 1

+?:

|

i0

?:i0

?:

i 0

PE8

m2-0

m2-1

PE9

?:

i 2

+?:

PE10

?:

i 3

+?:

PE11

?:

?:

i 6

+ ?:

?:

i 5

+ ?:

?:

i 4

+ ?:

PE14 PE15PE13

i 7

+

PE12

+

m2-0 i 32

m2-0

m2-0 m2-0 m2-0 m2-0 m2-0 m2-0 m2-0

m2-0

m2-2

m2-1

m2-1 m2-1

m2-1 m2-1

m2-1

m2-1 m2-1

-

i0

-

i1

-

i2

-

m2-1 m2-1 m2-1 m2-1 i3

r3 r3 r3 r3

× ×

-

>

18

m3-0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

面向可重构处理器的插值缩放算法的研究

۞ 每个插值点的缩放计算映射图:

目录

面向可重构处理器的插值缩放算法的研究面向可重构处理器的插值缩放算法的研究

插值缩放算法的 RTL 级电路实现插值缩放算法的 RTL 级电路实现

对缩放后图像进行客观质量评价对缩放后图像进行客观质量评价

下一步工作计划下一步工作计划

插值缩放算法的 RTL 级电路实现

۞ 视觉信息处理系统总体架构:

PLB

Memory

Linebuffer

Linebuffer

Medianfilter

Medianfilter

YUVto

RGB

CIS

CIS

AddrGen

MPMC

DDR

AddrGen

RPU

PEA

PLBto

SCCB

PLB

Microblaze

DPLB

DXCL

XCL

PIM1

PIM0

Interface

YUYVto

YUV

PIM2

Pre-Processing Subsystem

Interface

IXCL

XCL

IPLB

DMA

MCU

Linebuffer

Line Scale

ImageEnhance

Post-Processing Subsystem

mpmc

DDR

colume Scale

Display TimingControl

Linebuffer

AddrGen

Controlmaster

AddrGen

PIM0

PIM1

Interface

OSD

插值缩放算法的 RTL 级电路实现

۞ 缩放模块架构图:

参数配置模块

缩放模块

buffer_1_control line_scale buffer_2_control colume_scale

dual_port RAM dual_port RAM

后处理子系统

DDRcontroller

插值缩放算法的 RTL 级电路实现

۞ line_scale和 colume_scale模块流程图

插值缩放算法的 RTL 级电路实现

۞ buffer_1_control 模块:

CLK buffer_1_contol

Dataposition计算

地址控制

position

Data_out

addr

from

_ram

to_r

am

目录

面向可重构处理器的插值缩放算法的研究面向可重构处理器的插值缩放算法的研究

插值缩放算法的 RTL 级电路实现插值缩放算法的 RTL 级电路实现

对缩放后图像进行客观质量评价对缩放后图像进行客观质量评价

下一步工作计划下一步工作计划

对缩放后图像进行客观质量评价۞ 对于 Herimite 插值缩放和 lagrange 插值缩放后的图像,哪个效果更好? 传统的图像质量评价方法是通过计算失真图像与原始图像像素点之间纯数学的误差来衡量失真程度,例

如,均方误差和峰值信噪比。但是,这两种方法没有利用图像任何的位置信息和像素之间的相关性,与人类视觉系统感知图像的方式不符。

2012年,同济大学对已有的 11 种算法进行了综合评价。

NQM和 VSNR 是两个基于HVS的 IQA 方法

UQI->SSIM->MS-SSIM->IW-SSIM

IFC->VIF(基于信息保真度准则)

RFSIM->FSIM( 基于底层视觉特性相似 )

对缩放后图像进行客观质量评价

2002年, Zhou Wang, Bovik AC 提出 UQI 方法,把所有失真情况认为是以下三种因素的组合 :

相关性失真(相关系数);亮度失真(亮度的近似程度);对比度失真(对比度的近似程度)。

2222

x 2

)()(

2

yx

yx

yx

y

yx

yxQ

UQI 采用 8*8窗口,求窗口 64 个点的期望,由期望求得方差,可组成以上三个元素。缺点:块效应比较明显。

对缩放后图像进行客观质量评价

2004年, Zhou Wang 提出 SSIM 算法,为了去除块效应,采用 11*11 的高斯低通滤波窗口。

对缩放后图像进行客观质量评价

SSIM 是一个单一尺度方法,这是一个缺陷,尺度应该随着观测条件(例如,显示分辨率和观测距离)的变化而变化。并且,图像在单一尺度下不容易看出或获取,但是在另外的尺度下很容易看出来或者检测到 , 所以利用多尺度分析技术可以更有效的提取图像特征 ,获取图像内容。 2003年, Zhou Wang 提出 MS-SSIM ,对图像进行高斯塔形分解,从此进入多分辨率分析。 多分辨率分析以小波作为分析基础 , 是一种由粗及精的对信号进行逐级分析的过程 , 实现多种分辨率的信号可以发现单一分辨率下无法发现的特性。

对缩放后图像进行客观质量评价

自从基于结构相似度( SSIM)模型提出来以后,有许多研究者对齐进行了改进。几乎所有的方法都分为三步:1.使用多分辨率方法,分解为大小不同的尺度;2.对不同尺度图像计算 SSIM 值;3.对不同尺度图像给予不同权重值。 2011年, Zhou Wang 等提出 IW-SSIM 算法:①首先使用拉普拉斯塔形分解,分成为 5 个大小不同的尺度;②对于每个尺度的矩阵使用 11*11 的高斯低通滤波窗口计算 SSIM 值;③采用高斯尺度混合模型( GSM)模拟自然图像多分辨率系数的分布统计特性,估算局部信息量,用于最终图像差异的加权综合。 拉普拉斯金字塔通过求解原图像与高斯滤波后上采样得到的图像的残差来提取图像的边缘细节信息 , 可是得到的高频信息不能保持图像的平移和旋转不变性

对缩放后图像进行客观质量评价

۞ 小论文创新点介绍: 圆周对称的多分辨率分析方法与以上的多分辨率分析方法相似 , 通过一系列滤波

器组将图像分解为多个不同分辨率的细节子带和一个低频子带 , 不同的是 , 它采用的滤波器组具有圆周对称特性。

۞ 优点 基函数比较光滑 ,正则性好 , 可以消除频率混迭的现象; 它的频谱具有带通性,圆对称性 ,频域局部特性好 ,冗余度低 , 是一种新的低冗余

度的多分辨率分析方法。۞ 实现方法 与经典的多分辨率分解相比 , 为保证圆周对称多分辨率分解的平移不变性 ,使对低

通滤波后的信号进行隔行隔列的下抽样不产生频谱混迭现象 , 用二维圆对称滤波器组来实现。

下一步工作计划

۞ 插值算法在可重构处理器上的仿真。۞ 插值缩放算法的 RTL 级实现。۞ 图像质量评价方法。

谢 谢谢 谢 !!