微 机 存 储 器系统

-

Upload

caryn-acosta -

Category

Documents

-

view

40 -

download

10

description

Transcript of 微 机 存 储 器系统

6.1 6.1 概述概述

6.1.16.1.1 存储系统的层次结构存储系统的层次结构

6.1.26.1.2 存储器的分类存储器的分类

6.1.36.1.3 存储器的基本组成存储器的基本组成

6.1.46.1.4 存储器的技术指标存储器的技术指标

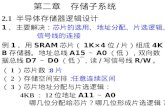

6.2 6.2 半导体读写存储器 半导体读写存储器

6.2.16.2.1 静态静态 RAMRAM

6.2.26.2.2 动态动态 RAMRAM

6.2.36.2.3 存储器的工作时序存储器的工作时序

6.3 6.3 半导体只读存储器半导体只读存储器

6.3.1 6.3.1 掩膜式只读存储器掩膜式只读存储器 ROMROM

6.3.2 6.3.2 可编程的只读存储器可编程的只读存储器

6.3.3 6.3.3 可编程可擦除只读存储器可编程可擦除只读存储器

6.4 6.4 存储器与存储器与 CPUCPU 的连接的连接

6.4.1 6.4.1 存储器与存储器与 CPUCPU 连接时问连接时问题题

6.4.2 6.4.2 常用译码电路常用译码电路

6.4.3 6.4.3 存储器连接举例存储器连接举例

微 机 存 储 器系统微 机 存 储 器系统第 第 6 6 章章

66 .. 11 .. 1 1 存储系统的层次结存储系统的层次结构构

概述概述

11 .主存储器—外存储器.主存储器—外存储器

22 .主存储器—高速缓冲存储.主存储器—高速缓冲存储器器33 .虚拟存储技术.虚拟存储技术

CPUCPU

高速缓冲存储器高速缓冲存储器

主存储器主存储器

外存储器外存储器

图图 6-1 6-1 存储器系统的层次结构图存储器系统的层次结构图

66 .. 11

存储器的分类存储器的分类

按存取方式分类按存取方式分类

按存储器载体分类按存储器载体分类

随机存储器(随机存储器( RAMRAM ))

只读存储器(只读存储器( ROMROM ))

顺序存储器(顺序存储器( SAMSAM )

磁介质存储器磁介质存储器

半导体存储器半导体存储器

光存储器光存储器

存储器

存储器

66 .. 11 .. 22

存储器的基本组成存储器的基本组成

XX地址地址译码译码

器器

存储单元矩阵存储单元矩阵 NXMNXM (( 4096XI4096XI ))

YY 地址译码器地址译码器

26

A11 A6

2266

A11A11

A6

n 个

输入输入缓冲器缓冲器

数据输入数据输入DINDIN 写入 读出写入 读出 输入输入

缓冲器缓冲器

数据输出数据输出DOUTDOUT

R/WR/W 读写输读写输入入CSCS 片选择片选择

图图 6-2 6-2 典型存储器的组成框图典型存储器的组成框图

6.1.36.1.3

存储器的技术指标存储器的技术指标

衡量存储器的技术指标衡量存储器的技术指标

存储器容量

存取周期

存取周期

可靠性

可靠性

经济性

经济性

取数时间

取数时间

66 .. 11 .. 44

66 .. 22 .. 1 1 静态静态 RARAMM

半导体读写存储器半导体读写存储器

11 .静态.静态 RAMRAM 的工作原的工作原理理

选择线选择线

VF5VF5

I/OI/O

A B

VF1VF1 VF2VF2

VF4VF4

VF6VF6

VccVcc

I/OI/O图图 6-3 6-3 六静态六静态 RAMRAM 基本存储电基本存储电路路

66 .. 22

22 .静态.静态 RAMRAM 组成组成

将多个存储单元按一定方式将多个存储单元按一定方式排列起来,就组成了一个静排列起来,就组成了一个静态态 RAMRAM 存储器存储器 [[ 见书见书 P17P178]8]

33 .静态.静态 RAMRAM 举例举例

现在以一个具体的芯片——现在以一个具体的芯片—— IIntel 2114ntel 2114 为例,来说明静态为例,来说明静态RAMRAM 的具体组成。的具体组成。 [[ 见书见书 P1P179]79]

静态静态 RAMRAM66 .. 22 ..11

VF5VF5

I/OI/O

AA BB

VF1VF1 VF2VF2

VF6VF6

图图 6-6-6 6 四管动态四管动态 RAMRAM 基本存储电路基本存储电路

C1C1 C2C2

VF7VF7

EDED

VF8VF8

EDED

选择线选择线

EsEs

66 .. 22 .. 2 2 动态动态 RRAMAM动态动态 RAMRAM 的工作原理的工作原理

存储器的工作时序

11 .存储器的读周期.存储器的读周期

存储器的读周期,就是从存储器读出数据所需时间存储器的读周期,就是从存储器读出数据所需时间

22 .存储器的写周期.存储器的写周期

是地址建立、写脉冲宽度和写操作恢复时间三者的总和是地址建立、写脉冲宽度和写操作恢复时间三者的总和 。

33 . . 8086CPU8086CPU 对存储器的读对存储器的读 // 写时写时序序

读周期时读周期时序序

写周期时序写周期时序

6 . 2 . 3

掩膜式掩膜式 ROMROM 有双极型和有双极型和 MOSMOS 型两种类型型两种类型

66 .. 33 .. 1 1 掩膜式只读存储器掩膜式只读存储器ROMROM

半导体只读存储器半导体只读存储器

速度快 容量小速度快 容量小 容量大速度较容量大速度较慢慢

66 .. 33 .. 2 2 可编程的只读存储器可编程的只读存储器 PRPROMOM

●● ROMROM 在制作时不写入信息,用户使用时可写入自己的程在制作时不写入信息,用户使用时可写入自己的程序。但这种写入是一次性的,一旦写入内容后就不能更改,序。但这种写入是一次性的,一旦写入内容后就不能更改,所以称一次性可编程序只读存储器,又称为现场可编程序只所以称一次性可编程序只读存储器,又称为现场可编程序只读存储器。读存储器。

66 ..33

可编程、可擦除的只读存储器——可编程、可擦除的只读存储器—— EPROEPROMM

11 .紫外线擦除的.紫外线擦除的 EPROMEPROM

这种这种 EPROMEPROM 是采用紫外线擦去原存内容,再用专是采用紫外线擦去原存内容,再用专门写入器改写内容。因此又称门写入器改写内容。因此又称 UVEPROMUVEPROM 。。

22 .电可改写的、可重编程的只读存储器.电可改写的、可重编程的只读存储器

这种电可改写这种电可改写 PROMPROM ,简称为,简称为 EEPROMEEPROM 。。

33 .. EPROMEPROM 芯片举例——芯片举例—— Intel 271Intel 27166

Intel 2716Intel 2716 是是 16K16K 位,可组成容量为位,可组成容量为 2K×82K×8 的紫外的紫外线擦除的线擦除的 EPROMEPROM 。。

66 .. 33 .. 33

66 .. 44 ..11

11 .. CPUCPU 总线的负载能力总线的负载能力

●● 一般情况下,一般情况下, CPUCPU 总线的直流负载能力可带动一个标总线的直流负载能力可带动一个标准的准的 TTLTTL 门。门。

22 .. CPUCPU 的时序与存储器的存取速度之间的配的时序与存储器的存取速度之间的配合合

●● CPUCPU 在取指令和进行读出操作时,都是在相应的时序在取指令和进行读出操作时,都是在相应的时序控制下进行的,如读周期和写周期, 已根据时钟频率和控制下进行的,如读周期和写周期, 已根据时钟频率和机器运算速度确定好范围。那么,在选用存储器时,它机器运算速度确定好范围。那么,在选用存储器时,它的最大存取时间要小于的最大存取时间要小于 CPUCPU 安排的读写周期。 否则,要安排的读写周期。 否则,要使使 CPUCPU 插入等待周期, 才能保证读写数据的可靠传送。插入等待周期, 才能保证读写数据的可靠传送。

66 .. 4 4 存储器与存储器与 CPUCPU 的连的连接接 存储器与存储器与 CPUCPU 连接时要考虑的问连接时要考虑的问

题题

33 ..

●● CPUCPU 的信号电平多为的信号电平多为 TTLTTL 标准电平。当选用的存储标准电平。当选用的存储器电平不相匹配时,它不能与器电平不相匹配时,它不能与 CPUCPU 直接相连,必须经直接相连,必须经缓冲器进行电平转换。缓冲器进行电平转换。

44 .存储器的地址要合理分配.存储器的地址要合理分配

●● 通常在微型机的主存中有通常在微型机的主存中有 RAMRAM 和和 ROMROM (( EPROEPROMM )两部分。)两部分。

55.控制信号的连接.控制信号的连接

●● CPUCPU 到存储器的控制信号,一般包括读写控制信号、到存储器的控制信号,一般包括读写控制信号、片选信号、复位信号、刷新信号(对动态片选信号、复位信号、刷新信号(对动态 RAMRAM )等,)等,在常规情况下存储器可直接连接这些控制信号。在常规情况下存储器可直接连接这些控制信号。

存储器的电平信号与存储器的电平信号与 CPUCPU 的电平匹配的电平匹配

常用的译码电路常用的译码电路66 .. 44 ..22

●● 由于在存储器与由于在存储器与 CPUCPU 连接时,不仅仅要考虑地址、数据和连接时,不仅仅要考虑地址、数据和控制总线的连接,还要考虑实现这三种信息传送的有关电路,控制总线的连接,还要考虑实现这三种信息传送的有关电路,如地址译码器与锁存器、数据缓冲、控制信号的传递与加工等如地址译码器与锁存器、数据缓冲、控制信号的传递与加工等因素,而这些因素中最重要的便是地址译码器。因素,而这些因素中最重要的便是地址译码器。

行地址和列地址的形成行地址和列地址的形成

●● 该存储系统的容量为该存储系统的容量为 64K×864K×8 位的位的 RAMRAM ,其,其 RAMRAM 芯片芯片的行地址和列地址形成电路如图的行地址和列地址形成电路如图 6-20 [P192]6-20 [P192] 所示。所示。

●● PC/XTPC/XT 机中机中 RAMRAM 子系统采用子系统采用 41644164 动态动态 RAMRAM 芯片,芯片,有四组芯片,每组九片,其中八片构成有四组芯片,每组九片,其中八片构成 64KB64KB 容量的存储容量的存储器,一片用于奇偶校验位,四组动态器,一片用于奇偶校验位,四组动态 RAMRAM 芯片构成芯片构成 XTXT机系统板上机系统板上 256KB256KB 容量的内存。 送到每个组中的行、列容量的内存。 送到每个组中的行、列地址由两片地址由两片 74LS15874LS158 (二选一选择器)组成的地址多路(二选一选择器)组成的地址多路器提供。器提供。

1 .

RASRAS 和和 CASCAS 的产生的产生

PC/XTPC/XT 机和机和 CASCAS 信号产生四组动态信号产生四组动态 RAMRAM 存储器的存储器的 RASRAS00~~ RAS3RAS3 和和 CAS0CAS0~~ CAS3CAS3 。由两级地址译码器组成。。由两级地址译码器组成。第二级译码器由两片第二级译码器由两片 74LS13874LS138 组成组成 ,U56,U56产生行地址选通产生行地址选通信号信号 RAS0RAS0~~ RAS3RAS3;; U42U42产生列地址选通信号产生列地址选通信号 CASCAS00~~ CAS3CAS3 。。

第二级译码器工作需满足以下三个条件第二级译码器工作需满足以下三个条件:

(1)(1)第一级第一级译码器输译码器输出出 Q0=Q0=“H”“H”

(2)(2) 非刷新非刷新操作,操作, DCDCK0BRD=K0BRD=“H”“H”

(3)(3)有存有存储器读或储器读或写信号写信号 XXMEMRMEMR 、、XMEMWXMEMW

22 ..

存储器存储器

RAS RAS CASCAS

刷新电路刷新电路

地址地址多路器多路器

DMACDMAC

定时器定时器

延时线延时线

&&22

&&33

&&

地址总线地址总线A8~A15A8~A15

A0~A7A0~A7

A0~A6A0~A6

RASRAS80ms80ms

100ms100ms

DACK0DACK0

DREQ0DREQ0

总线请求总线请求HOLDHOLD

HLAD

总线响应总线响应

存储器读写线存储器读写线

REFREF

图图 6-22 6-22 刷新逻辑的原理刷新逻辑的原理

33 ..

小结小结

6.1 6.1 概述概述

6.1.16.1.1 存储系统的层次结存储系统的层次结构构

6.1.26.1.2 存储器的分类存储器的分类

6.1.36.1.3 存储器的基本组成存储器的基本组成

6.1.46.1.4 存储器的技术指标存储器的技术指标

6.2 6.2 半导体读写存储器半导体读写存储器

6.2.16.2.1 静态静态 RAMRAM

6.2.26.2.2 动态动态 RAMRAM

6.2.36.2.3 存储器的工作时序存储器的工作时序

6.3 6.3 半导体只读存储器半导体只读存储器

6.3.1 6.3.1 掩膜式只读存储器掩膜式只读存储器 ROMROM

6.3.2 6.3.2 可编程的只读存储器可编程的只读存储器

6.3.3 6.3.3 可编程可擦除只读存储器可编程可擦除只读存储器

6.4 6.4 存储器与存储器与 CPUCPU 的连接的连接

6.4.1 6.4.1 存储器与存储器与 CPUCPU 连接时问题连接时问题

6.4.2 6.4.2 常用译码电路常用译码电路

6.4.3 6.4.3 存储器连接举例存储器连接举例