第四章 组合逻辑电路

Click here to load reader

-

Upload

ulysses-watkins -

Category

Documents

-

view

378 -

download

15

description

Transcript of 第四章 组合逻辑电路

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

第四章 组合逻辑电路4.1 概述4.2 分析方法和设计方法4.3 常用的组合逻辑电路4.4 竞争 - 冒险现象

习 题

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

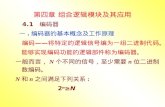

4.1 概述

一、组合逻辑电路的特点

数字电路按逻辑功的特点

可分为两大类 :

1. 组合逻辑电路 ( 时间无关 )

2. 时序逻辑电路 ( 时间相关 )

在组合逻辑电路在任意时刻的输出和状态只取决于该时刻的输入 (而与电路原来的状态无关 )。

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

二、本章重点:

1.组合逻辑电路的分析方法;

2.组合逻辑电路的设计方法;

3.常用组合电路的功能和使用方法 (读懂功能表 )。

对于具体逻辑电路结构了解一下就可以了。

常用组合电路包括:

1. 编码器

2. 译码器

3. 数据选择器

4. 加法器

5. 数值比较器

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

三、组合逻辑功能的描述

逻辑图、函数式或真值表均能描述,这里用函数式说明:

( )Y F A

1 1 1 2

2 2 1 2

1 2

, ,......,

, ,......,

......

, ,......, )

n

n

m m n

y f (a a a )

y f (a a a )

y f (a a a输出方程

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

4.2 组合电路的分析方法和设计方法4.2.1 组合电路的分析方法

逻辑图 函数式 真值表(功能表)转换,化简,计算

如果可能文字描述逻辑功能

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

A B CI S CO

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

S = A B C

CO = A B + A B CI

全加器

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

组合逻辑电路分析习题1.写出图示电路中 Y的逻辑式; 2 .填写功能表(真值表);

&

&

R

VCC

Y

S0S1

AB

A

S1 S0 Y

0 0

1

0

1

0

1

1

功能表

1

A’+B’

A +B’

B’

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

4.2.2 设计方法

函数表达式,并化简 (有时不需要化简 );

根据实现电路的要求不同,对表达式进行相应的转换;

画逻辑图。

逻辑抽象1. 确定输入输出变量,用字母表示之;2. 状态赋值 ( 逻辑赋值 ) ;3. 总结出真值表;

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

例 4.2.2 交通信号灯故障检测电路。要求在非“只有一只灯亮”时给出故障信号。

解:

首先逻辑抽象。 R 代表红、 A 代表黄、 G 代表绿 ; 用‘ 1’ 表示灯亮,“ 0” 表示灯灭;用 Z 表示输出,且“ 1” 表示有故障。

1. 真值表 ( 逻辑抽象 )

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

得到真值表: R A G Z

0 0 0 1

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

2. 函数式注意:在用门电路实现时要注意点:第一、要把函数式划成最简。第二、把函数式转化为所用门要求的形式。

1 1

0

10

1101 00R

1 1

11

AG

得到最简与或式:

Z = ((R'A'G')'(RA)'(RG)'(GA)')'若用与非门:

Z = R'A'G' + RA + RG + AG

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

3. 逻辑图电路图

(( ' ' ') '( ) '( ) '( ) ') 'Z = R A G RA RG GA

AGRGRAGARZ '''

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

P210 [ 题 4.6] 组合电路的设计(约束条件的组合逻辑电路设计)

缓冲隔离的作用!必须存在

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

4.3 若干常用的组合逻辑电路4.3.1 编码器( Encoder)

编码:用二值代码表示对象

一、普通二进制编码器

1. 功能表 / 真值表输 入 输 出

I0 I1 I2 I3 I4 I5 I6 I7 Y2 Y1 Y0

1 0 0 0 0 0 0 0 0 0 0

0 1 0 0 0 0 0 0 0 0 1

0 0 1 0 0 0 0 0 0 1 0

0 0 0 1 0 0 0 0 0 1 1

0 0 0 0 1 0 0 0 1 0 0

0 0 0 0 0 1 0 0 1 0 1

0 0 0 0 0 0 1 0 1 1 0

0 0 0 0 0 0 0 1 1 1 1

功 能 表( Function Table )

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

2. 函数式

3. 逻辑图

75310

76321

76542

IIIIY

IIIIY

IIIIY

特点:普通编码器为“或”逻辑矩阵。

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

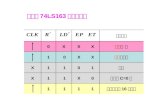

二、优先编码器 1. 8-3 线优先编码器 74148

输 入 输 出

1 X X X X X X X X 1 1 1 1 1

0 1 1 1 1 1 1 1 1 1 1 1 0 1

0 X X X X X X X 0 0 0 0 1 0

0 X X X X X X 0 1 0 0 1 1 0

0 X X X X X 0 1 1 0 1 0 1 0

0 X X X X 0 1 1 1 0 1 1 1 0

0 X X X 0 1 1 1 1 1 0 0 1 0

0 X X 0 1 1 1 1 1 1 0 1 1 0

0 X 0 1 1 1 1 1 1 1 1 0 1 0

0 0 1 1 1 1 1 1 1 1 1 1 1 0

' ' ' ' ' ' ' '0 1 2 3 4 5 6 7S' I I I I I I I I ' ' '

2 1 0Y Y Y ' 'S EXY Y

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

S’ 是“使能”信号

低电平有效

G1 门是负逻辑输入非门

EX S

S 0 1 2 3 4 5 6 7

Y ' = (Y 'S)'

Y ' = (I 'I 'I 'I 'I 'I 'I 'I 'S)'

Y’S Y’EX 工 作 状 态1 1 不工作,使能端无效0 1 工作,但无输入1 0 工作,且有输入0 0 不可能出现

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

正、负逻辑输入门的对应关系

负逻辑输入门和负逻辑门有区别,见备注

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

例 4.3.1 编码器逻辑功能的扩展 : 用两片 74148 接成 16 线 -4 线优先编码器

原理

Y’S Y’EX 工 作 状 态

1 1 不工作, Y=1

0 1 工作,但无输入, Y=1

1 0 工作,且有输入

Z3 Z2 Z1 Z0

(1)1 000 ~ 1 111(2)0 000 ~ 0 111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

2. 二—十进制优先编码器 74147

为什么没有 I0′?

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

4.3.2 译码器 (Decoder)

一、二进制译码器

译码:将输入的二值代码转换成对应的高、低电平信号。因此,它是编码的反操作,也称解码器。

分类:• 二进制译码器• 二—十进制译码器• 显示译码器

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

' ' '0 2 1 0 4 4

' '1 2 1 0 5 5

' '2 2 1 0 6 6

3 3 7 7

Y = A A A Y = m

Y = A A A Y = m

Y = A A A Y = m

Y = m Y = m

与逻辑矩阵!

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

' ' ' ' ' ' ' ' ' ' ' ' ' ' ' '7 7 6 6 5 5 4 4 3 3 2 2 1 1 0 0Y = m Y = m Y = m Y = m Y = m Y = m Y = m Y = m

输出逻辑的特点:输出为输入变量的最小项或最小项的非!

输 入 输 出S1 A2 A1 A0

0 X X X X 1 1 1 1 1 1 1 1

X 1 X X X 1 1 1 1 1 1 1 1

1 0 0 0 0 1 1 1 1 1 1 1 0

1 0 0 0 1 1 1 1 1 1 1 0 1

1 0 0 1 0 1 1 1 1 1 0 1 1

1 0 0 1 1 1 1 1 1 0 1 1 1

1 0 1 0 0 1 1 1 0 1 1 1 1

1 0 1 0 1 1 1 0 1 1 1 1 1

1 0 1 1 0 1 0 1 1 1 1 1 1

1 0 1 1 1 0 1 1 1 1 1 1 1

''32 SS ''''''''

01234567 YYYYYYYY

74138 功能表

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

74138 逻辑图

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

Data-sheet( 数据表,包括了逻辑功能和物理特性等内容的描述 )

74LS138 的数据表部分 (1)

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

74LS138 的数据表部分 (2)

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

动态特性 ( 以表格或曲线的方式给出 )

74LS138 的数据表部分 (3)

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

双 2-4 线译码器

74LS138 的数据表部分 (4)

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

译码器功能的扩展:例如,用 74LS138 实现 4—16 线译码器。很明显,要用 2 片 74LS138

原理

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

二、二—十进制译码器功能:将输入的二—十进制码( BCD 码)转换为代表 0-9 这十个数的电平信号。

二—十进制码( Binary Coded Decimal)

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

二—十进制译码器 7442 逻辑图如下( 8421 码):

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

7442 逻辑图

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

三、显示译码器1. 七段字符显示器

这种显示器可用多种发光器件构成。例如半导体发光二极管、液晶等。这里以发光二极管为例进行说明。

半导体数码管 BS201AD 的外形图、等效电路:

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

2. BCD— 七段显示译码器

''''

''''

''

'''''

'''

'''

'''''

)(

)(

)(

)(

)(

)(

)(

012123

0112023

012

012012012

01223

01201213

02130123

AAAAAAY

AAAAAAAY

AAAY

AAAAAAAAAY

AAAAAY

AAAAAAAAY

AAAAAAAAY

g

f

e

d

c

b

a

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

四、译码器的应用-实现组合逻辑电路

例 4.3.3 用 74138 实现下述逻辑函数式描述的组合逻辑电路

原理:①任何逻辑函数都可以表示为最小项之和的形式,或者最小项非的与非形式(与非与非式);②译码器的输出是代码输入变量的全部最小项的非(最小项);③因此如果将函数变量作为译码器的代码输入变量,在输出端加上与非门(或门),就可以用它实现任何逻辑函数。

ABCCBBCAZ

CABBAZ

CBABCZ

CABBCAACZ

''''

''

''

'''

4

3

2

1

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

由于是三变量逻辑函数,故选用

3-8 线译码器

),,,(

),,(

),,(

),,,(

''''

''

''

'''

7420

532

731

6543

4

3

2

1

mABCCBBCAZ

mCABBAZ

mCBABCZ

mCABBCAACZ

'''''

''''

''''

'''''

)(),,,(

)(),,(

)(),,(

)(),,,(

74204

5323

7312

65431

7420

532

731

6543

mmmmmZ

mmmmZ

mmmmZ

mmmmmZ

使能端必须有效

注意变量连接顺序!

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

4.3.3 数据选择器一、数据选择器工作原理

从一组数据输入中选出其中一路输出。也称为多路选择器、多路开关、多路复用器。与之相反的功能电路称为多路分配器。

数据输入

输

出

开关位置由控制信号决定

可称为 4选 1数据选择器

地址输入 A1A0

D0

D1

D2

D3

Y

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

A1 A0 Y

0 0 D0

0 1 D1

1 0 D2

1 1 D3

表达式 :

四选一数据选择器功能表

' ' ' '0 1 0 1 1 0 2 1 0 3 1 0Y = D (A A ) + D (A A ) + D (A A ) + D (A A )

0 0 1 1 2 2 3 3Y = D (m ) + D (m ) + D (m ) + D (m )

见备注

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

S1’ A1 A0 Y1

1 × × 0

0 0 0 D10

0 0 1 D11

0 1 0 D12

0 1 1 D13

74HC153双四选一数据选择器

' ' '1 1 0 1 0 1 1 0

'2 1 0 3 1 0

Y = (S ')'[D (A A ) + D (A A )

+ D (A A ) + D (A A )]

功能表

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

功能扩展

两个 4 选 1数据选择器

1-2线译码器

例 4.3.4 用双 4 选 1 数据选择器构成 8 选 1 数据选择器。

原理和方案二

' ' ' ' ' ' ' '2 1 0 0 2 1 0 1 2 1 0 2 2 1 0 3

' ' ' '2 1 0 4 2 1 0 5 2 1 0 6 2 1 0 7

0 0 1 1 2 2 3 3 4 4 5 5 6 6 7 7

( ) ( ) ( ) ( )

( ) ( ) ( ) ( )

Y A A A D A A A D A A A D A A A D

A A A D A A A D A A A D A A A D

m D m D m D m D m D m D m D m D

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

二、用数据选择器设计组合逻辑电路

根据对应项系数相等 , 函数相等的原则 , 得 : D0=D3=0 , D1=D2=1

也可用真值表: A(A1) B(A0) Z Y

0 0 0 D0

0 1 1 D1

1 0 1 D2

1 1 0 D3

具有 n 个地址输入端的数据选择器,可以实现任一变量数不大于 n+1 的组合逻辑函数!即若干数据输入端只能当作一个变量看待。

' ' ' '

' ' ''1 0 1 0

1 0 1 0 10 1 0

Z = AB + A B = A A + A A

Z = A A + A A 0 + AA A 1 A1+ 0方法一 :

方法二 :

' ' ' '1 0 2 1 0 1 1 0 3 1 0 0Y = A A D + A A D + A A D + A A D

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

例 4.3.5 用 4 选 1 数据选择器实现交通灯判别电路。

R A G Z

0 0 0 1

1 0 0 0

0 1 0 0

1 1 0 1

0 0 1 0

1 0 1 1

0 1 1 1

1 1 1 1

Y

D0

D1

D2

D3

D0=R’, D1=D2=R, D3=1

' ' ' ' ' 'Z = R A G + R AG + RA G + RAG + RAG

' ' ' '1 0 1 0 1 1 0 2 1 0 3 1 0Y = D (A A ) + D (A A ) + D (A A ) + D (A A )

' ' ' ' '= R (A G ) + R(A G) + R(AG ) + 1(AG)

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

4.3.4 加法器

一、 1位加法器-半加器 (Half-Adder)

实现二进制数的加法运算。

1 0 1 1 + 0 1 1 1

1 1 1

1 0 0 1 0

将三个一位二进制数相加,得出和数和进位。2. 一位全加器 (Full-Adder)

输 入

输 出

A B S CO

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

ABCO

BAS

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

输 入

输 出

A B CI S CO

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

'''''''

'''''''

)(

)(

CIACIBBACO

ABCICIABCIBACIBAS

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

二、多位加法器1.串行进位加法器

特点:电路简单,但速度慢

2.超前进位加法器 74283

将各位的 CO 均用输入的 AiBi 表示。

COi=AiBi + (Ai+Bi)CIi CIi = COi-1

COi=AiBi + (Ai+Bi)COi-1

递推下去就可将所有的 COi 和 Si都表示成 Ai 和 Bi 的函数。

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

0

0 0 0 0

0 0 0 0 0 0

1 0

1 1 1 0

1 1 0 0 0 0 0

1 1 1 1 1 0

1 1 1 1 0 0 0 0 0

2 1

1 1 1 1 0 0 0 0

0 : ( ) 0

( )

( ) ( )( )

1: ( ) ( )

( )

( ( )( ) )

( ) ( )( )

( )( ( )( ) )

2 : ( ) ( )

( )( ( )(

i CI

S A B CI

CO A B A B CI

i CI CO

S A B CO

A B A B A B CI

CO A B A B CO

A B A B A B A B CI

i CI CO

A B A B A B A B

0

2 2 2 2 2 2

2 2 2 2 1 1 1 1 0 0 0 0 0

2 2 2 2

2 2 1 1 1 1 0 0 0 0 0

) )

( ) ( )( )

( )( ( )( ( )( ) ))

( )

( ( )( ( )( ) ))

CI

CO A B A B CI

A B A B A B A B A B A B CI

S A B CI

A B A B A B A B A B CI

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

特点:电路复杂;速度快。

4位超前进位加法器 74283 逻辑图

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

三、应用 设计组合电路:用在加(减)算法的场合。

例 4.3.7 将 8421-BCD 码转换为余 3码。分析:只要在 8421 码上加常数 3即可。

加上 3: 0011

输入 8421 码

输出余 3 码

00110123 DCBAYYYY 输 入 输 出D C B A Y3 Y2 Y1 Y0

0 0 0 0 0 0 1 1

0 0 0 1 0 1 0 0

0 0 1 0 0 1 0 1

0 0 1 1 0 1 1 0

0 1 0 0 0 1 1 1

0 1 0 1 1 0 0 0

0 1 1 0 1 0 0 1

0 1 1 1 1 0 1 0

1 0 0 0 1 0 1 1

1 0 0 1 1 1 0 0

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

4.3.5 数值比较器 功能:比较两个二进制数的大小一、 1位数值比较器

')(

')(

'

')(

'

)(),,(

,),(

,),(

BAYBABA

BAYBABABA

ABYABBABA

BA

BA

BA

10

110

101

或同为

则

则

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

二、多位数值比较器— 4位

3 2 1 0

3 2 1 0

A A A A A

B B B B B

3 3 3 3 2 2 3 3 2 2 1 1

3 3 2 2 1 1 0 0

A < B : A < B Α = Β A < B A = B A = B A < B

A = B A = B A = B A < B

或 且 或 且 且或 且 且 且

' ' ' ' ' '( ) 3 3 3 3 2 2 3 3 2 2 1 1

' ' ' '3 3 2 2 1 1 0 0

' ' ' '( ) 3 3 2 2 1 1 0 0

( ) ( ) ( )

( ) ( ) ( )

( ) ( ) ( ) ( )

A B

A B

Y A B A B A B A B A B A B

A B A B A B A B

Y A B A B A B A B

'( ) ( ) ( )( )A B A B A BY Y Y

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

7485每种逻辑都是单独实现的 , I(A>B)

是有意义

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

三、逻辑功能的扩展例 4.3.8 用 7485 构成 8位数值比较器。

显然,需要 2 片 7485 。用片( 1 )比较低 4位;片( 2 )比较高 4位。比较结果由片( 2 )输出。

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

四、比较器的应用

用在其逻辑是变量和变量,或变量和常量比较的场合。比如:实现一个数值比较器逻辑。四舍五入电路,输入 4位二进制数,当其数值大于 4 时输出 1 ,否则输出 0 。

A3A2A1A0

0100

010

A3A2A1A0

B3B2B1B0

Y(A<B)

Y(A=B)

Y(A>B)

7485

Y

I A<BI A=BI A>B

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

尖峰脉冲 或称毛刺(glitch)

tpd

4.4 竞争—冒险现象

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111返回首页

4.4.1 竞争—冒险现象及其成因

定义:门电路的两个输入信号同时 (相近的时间内 )向相反的逻辑电平跳变 (一个由 1 变为 0,另一个由 0 变为 1) 的现象称为竞争。定义:由于竞争在电路输出端可能产生尖峰脉冲的现象叫竞争—冒险。

4.4.2 检查竞争—冒险现象的方法

竞争冒险原因 :信号传输路径的延迟不同和门电路的动态特性的差异。

原则:电路的输入信号变化时,它的两个输入信号同时向相反的逻辑电平跳变,用来判断是否有竞争;有竞争就有可能有冒险,需要避免。现多用计算机仿真来判断。但还是需要实验验证。

有链接

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100

0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110

0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000

0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111 0101 0110 0001 0110

1110 0110 0111 0110 0001 0110 1110 0111 0010 0110 0001 0110 1110 0011 0010

0011 0000 0011 0000 0011 0110 0011 0100 0011 0001 0011 0110 0100 1000 0111

0100 1000 0111 0101 0110 0001 0110 1110 0110 0111 0110 0001 0110 1110 0111

0010 0110 0001 0110 1110 0011 0010 0011 0000 0011 0000 0011 0110 0011 0100